Изобретение относится к автоматике, вычислительной технике и приборостроению и может быть использовано при построении высоконадежных систем с Контролем передаваемой информации.

Известно устройство для мажори тарного выбора сигналов, содержащее компараторы, первый вход каждого из которых соединен с выходом мажоритар яого элемента, второй вход - с соответствующим информационным входом устройства, а выход - с соответствуюсцим входом индикатора, и переключающие элементы, первый и второй вход каждого из которых подключены к второму входу и выходу соответствующего компаратора, а выходы - к входам мажоритарного элемента, а также элементы ИЛИ и блок вьщеления строба, входы которого подключены к информационным и тактовым входам устройства, а выход - к третьим входам кокшараторов, выходы элементов ИЛИ подключены к третьему входу одного переключающего элемента, а входы - к первым входам других переключакхцих элементов Щ .

Недостаток данного устройства значительная задержка формирования сигналов сбоя по отношению к информационным выходным сигналам, что затрудняет организацию тактирования при использовании устройства в автоматизированной системе с программным анализсм сбоя каналов. Кроме того, вследствие формирования специального стробирующего сигнала устройство обладает пониженным быстродействием. Наиболее близким техническим решением к изобретению является мажоритарно-резервированная система, содержащая три резервируемых блока, выходы которых соединены с входами мажоритарных элементов и с входами блоков поразрядной селекции, выходы которых через первые элементы ИЛИ соединены с первыми входами блоков контроля, выходы которых соединены с тремя выходами системы и входами вторых элементов ИЛИ, выходы которых соединены с четьфьмя выходами системы и входом элемента НЕ, выход которого соединен с вторыми входами блоков контроля, третьи входы которых соеди нены с двумя системы 2J. Недостатки этого устройства - его сложность, а также сложность организации тактирования блоков контроля. Формирование сигналов сбоя по прингщпу поразрядной селекции с использованием элементов ИСКЛЮЧАЮиЩЕ ИЛИ делает схему громоздкой при мажоритировании многоразрядных кодов.

Цель изобретения - упрощение и повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для мажоритарного резервирования, содержащее мажоритарньй элемент, входы которого соединены с выходами трех резервируемых блоков, блок сравнения, выходы кото-рого соединены с выходами отказа каналов .устройства, а синхровход соеди-нен с тактовым входом устройства, элементы И и элемент ИЛИ, введены шифратор и две группы ключей, информационные входы первой группы ключей соединены с выходами мажоритарного элемента, выходы - с информационными выходами устройства, а управляющий вход - с тактовым входом устройства и с управлянщим входом второй группы ключей, выходы которой соединены с выходами сбоя каналов устройства, а входы - с выходами шифратора и входами блока сравнения, выходы которого попарно соединены с входами трех элементов И, выходы которых сое динены через элемент ИЛИ с выходом отказа устройства.

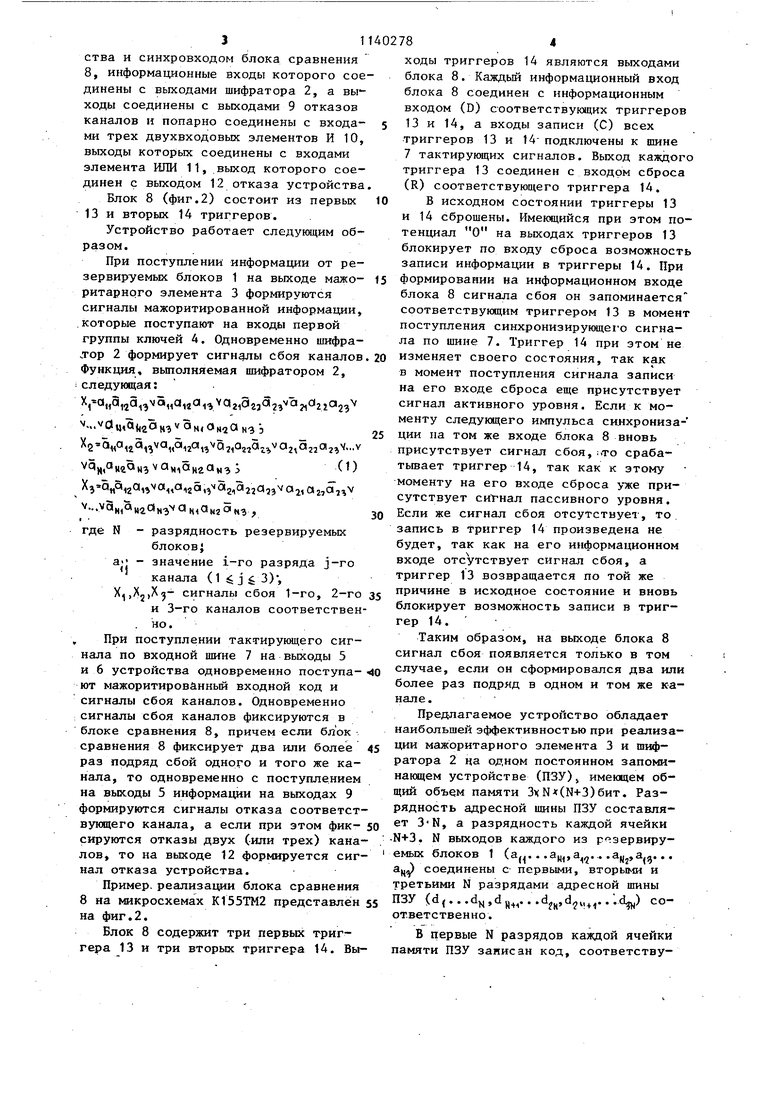

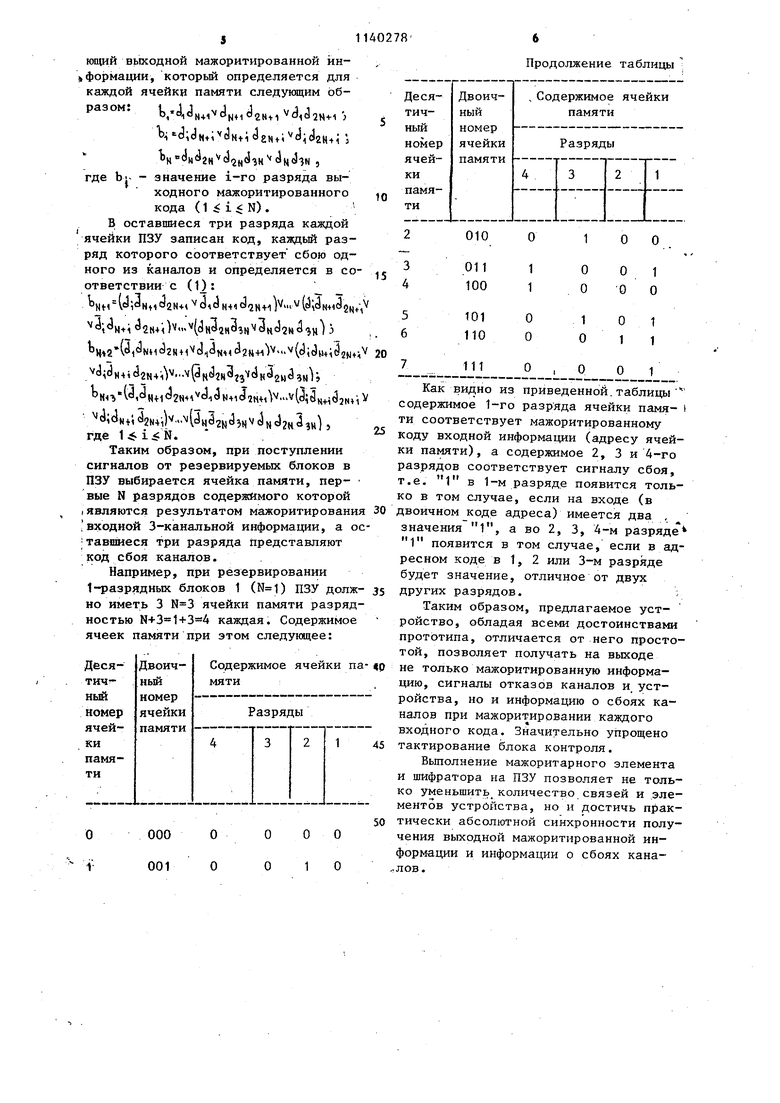

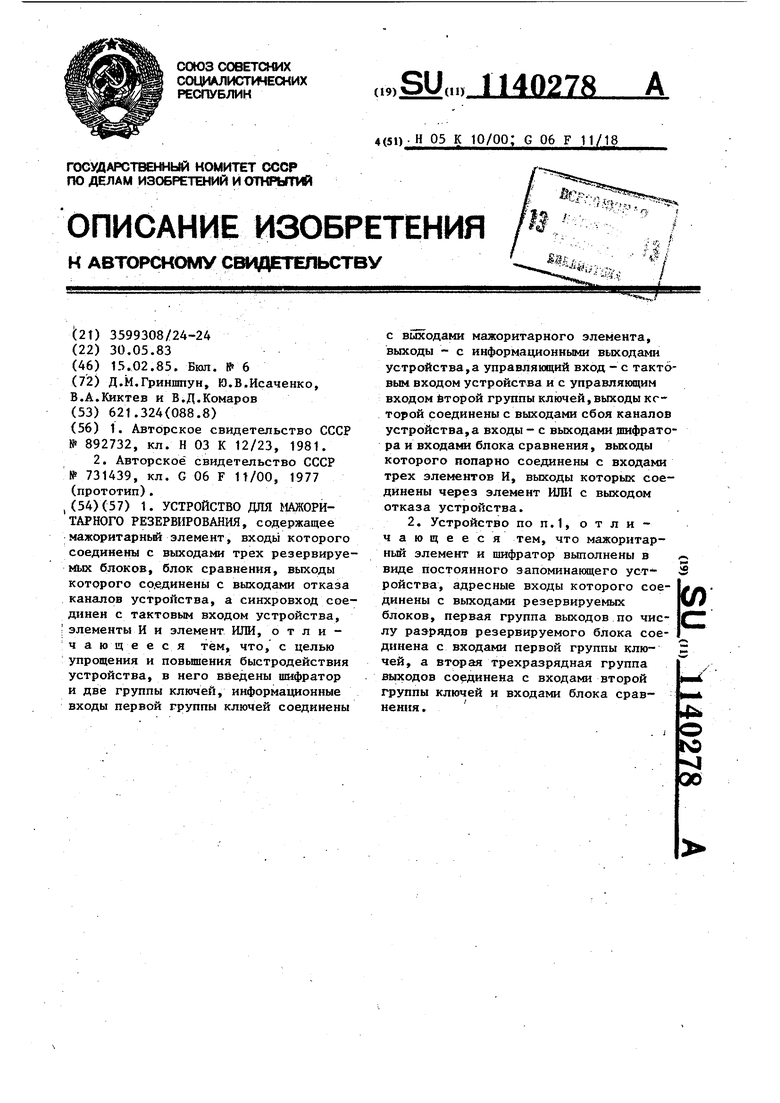

Кроме того, мажоритарный элемент шифратор вьтолнены в виде постоянного запоминающего устройства, адресные входы которого соединены с выходами резервируемых блоков, первая группа выходов по числу разрядов резервируемого блока соединена с входами первой группы ключей, а вторая трехразрядная группа выходов соединена с входами второй группы ключей и входами блока сравнения. На фиг.1 представлена блок-схема мажоритарно-резервированного устройства на фиг.2 - схема блока сравнения. Устройство содержит резервируемые блоки 1, выходы которых соединены с входами шифратора 2 и мажоритарного элемента 3, выходы которых соединены соответственно с информационными входами первой и второй групп ключей 4, выходи которых соединены с выходами .5 информации и 6 сигналов сбоя каналов устройства, а управляющие входы соединены с тактовым входом 7 устройства и синхровходом блока сравнения 8, информационные входы которого сое динены с выходами шифратора 2, а выходы соединены с выходами 9 отказов каналов и попарно соединены с входами трех двухвходовых элементов И 10, выходы которых соединены с входами элемента ИЛИ 11, выход которого соединен с выходом 12 отказа устройства Блок В (фиг.2) состоит из первых 13 и вторых 14 триггеров. Устройство работает следукндим образом. При поступлении информации от резервируемых блоков 1 на выходе мажоритарного элемента 3 формируются сигналы мажоритированной информации, которые поступают на входы первой группы ключей 4. Одновременно шифра.тор 2 формирует сигналы сбоя каналов Функция, выполняемая шифратором 2, следующая: X,-a,,a,2a,,v5,,a«ai,jVqj,a23a,va d2ja2,v ...анЗйеанэON Он а N3 э ,,a,ja,,va,,,,vQj,aj,a-,,va2 ajja2,v,.,v vq,aHjaH3vaH,aK2aN3S ) X3a oii2a««n°ija,,oi2n 22a«c ai oti,cr,,v «а„,а„2а„з ач,амга„, , где N - разрядность резервируемых блоков а- - значение i-ro разряда j-ro канала (), X, . сигналы сбоя 1-го, 2-го и 3-го каналов соответствен . но. При поступлении тактирующего сигнала по входной шине 7 на выходы 5 и 6 устройства одновременно поступают мажоритированный входной код и сигналы сбоя каналов. Одновременно сигналы сбоя каналов фиксируются в блоке сравнения В, причем если блок сравнения В фиксирует два или более раз подряд сбой одного и того же канала, то одновременно с поступлением на выходы 5 информации на выходах 9 формируются сигналы отказа соответст вующего канала, а если при этом фиксируются отказы двух (или трех) кана лов, то на выходе 12 формируется сиг нал отказа устройства. Пример, реализации блока сравнения В на микросхемах К155ТМ2 представлен

на фиг.2.

Блок 8 содержит три первых триггера 13 и три вторых триггера 14. Выответственно.

В первые N разрядов каждой ячейки памяти ПЗУ записан код, соответству- ходы триггеров 14 являются выходами блока 8. Каждый информационный вход блока В соединен с информационным входом (D) соответствующих триггеров 13 и 14, а входы записи (С) всех триггеров 13 и 14 подключены к шине 7 тактирукщих сигналов. Выход каждого триггера 13 соединен с входом сброса (R) соответствующего триггера 14. В исходном состоянии триггеры 13 и 14 сброшены. Имеющийся при этом потенциал О на выходах триггеров 13 блокирует по входу сброса возможность записи информации в триггеры 14. При формировании на информационном входе блока 8 сигнала сбоя он запоминается соответствующим триггером 13 в момент поступления синхронизирующего сигнала по шине 7. Триггер 14 при этом не изменяет своего состояния, так как в момент поступления сигнала записи на его входе сброса еще присутствует сигнал активного уровня. Если к моменту следующего импульса синхронизации па том же входе блока В вновь присутствует сигнал сбоя, :.то срабатывает триггер 14, так как к этому моменту на его входе сброса уже присутствует ситнал пассивного уровня. Если же сигнал сбоя отсутствует, то запись в триггер 14 произведена не будет, так как на его информационном входе отсутствует сигнал сбоя, а триггер 13 возвращается по той же причине в исходное состояние и вновь блокирует возможность записи в триггер 14. Таким образом, на выходе блока В сигнал сбоя появляется только в том случае, если он сформировался два или более раз подряд в одном и том же канале. Предлагаемое устройство обладает наибольшей эффективностью при реализации мажоритарного элемента 3 и шифратора 2 на одном постоянном запоминающем устройстве (n3y)j имеющем общий объем памяти ЗxN«(N+3)бит. Разрядность адресной шины ПЗУ составля -N, а разрядность каждой ячейки N+3. N выходов каждого из р.зервируемых блоков 1 (а,. .а,а,., .,., ац соединены с- первыми, вторыми и третьими N разрядами адресной шины ( Н-и ° ющий вькодной мажоритированной йниформации, которьй определяется для каждой ячейки памяти следукнцим обb,o,((+n ii3aN-n J b t idN+i i Nt; Згм ; ;с1гк- Г; (2H 32Nc53M iM 3N , где b- значение i-ro разряда выходного мажоритированного кода (1 i N) . В оставшиеся три разряда каждой ячейки ПЗУ записан код, каждый разряд которого соответствует сбою одного из каналов и определяется в со ответствии с (ОЦмЧ 1ани 2Н+и5,м+1 7Н+1К(|3;5м4Л8ц 32н40 Ч 5нЗгнЗ м Знс52м5 н) - (1 NH 2NH c iJN44(i2H+l)((3n4;32Ni ...-vpN(32H3j5(iHl2H 5MH Ькп1 1« НИ 2НМ 1 Н41(.(3;5н+ 3 I r.OlOn+iCl2N ( mib-H M K JnV (3 )} где :N. Таким образом, при поступлении сигналов от резервируемых блоков в ПЗУ выбирается ячейка памяти, первые N разрядов содержимого которой (ЯВЛЯЮТСЯ результатом мажоритировани Iвходной 3-канальной информации, а о тавошеся три разряда представляют код сбоя каналов. Например, при резервировании -разрядных блоков 1 () ПЗУ долж но иметь 3 ячейки памяти разряд ностью N+3 1+3-4 каждая. Содержимое ячеек памяти при этом следующее: Продолжение таблицы Как видно из приведенной.таблицы содержимое 1-го разряда ячейки памя- t ти соответствует мажоритированному коду входной информации (адресу ячейки памяти), а содержимое 2, 3 и 4-го разрядов соответствует сигналу сбоя, т.е. 1 в 1-м разряде появится только в том случае, если на входе (в двоичном коде адреса) имеется два 1, а во 2, 3, 4-м разряде значения появится в том случае, если в адресном коде в 1, 2 или 3-м разряде будет значение, отличное от двух других разрядов.: Таким образом, предлагаемое устройство, обладая всеми достоинствами прототипа, отличается от него простотой, позволяет получать на выходе не только мажоритированную информацию, сигналы отказов каналов и. устройства, но и информацию о сбоях каналов при мажоритировании каждого входного кода. Значительно упрощено тактирование блока контроля. Вьтолнение мажоритарного элемента и шифратора на ПЗУ позволяет не только уменьшить количестзо.связей и элементов устройства, но и достичь практически абсолютной синхронности получения выходной мажоритированной информации и информации о сбоях каналов.

5 7 /2 Л А 4

/(

//

///

6 6 6

5

А А / -t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Мажоритарное устройство | 1984 |

|

SU1399905A1 |

| Устройство для управления реконфигурацией резервированной системы | 1982 |

|

SU1040632A1 |

| Адаптивное резервированное устройство | 1983 |

|

SU1174929A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

| Дешифратор с коррекцией ошибок | 1981 |

|

SU1012262A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

1. УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО РЕЗЕРВИРОВАНИЯ, содержащее мажоритарньй элемент, входы которого соединены с выходами трех резервируемых блоков, блок сравнения, выходы которого со.единены с выходами отказа каналов устройства, а синхровход соединен с тактовым входом устройства, элементы И и элемент ИЛИ, о т л и ч а ю щ е е с я тем, что, с целью упрощения и повьшения быстродействия устройства, в него введены шифратор и две группы ключей, информационные входы первой группы ключей соединены с выходами мажоритарного элемента, выходы - с информационными выходами устройства,а управляющий вход - с тактовым входом устройства и с управляющим входом йторой группы ключей, выходы К(- торой соединены с выходами сбоя каналов устройства, а входы - с выходами дшфратора и входами блока сравнения, выходы которого попарно соединены с входами трех элементов И, выходы которых соединены через элемент ИЛИ с выходом отказа устройства. 2. Устройство по П.1, отличающееся тем, что мажоритарный элемент и шифратор выполнены в виде постоянного эапоминанндего ус-тройства, адресные входы которого сое(Л динены с выходами резервируемых блоков, первая группа выходов по числу разрядов резервируемого блока соединена с входами первой группы ключей, а вторая трехразрядная группа выходов сочинена с входами второй группы ключей и входами блока сравнения.

TV

Г

8

ч v Г

гпп

i/г/

CM

I

5

Фие.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Мажоритарное устройство | 1980 |

|

SU892732A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Мажоритарно-резервированная система | 1977 |

|

SU731439A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , | |||

Авторы

Даты

1985-02-15—Публикация

1983-05-30—Подача