. Изобретение относится к электросвя зи и может быть использовано в системах с фазовым пуском, а также в системах передачи данных, использующих для синхронизации рекуррентный сигнал По основному авт.св. № 628630 известен анализатор рекуррентного сигнала фазового пуска, содержащий объединенные по информационному входу пер вый блок сравнения и коммутатор, к вторым входам которых подключен выход первого блока сумматоров по модулю два, к входам которого подключены выходы соответствукицих регистра сдвига, другие выходы соответству ющих выходов которого подключены через элемент запрета к первому входу элемента ИЛИ, к второму входу которого подключен выход первого блока сраа нения, а выход элемента ИЛИ через пос ледовательно соединенные счетчик, . блок памяти и коммутатор подключен к входу регистра сдвига, а также последовательно соединенные датчик времени и анализатор ошибок, при этом выход блока памяти подключен к датчику времени и к второму входу анализатора ошибок, к третьему входу которого подключен выход элемента ИЛИ,а выход анализатора ошибок подключен к соответствукяце.му входу блока памяти, причем на соответствукмдие вхо;. разрядов регистра сдвига элемента запрета и счетчика поданы тактовые импульсы, а на соответствующие входы блока памяти и счетчика поданы импульсы Исходное состояние 1 , Одн.ако известный анализатор характеризуется большим временем выявления рекуррентного сигнала при искажении этого сигнала в канале связи. Цель изобретения - сокращение времени анализа рекуррентного сигнала при наличии помех путем исправления ошибок. Для достижейия указанной цели ванализатор рекуррентного сигнала фазового пуска введены последовательно соединенные второй регистр сдвига, второй блок сумматоров по модулю два/ второй блок сравнения, блок мажоритар ного анализа и блок исправления ошибок, причем второй вход второго блока сравнения объединен с информационным входом второго регистра сдвига, соответствукяций выход которого подключен к второму входу блока исправления ошибок, выход которого подключен к объединенным входам коммутатора и первого блока сравнения. .

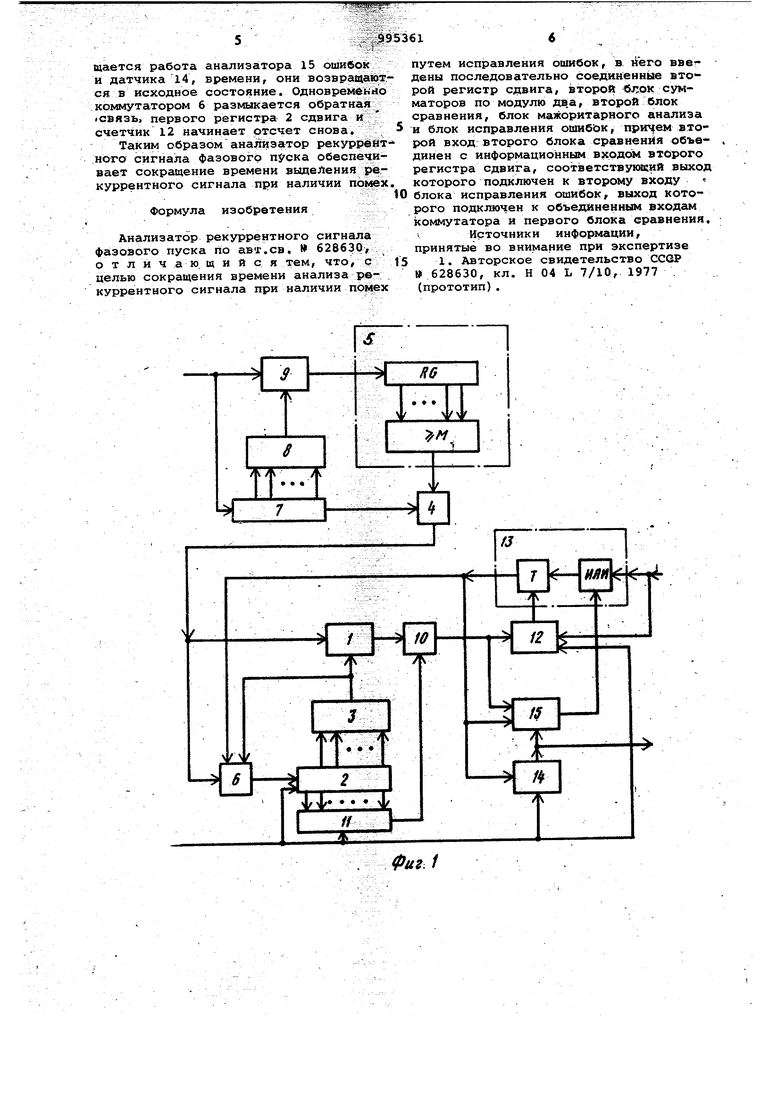

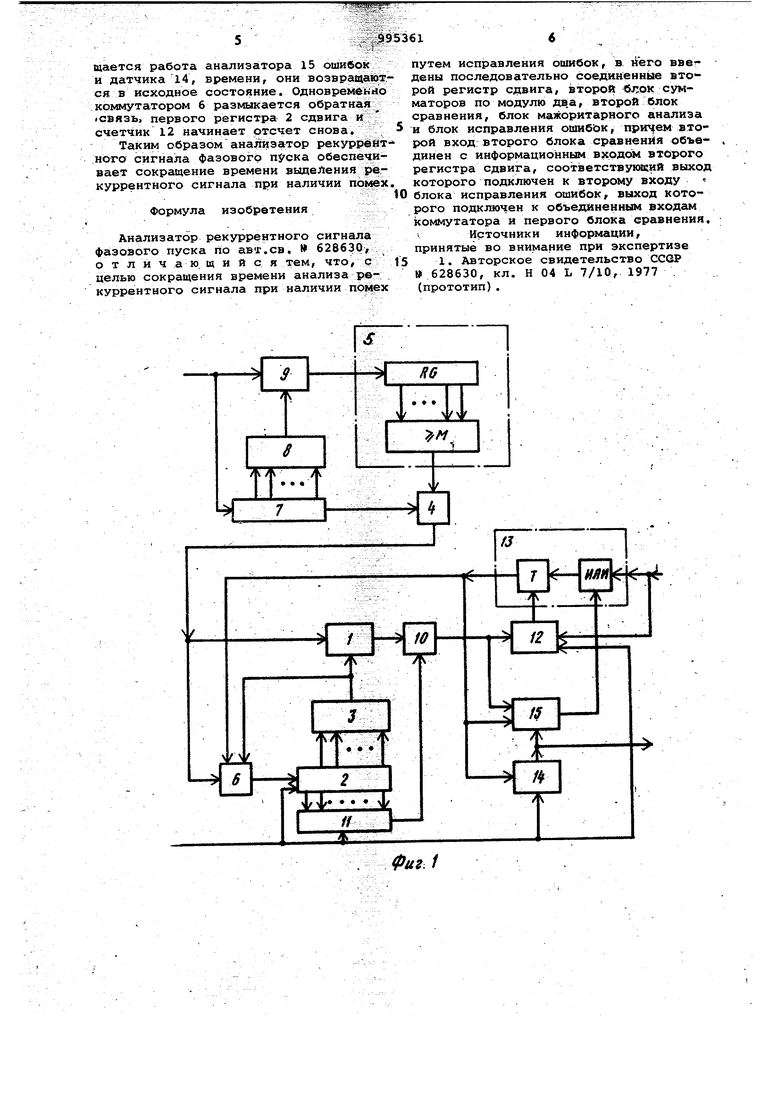

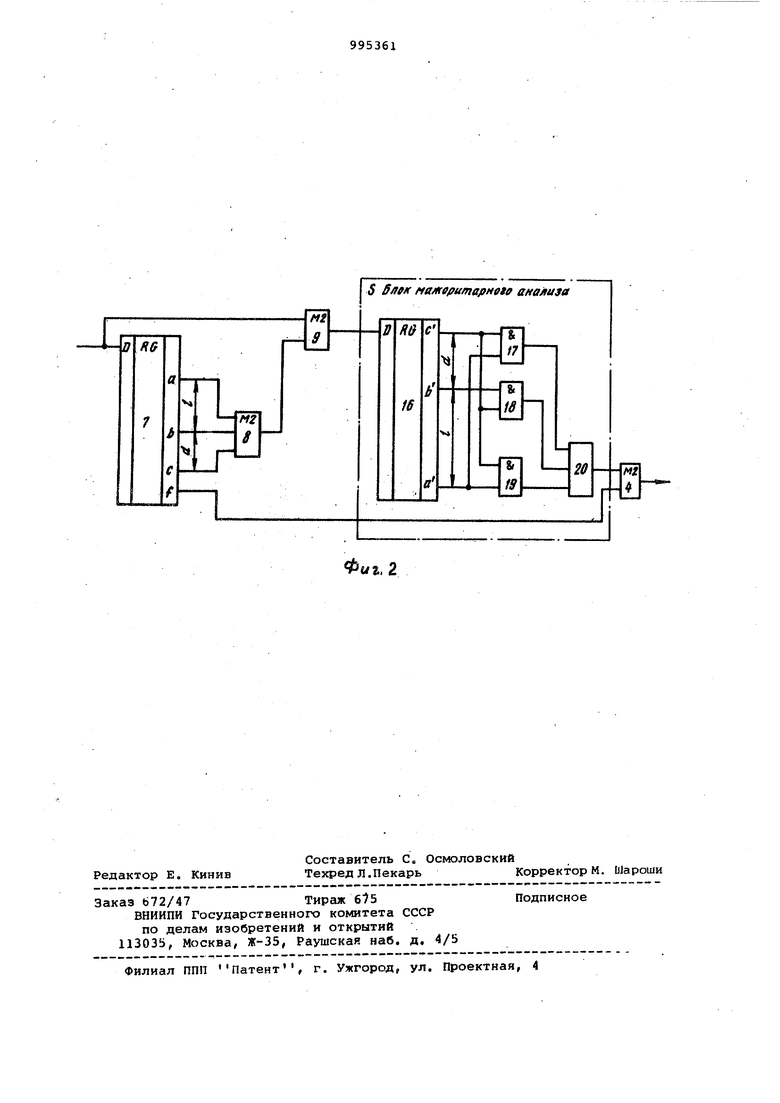

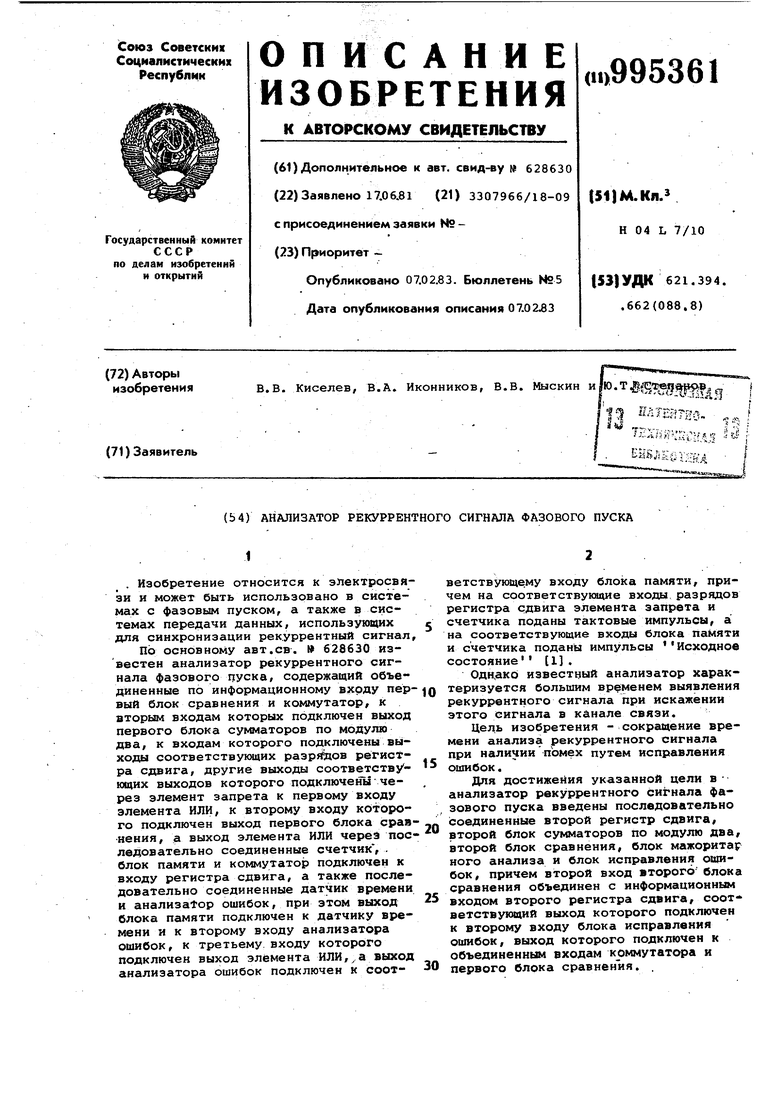

На фиг. 1 приведена структурная электрическая схема анализатора; на фиг. 2 - принцип анализа и исправления искаженных знаков с помощью введенных в анализатор блоков.

Анализатор рекуррентного сигнала фазового пуска содержит первый блок 1 сравнения, первый регистр 2 сдвига, первый; блок 3 сумматоров по модулю два,блок 4 исправления ошибок, блок 5 мажоритарного анализа, коммутатор 6, второй регистр 7 сдвига, второй блок 8 сумматоров по модулю два, второй блок 9 сравнения, элемент , элемент 11 запрета, счетчик 12, блок 13 памяти, датчик 14 времени анализатор 15 ошибок, блок 5 можоритарного анализа содержит, регистр сдвига 16, элементы И 17, 18 и 19, элемент ИЛИ 20.

Анализатор рекуррентного сигнала фазового пуска работает следующим образом.

На блок 13 памяти и счетчик 12 поступает импульс, устанавливающий их в исходное состояние. В исходном состоянии первый регистр 2 сдвига через коммутатор 6, управляемый б локрм 13 памяти, подключается к выходу блока 4 исправления ошибок.

Сигнал принимаемый по информационному входу, одновременно поступает на второй блок 9 сравнения и на второй регистр 7 сдвига. Второй блок 8 сумматоров по модулю два формирует последовательность импульсов , с которой во втором блоке 9 сравнения сравнивается принятый по информационному вхо.ду сигнал .

Полученные знаки сравнения поступают последовательно в блок 5 мажоритарного анализа.

При прохождении искаженного сигнала рекуррентной последовательности по второму регистру 7 сдвига, на выходе второго блока 9 сравнения (сумматора) появляются знаки несовпадения в моменты прохождения искаженным знаком точек съема. Эти знаки несовпадения зафиксируются на регистре блока 5 мажоритарного анализа в виде трека ошибок. В момент, когда искажённый знак передвинется с последней точки съема в следукиций разряд (точка ha фиг. 2), трек ошибок займет положение на регистре 16 блока 5 мажоритарного анализа, соответствующее точ- кам съема на этом регистре. При наличии в точках а, Ъ, с не менее двух . знаков несовпадения, с выхода блока 5 мажоритарного анализа поступает на вход блока 4 исправления ошибок (сумматора) сигнал исправления знака, поступающего на второй вход блока 4 из второго регистра 7 сдвига. С выхода блока. 4 исправления ошибок реку ррентная последовательность поступает

на объединенные входы коммутатора б и первого блока 1 сравнения.

Анализатор рекуррентного сигнала фазового пуска способен исправлять не только одиночные но и групповые ошибки, при этом длина пакета ошибок для рассмотренного примера не должна превышать расстояние е( расстояние ме ;;ду точками съема « и Ъ фиг. 2). Иначе при прохождении пакета по второму регистру 7 сдвига несовпадение регистрируется лишь при попадении искаженного fзнака на первую тогку съема а . При Достижении искаженным знаком точки Ъ, на d тоже искаженный знак. В разультате несовпадение может не зарегйс1гри-роваться. То же произойдет .при достижении искаженным,знаком точки с.

В треке ошибок только един знак несовпадения и сигнал испразления не формируется.

С блока 4 исправления ошибок рекуррентная последовательность через коммутатор 6 поступает в первый регистр 2 сдвига. Первый блок 3 сумматоров по модулю два по информации, записываемой в первый регистр 2 сдвига, формирует последовательность импульсов, с которой в первом блоке 1 сравнения сравнивается сигнал, приходящий с выхода блока 4 исправления ошибок.

Счетчик 12 начинает счет. При отсутствии сигнала на выходе второго регистра 7 сдвига срабатывает элемент запрета 11 и через элемент ИЛИ 10 возвращает счетчик 12 к началу счета.

При наличии заданного числа совпадений счетчик 12 формирует на своем. выходе импульс, опрокидывающий блок 13 памяти, который при помощи коммутатора 6 замыкает обратную связь первого регистра 2 сдвига, проходящую через второй блок 8, сумматоров по модулю два. Одновременно блок 13 памяти разрешает работу анализатора 15 ошибок и датчика 14 времени. С замыканием обратной связи первого регистра 2 сдвига на выходе первого блока 3 сумматоров по модулю два начинается ав.тономное формирование опорной последовательности. В то же врекГя анализатор 15 ошибок начинает подсчет несовпадающих символов , выявленных первым блоком 1 сравнения, а датчик 14 времени начинает отсчет времени. Если за время, определяемое датчиком 14 времени, число несовпадающих символов не превышает порог, анализатора 15 ошибок, то датчик 14 времени вырабатывает импульс, запрещающий работу анализатора 15 ошибок и поступающий на вход анализатора рекуррентного сигнала. Если до срабатывания датчика 14 времени анализатор 15 ошибок выявляет превышение допустимого порога ошибок количеством несовпадающих символов, то блок 13 памяти сразу возвращается в исходное состояние. Тем самым запрещается работа анализатора 15 ошибок и датчика 14, времени, они возвращают ся в исходное состояние. Одноврем нсю кo 1мyтaтopoм 6 размыкается обратная связь первого регистра 2 сдвига и счетчик 12 начинает отсчет снова, Таким образом анализатор рекуррент ного сигнала фазового nSrcKa обеспечивает сокращение времени выделения рекуррентного сигнала при наличии помех Формула изобретения Анализатор рекуррентного сигнала фазового пуска по авт.св. W 628630, о т л и ч а ю щ и и с я тем, что, с целью сокращения времени анализа рекуррентного сигнала при наличии помех путем исправления ошибок, в йего вве дены последовательно соединенные второй регистр сдвига, второй блок сумматоров по модулю дв.а, второй блок сравнения, блок мажоритарного анализа и блок исправления ошибок, примем второй вход второго блока сравнения объединен с информационным входом второго регистра сдвига, соотззетствукнсий выход которого подключен к второму входу блока исправления ошибок, выход которого подключен к объединенным входам коммутатора и первого блока сравнения, i Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №628630, кл, Н 04 L 7/10, 1977 . (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выделения рекуррентного сигнала с обнаружением ошибок | 1986 |

|

SU1327308A2 |

| Устройство для выделения рекуррентного синхросигнала | 1978 |

|

SU758549A2 |

| Устройство для выделения рекуррентного синхросигнала | 1983 |

|

SU1116547A1 |

| Устройство фазового пуска | 1979 |

|

SU866773A1 |

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1983 |

|

SU1102050A2 |

| Устройство цикловой синхронизации | 1981 |

|

SU944137A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ПО ЦИКЛАМ | 1970 |

|

SU275106A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Устройство для выделения рекуррентныхСигНАлОВ фАзОВОгО пуСКА B МНОгОКАНАльНыХ СиСТЕМАХ СВязи | 1979 |

|

SU849519A2 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

Фиг. 1

iTl-

20

r-iLT

Фиг,2

Авторы

Даты

1983-02-07—Публикация

1981-06-17—Подача