Изобретение относится к электронной технике, преимущественно к изготовлению полупроводниковых схем памяти на МДП-транзисторах.

Целью изобретения является увеличение эффективной поверхности обкладки за счет развития ее рельефа.

В предлагаемом изобретении после формирования в нанесенном слое рисунка обкладки на поверхность пластины наносят разделительный диэлектрический слой, затем безмасочным анизотропным плазменным травлением удаляют участки этого слоя с горизонтальных поверхностей пластины.

При нанесении разделительного диэлектрического слоя на ступенчатую поверхность, толщины слоя диэлектрика по вертикали, у стенки углубления больше чем на горизонтальной поверхности. Так как при безмасочном анизотропном плазменном травлении поток ионов направлен перпендикулярно поверхности пластины, то при удалении разделительного слоя с горизонтальных областей пластины, у стенок углубления остаются неудаленными участки разделительного диэлектрического слоя.

Последующее нанесение на полученную профилированную поверхность дополнительного проводящего слоя и безмасочное анизотропное плазменное удаление этого слоя с горизонтальных поверхностей пластины позволяет сформировать на поверхности обкладки конденсатора выступ из проводящего материала, имеющие электрический контакт с обкладкой. Удаление избирательным травлением оставшихся пристеночных участков разделительного диэлектрического слоя полностью обнажает рельефную поверхность обкладки конденсатора, образованную выступами, оставшимися на поверхности пластины после безмасочного анизотропного плазменного удаления с горизонтальных поверхностей дополнительного проводящего слоя.

Таким образом, в предлагаемом изобретении удается сформировать трехмерную рельефную развитую поверхность, что позволяет увеличить эффективную площадь поверхности обкладки без увеличения ее размеров в плане или уменьшить ее размеры в плане без уменьшения эффективной площади обкладки, повысить плотность упаковки элементов на кристалле, уменьшить стоимость кристалла ИС.

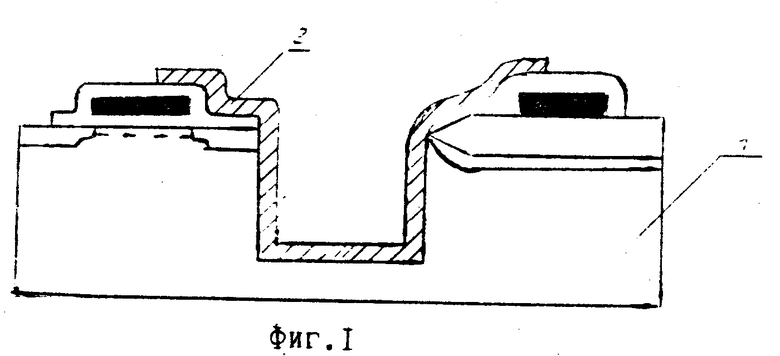

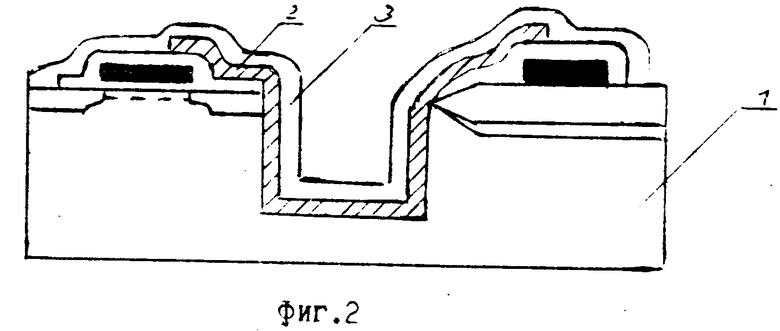

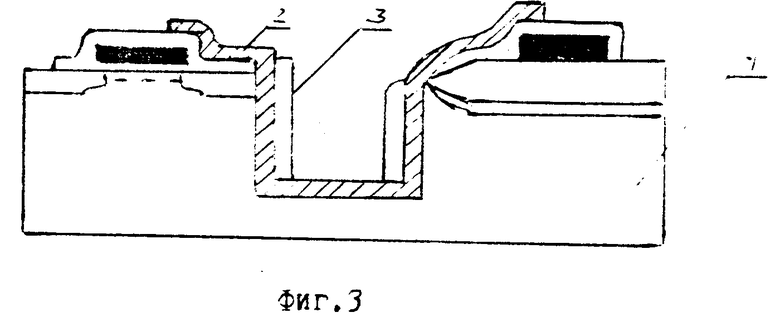

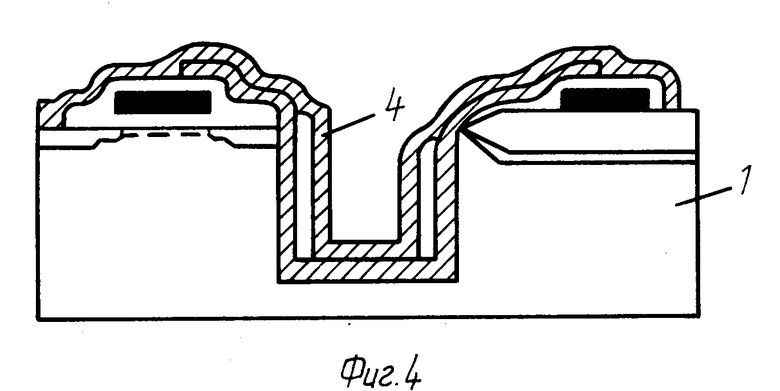

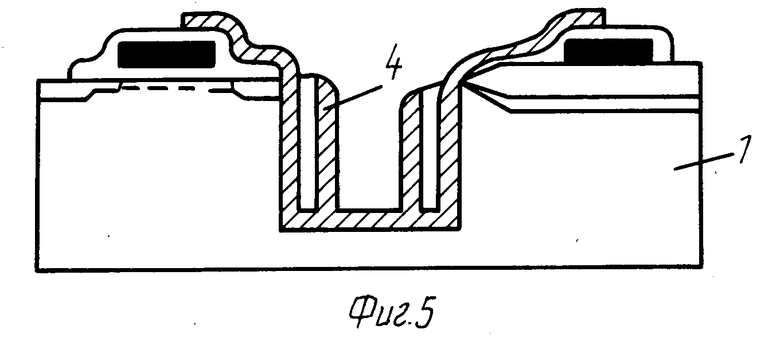

На фиг. 1 изображена полупроводниковая пластина 1 со сформированным на ней углублением с вертикальными стенками после нанесения проводящего слоя 2 и формирования в нанесенном слое рисунка обкладки конденсатора; на фиг.2 - полупроводниковая пластина 1 после нанесения разделительного диэлектрического слоя; на фиг.3 то же после удаления безмасочным анизотропным плазменным травлением участков диэлектрического слоя с горизонтальных поверхностей пластины; на фиг.4 то же после нанесения дополнительного проводящего слоя 4; на фиг. 5 то же после удаления безмасочным анизотропным плазменным травлением участков дополнительного проводящего слоя с горизонтальных поверхностей пластины; на фиг. 6 то же после удаления избирательным травлением оставшихся пристеночных участков разделительного диэлектрического слоя.

П р и м е р. На полупроводниковую пластину 1 КДБ 12 со сформированным на ней углублением 2 х 2 мкм, глубиной 2 мкм, угол наклона стенок относительно поверхности 87 90o, методом LPCVD нанесли проводящий слой 2 из легированного в процессе роста фосфором поликристаллического кремния толщиной 0,1 ± 0,01 мкм и методом проекционной фотолитографии на установке ЭМ-584А сформировали в нанесенном слое обкладки конденсатора площадью 200 мкм2. После этого на поверхность полупроводниковой пластины нанесли разделительный диэлектрический слой 3 (фиг.2) из фосфоро-силикатного стекла толщиной 0,6 мкм и содержанием фосфора 3-4% полученный пиролизом тетроэтоксисилана при температуре 750oС. Затем безмасочным анизотропным плазменным травлением на установке Лада-35 в газовой смеси C3F8 + CHF3 + O2 + He в соотношении (8-11) (13-15) (1,8 2,5) (70 78) при рабочем давлении 130 ± 5 Па и мощности, вкладываемой в разряд 200 230 Вт, удалили участки диэлектрического слоя с горизонтальных поверхностей пластины (фиг.3). После этого на поверхность пластины нанесли дополнительный проводящий слой 4 (фиг.4), легированного в процессе роста фосфором поликристаллического кремния. Режим нанесения идентичен режимам нанесения слоя поликристаллического кремния для обкладки. Безмасочным анизотропным реактивно-ионным травлением слоя поликристаллического кремния на установке Лада-35 в смеси SF6 + (30-36)% O2 при рабочем давлении 6-9 Па и мощности, вкладываемой в разряд 70,0-90,0 Вт, удалили дополнительный проводящий слой с горизонтальных поверхностей пластины (фиг.5). Затем избирательным травлением в травителе, состоящем из HF:NH4F:H2O 108 мл:428 г:(до 1 л), удалили оставшиеся пристеночные участки разделительного диэлектрического слоя (фиг.6).

Так как емкость конденсатора пропорциональна площади обкладки, то эффективность предлагаемого изобретения оценили по увеличению емкости накопительного конденсатора элемента памяти БИС.

При одинаковой площади конденсатора в плане (4 мкм2) емкость конденсатора, обкладка которого была изготовлена в соответствии с предлагаемым изобретением, увеличилась в 1,8 раза по сравнению с емкостью конденсатора, обкладка которого была изготовлена по известному способу прототипу.

При использовании в качестве конденсаторного диэлектрика Si3N4 толщиной 275 А удельная емкость составляет ≈ 1,9-2,0 Ф/мкм2. Таким образом, для площади обкладки 20 мкм2 емкость накопительного конденсатора составит 38-40 Ф для способа-прототипа и 68-72 Ф для предлагаемого способа.

Использование предлагаемого изобретения позволяет в 1,8 раза повысить эффективную (рабочую) площадь конденсатора без увеличения площади обкладки на поверхности пластины, увеличить плотность упаковки элементов, снизить стоимость кристалла, повысить устойчивость микросхем к случайным сбоям над воздействием α-частиц или других видов излучений.

Дополнительным преимуществом предлагаемого изобретения является уменьшение рельефности поверхности полупроводниковой пластины.

Накопительный конденсатор со сформированной по предлагаемому изобретению обкладкой легко встраивается в типовой техпроцесс и элемент памяти ДОЗУ с канавочным конденсатором.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ОБКЛАДКИ КОНДЕНСАТОРА ИЗ ПОЛИКРИСТАЛЛИЧЕСКОГО КРЕМНИЯ | 1991 |

|

SU1829776A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ НАКОПИТЕЛЬНОГО КОНДЕНСАТОРА ЭЛЕМЕНТА ПАМЯТИ ИНТЕГРАЛЬНЫХ СХЕМ | 1990 |

|

RU2110870C1 |

| НАКОПИТЕЛЬНЫЙ КОНДЕНСАТОР ЭЛЕМЕНТА ПАМЯТИ ИНТЕГРАЛЬНЫХ СХЕМ | 1991 |

|

RU2030813C1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2018994C1 |

| СУПЕРКОНДЕНСАТОР НА ОСНОВЕ КМОП-ТЕХНОЛОГИИ | 2016 |

|

RU2629364C1 |

| Способ изготовления МИМ-конденсатора | 2023 |

|

RU2817385C1 |

| ВЕРТИКАЛЬНЫЙ МДП-ТРАНЗИСТОР ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2108641C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО УСТРОЙСТВА | 1997 |

|

RU2176423C2 |

| Способ изготовления элемента однократно программируемой памяти | 2024 |

|

RU2834207C1 |

| СХЕМНАЯ СТРУКТУРА С ПО МЕНЬШЕЙ МЕРЕ ОДНИМ КОНДЕНСАТОРОМ И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ | 1992 |

|

RU2082258C1 |

Использование: микроэлектроника, изготовление полупроводниковых схем памяти на МДП-транзисторах. Цель - повышение качества конденсатора за счет увеличения эффективной площади поверхности обкладки без увеличения ее размеров в плане. Сущность изобретения: при изготовлении обкладки накопительного конденсатора элемента памяти интегральных схем на поверхность полупроводниковой пластины со сформированным на ней углублением с вертикальными стенками наносят проводящий слой, формируют в нанесенном слое рисунок обкладки конденсатора, наносят разделительный диэлектрический слой, безмасочным анизотропным плазменным травлением удаляют участки этого слоя с горизонтальных поверхностей пластины, затем на полученную профилированную поверхность пластины наносят дополнительный проводящий слой, безмасочным анизотропным плазменным травлением удаляют участки этого слоя с горизонтальных поверхностей пластин, затем избирательным травлением удаляют оставшиеся пристеночные участки разделительного диэлектрического слоя. 6 ил.

Способ изготовления обкладки накопительного конденсатора элемента памяти интегральных схем, включающий нанесение на поверхность полупроводниковой пластины со сформированным на ней углублением с вертикальными стенками проводящего слоя, формирование в нанесенном слое рисунка обкладки конденсатора, отличающийся тем, что, с целью увеличения эффективной поверхности обкладки за счет развития ее рельефа, после формирования в проводящем слое рисунка обкладки на поверхность пластины наносят разделительный диэлектрический слой, безмасочным анизотропным плазменным травлением удаляют участки этого слоя с горизонтальных поверхностей пластины, затем на полученную профилированную поверхность пластины наносят дополнительный проводящий слой, безмасочным анизотропным плазменным травлением удаляют участки этого слоя с горизонтальных поверхностей пластины, затем избирательным травлением удаляют оставшиеся пристеночные участки разделительного диэлектрического слоя.

| Черняев В.Н | |||

| Технология производства интегральных схем и микропроцессоров | |||

| -М.: Радио и связь, 1987, с | |||

| Поливное приспособление для паровозов | 1922 |

|

SU390A1 |

| K.H | |||

| Kusters et al | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Способ размножения копий рисунков, текста и т.п. | 1921 |

|

SU89A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Solid State Device Res | |||

| Conf | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

| ВОДЯНОЕ КОЛЕСО | 1923 |

|

SU907A1 |

Авторы

Даты

1996-10-10—Публикация

1991-06-24—Подача