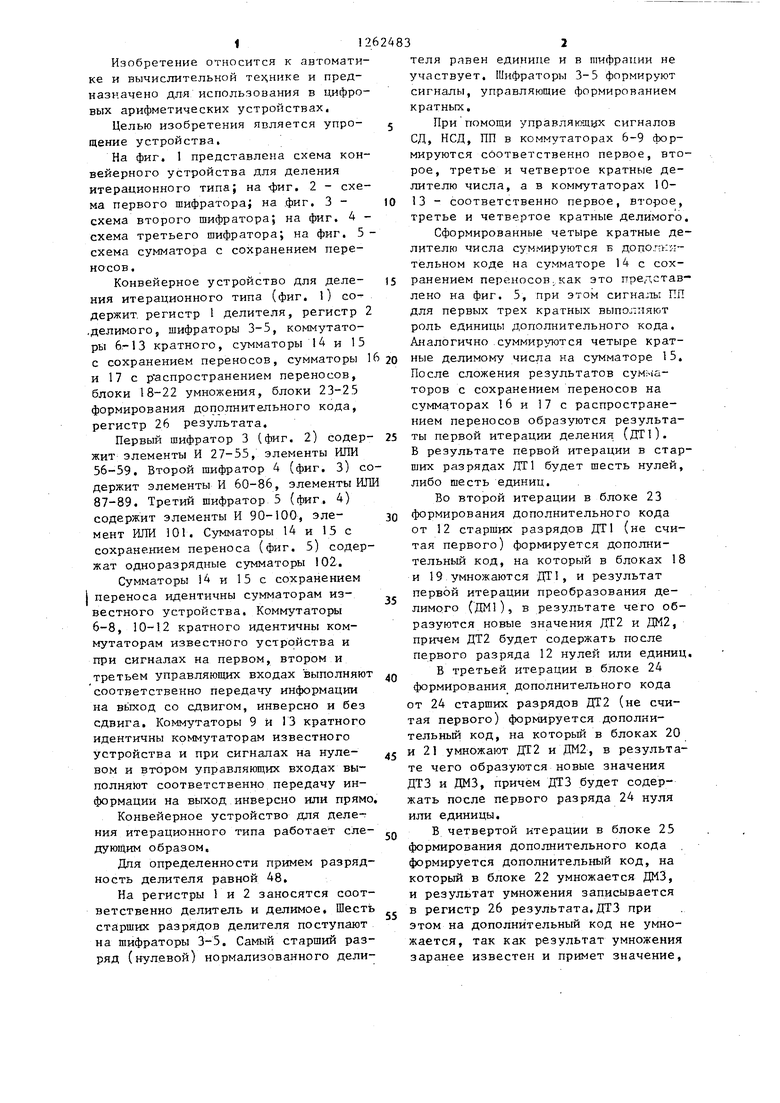

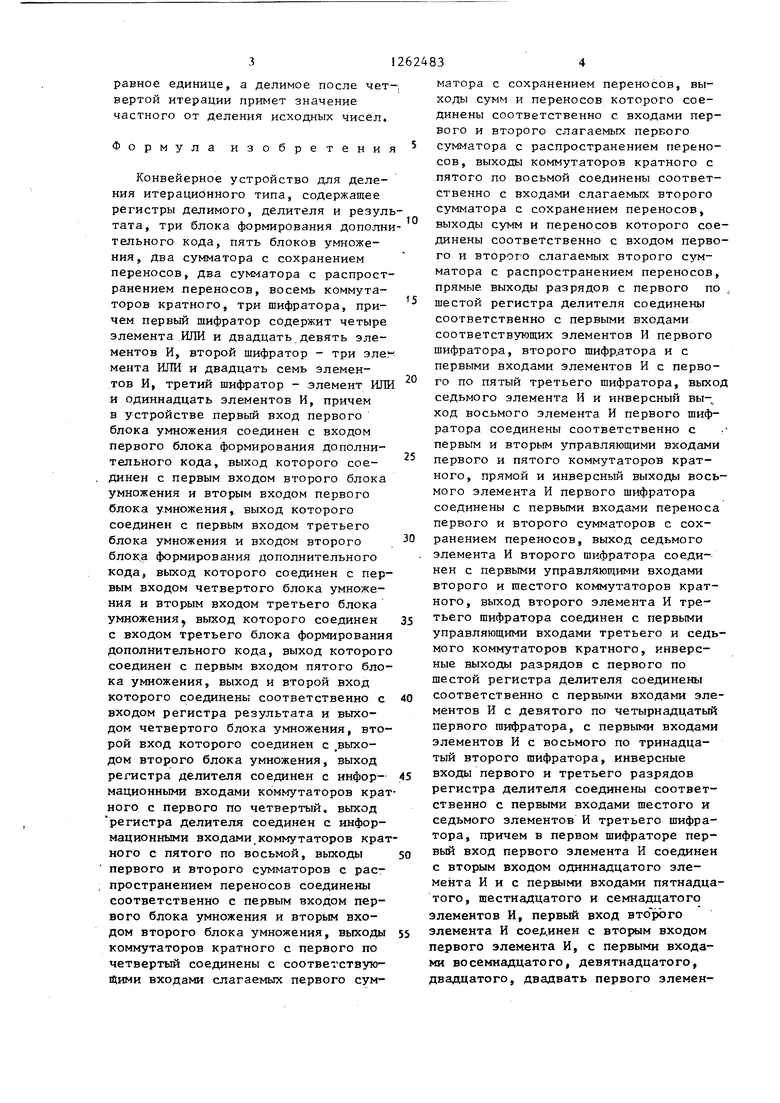

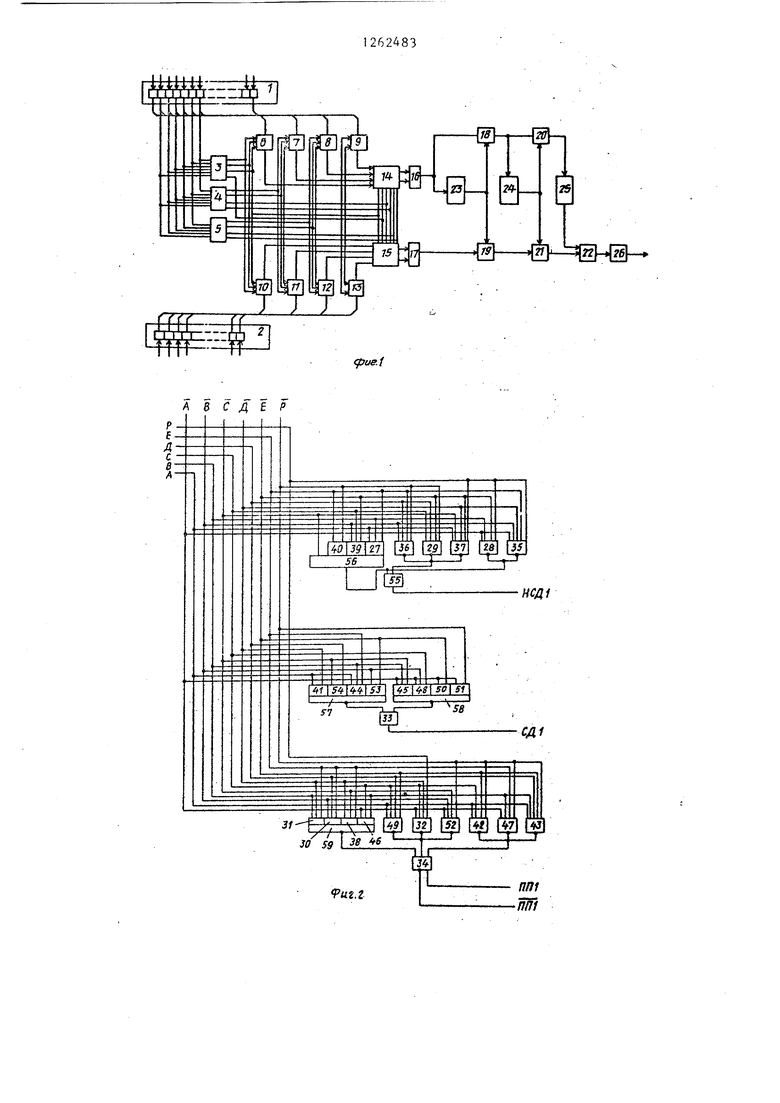

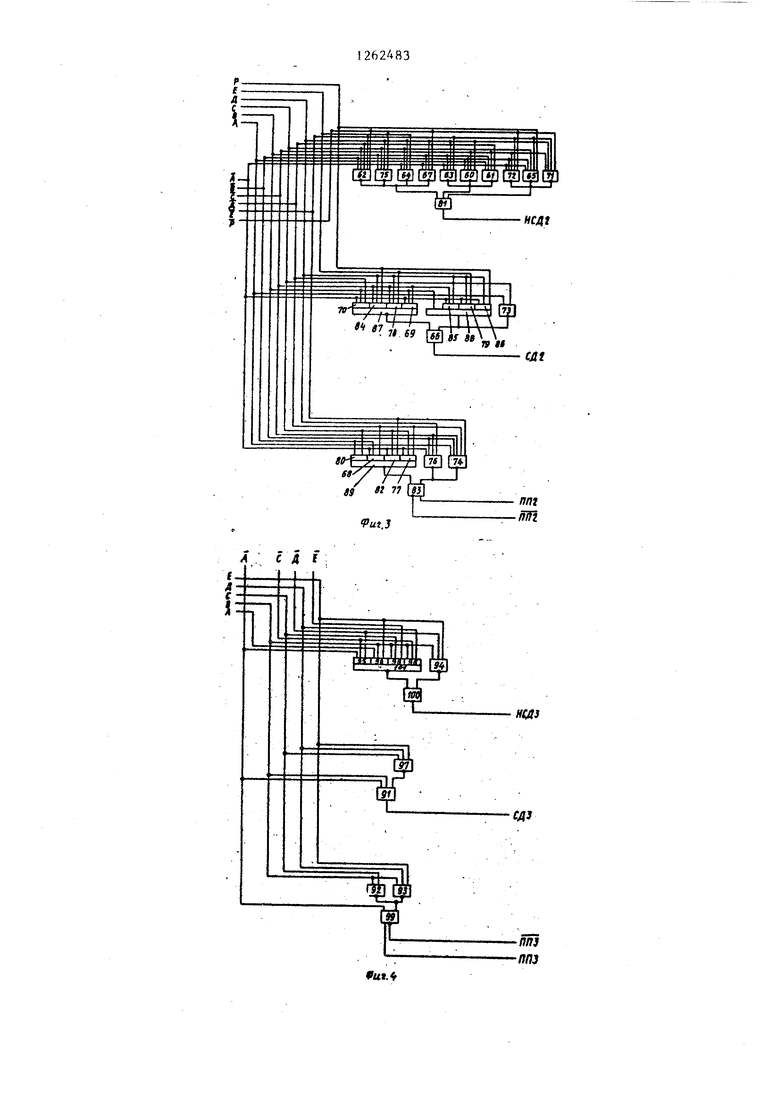

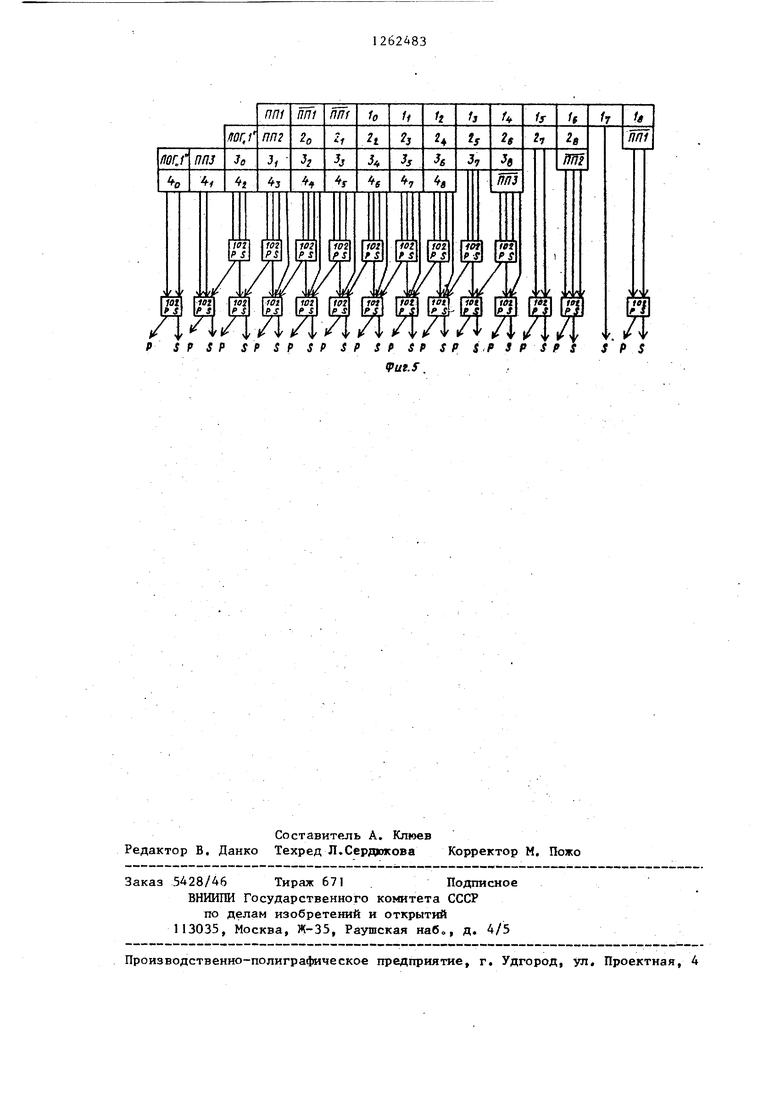

Изобретение относится к автомати ке и вычислительной тех,нике и предназначено для использования в цифро вых арифметических устройствах, Целью изобретения является упрощение устройства. На фиг. 1 представлена схема кон вейерного устройства для деления итерационного типа; на -фиг. 2 - схе ма первого шифратора; на фиг. 3 схема второго шифратора; на фиг. 4 схема третьего шифратора; на фиг. 5 схема сумматора с сохранением перенасов. Конвейерное устройство для деления итерационного типа (фиг. О со держит, регистр 1 делителя, регистр .делимого, шифраторы 3-5, коммутаторы 6.-13 кратного, сумматоры 14 и 15 с сохранением переносов, сумматоры и 17 с распространением переносов, блоки 18-22 умножения, блоки 23-25 формирования дополнительного кода, регистр 26 результата. Первый шифратор 3 (фиг. 2) содер жит элементы И 27-55, элементы ИЛИ 56-59. Второй шифратор 4 (фиг. З) с держит элементы И 60-86, элементы ИЛ 87-89. Третий шифратор 5 (фиг. 4) содержит элементы И 90-100, элемент ИЛИ 101. Сумматоры 14 и 15 с сохранением переноса (фиг. 5) содер жат одноразрядные сумматоры 102. Сумматоры 14 и 15 с сохранением I переноса идентичны сумматорам известного устройства. Коммутаторы 6-8, 10-12 кратного идентичны коммутаторам известного устройства и при сигналах на первом, втором и третьем управляющих входах выполняют соответственно передачу информации на вьгход со сдвигом, инверсно и без сдвига. Коммутаторы 9 и 13 кратного идентичны коммутаторам известного устройства и при сигналах на нулевом и втором управляющих входах выполняют соответственно передачу информации на выход инверсно или прямо Конвейерное устройство для деления итерационного типа работает следующим образом, Дпя определенности примем разрядность делителя равной 8, На регистры 1 и 2 заносятся соответственно делитель и делимое. Шесть старших разрядов делителя поступают на шифраторы 3-5, Самый старший разряд (нулевой) нормализованного делителя равен единице и в шифраиии не участвует. Шифраторы 3-5 формируют сигналы, управляющие формированием кратных. При помощи управляющих сигналов СД, НСД, ПП в коммутаторах 6-9 формируются соответственно первое, второе, третье и четвертое кратные делителю числа, а в коммутаторах 1013 - соответственно первое, второе, третье и четвертое кратные делимого. Сформированные четыре кратные делителю числа суммируются в доцо.ггкятельном коде на сумматоре 14 с сохранением переносов.как это представлено на фиг. 5, при этом сигна:ть: ПП для первых трех кратных выполняют роль единицы дополнительного кода. Аналогично .суммируются четыре кратные делимому числа на сумматоре 15. После сложения результатов сум:чаторов с сохранением переносов на сумматорах 16 и 17 с распространением переносов образуются результаты первой итерации деления (ДТ1). В результате первой итерации в старших разрядах ДТ1 будет шесть нулей, либо шесть единиц. Во второй итерации в блоке 23 формирования дополнительного кода от 12 старших разрядов ДЛ (не считая первого) формируется дополнительный код, на который в блоках 18 и 19 умножаются ДТ1, и результат первой итерации преобразования делимого (ДМ), в результате чего образуются новые значения ДТ2 и ДМ2, причем ДТ2 будет содержать после первого разряда 12 нулей или единиц, В третьей итерации в блоке 24 формирования дополнительного кода т 24 старших разрядов ДТ2 (не счиая первого) формируется дополниельный код, на который в блоках 20 21 умножают ДТ2 и ДМ2, в результае чего образуются новые значения ТЗ и ДМЗ, причем ДТЗ будет содерать после первого разряда 24 нуля ли единицы. В четвертой итерации в блоке 25 ормирования дополнительного кода . ормируется дополнительный код, на оторый в блоке 22 умножается ДМЗ, результат умножения записывается регистр 26 результата.ДТЗ при том на дополнительный код не умноается, так как результат умножения аранее известен и примет значение. равное единице, а делимое после чет вертой итерации примет значение частного от деления исходных чисел. Формула изобретени Конвейерное устройство для деления итерационного типа, содержащее регистры делимого, делителя и резул тата, три блока формирования дополн тельного кода, пять блоков умножения, два сумматора с сохранением переносов, два сумматора с распрост ранением переносов, восемь коммутаторов кратного, три шифратора, причем первый шифратор содержит четыре элемента ИЛИ и двадцать девять элементов И, второй шифратор - три элe мента ИЛИ и двадцать семь элементов И, третий шифратор - элемент ИЛ и одиннадцать элементов И, причем в устройстве первый вход первого блока умножения соединен с входом первого блока формирования дополнительного кода, выход которого соединен с первым входом второго блока умножения и вторым входом первого блока умножения, выход которого соединен с первым входом третьего блока умножения и входом второго блока формирования дополнительного кода, выход которого соединен с пер вым входом четвертого блока умножения и вторым входом третьего блока умножения выход которого соединен с входом третьего блока формировани дополнительного кода, выход которог соединен с первым входом пятого бло ка умножения, выход и второй вход которого соединены соответственно с входом регистра результата и выходом четвертого блока умножения, вто рой вход которого соединен с выходом второго блока умножения, выход регистра делителя соединен с информационными входами коммутаторов кра ного с первого по четвертый, выход регистра делителя соединен с информационными входами коммутаторов кра ного с пятого по восьмой, выходы первого и второго сумматоров с распространением переносов соединены соответственно с первым входом первого блока умножения и вторьи входом второго блока умножения, выходы коммутаторов кратного с первого по четвертый соединены с соотве7ствуюЩими входами слагаемых первого сумматора с сохранением переносов, выходы сумм и переносов которого соединены соответственно с входами первого и второго слагаемых первого сумматора с распространением переносов, выходы коммутаторов кратного с пятого по восьмой соединены соответственно с входами слагаемых второго сумматора с сохранением переносов, выходы сумм и переносов которого соединены соответственно с входом первого и второго слагаемых второго сумматора с распространением переносов, прямые выходы разрядов с первого по , шестой регистра делителя соединены соответственно с первыми входами соответствующих элементов И первого шифратора, второго шифр.атора и с первыми входами элементов И с первого по пятый третьего шифратора, выход седьмого элемента И и инверсный выход восьмого элемента И первого шифратора соединены соответственно с .первым и вторым управляющими входами первого и пятого коммутаторов кратного, прямой и инверсный выходы восьмого элемента И первого шифратора соединены с первыми входами переноса первого и второго сумматоров с сохранением переносов, выход седьмого элемента И второго шифратора соединен с первыми управляющими входами второго и шестого коммутаторов кратного, выход второго элемента И тре- тьего шифратора соединен с первыми управляющими входами третьего и седьмого коммутаторов кратного, инверсные выходы раарядов с первого по шестой регистра делителя соединены соответственно с первыми входами элементов И с девятого по четырнадцатый первого шифратора, с первыми входами элементов И с восьмого по тринадцатый второго шифратора, инверсные входы первого и третьего разрядов регистра делителя соединены соответственно с первыми входами шестого и седьмого элементов И третьего шифратора, причем в первом шифраторе первый вход первого элемента И соединен с вторым входом одиннадцатого элемента И и с первыми входами пятнадцатого, шестнадцатого и семнадцатого элементов И, первый вход второго элемента И соединен с вторым входом первого элемента И, с первыми входами восемнадцатого, девятнадцатого, двадцатого, двадвать первого элеменTOE И И С вторыми входами пятого и семнадцатого элементов И, первый вход третьего элемента И соединен с вторым входом тринадцатого элемен та И и с первыми входами двадцать второго, двадцать третьего элементов И, первый В.ХОД четвертого элемента И соединен с вторым входом двадцать третьего и третьим входом семнадцатого элементов И, первый вход четвертого элемента И соединен с вторым входом двадцать третьего и третьим входом семнадцатого элементов И, первый вход пятого элемента И соединен с вторыми входами четвертого, четырнадцатого и третьи входом первого элементов И, первый вход девятого элемента И соединен с вторыми входами второго, двадцать второго, двадцать первого и с первыми входами двадцать четвертого, двадцать пятого, двадцать шестого элементов И, первый вход десятого элемента И соединен с вторыми входами девятого и двадцать шестого элементов И, с третьими входами три- .надцатого, двадцать второго и четвертого, с первым входом двадцать седьмого элементов И, первый вход одиннадцатого элемента И соединен с первым .входом двадцать восьмого, вторым входом девятнадцатого и третьим входом двадцать шестого элементов И, первый вход двенадцатого элемента И соединен с вторым входом шестого, с третьими входами пятого и девятого элементов И, первый вход тринадцатого элемента И соединен с третьими входами второго, двадцать третьего, одиннадцатого и в-торыми входами шестнадцатого и двадцать четвертого элементов И, первый вход четырнадцатого элемента И соединен с вторыми входами десятого и третьего, четвертым входом двадцать шесто го элементов И, инверсные выходы второго и девятого элементов И соединены с первым входом двадцать девятого элемента И, выходы первого, тринадцатого и четырнадцатого элементов И соединены соответственно с входами с первого по третий первого элемента ИЛИ, выходы восемнадцатого и двадцать восьмого элементов И соединены соответственно с первьм и вторым входами второго элемента ИЛИ выход девятнадцатого элемента И соединен с первым входом третьего элемента ИЛИ, выходы четвертого, пятого, двенадцатого и двадцатого элементов И соединены соответственно с входами с первого по четвертый четвертого элемента ИЛИ, инверсный выход которого соединен с первым входом восьмого элемента И, инверсные выходы шестого и двадцать шестого элементов И соединены с вторым входо восьмого элемента И, третий вход которого соединен с инверсными выходами семнадцатого и двадцать первого элементов И причем во втором шифраторе первый вход первого элемента И соединен с вторым входом второго, с первыми входами четырнадцатого и пятнадцатого элементов И, первый вход второго элемента И соединен с вторыми входами четвертого, восьмого десятого и пятнадцатого, с первыми входоми шестнадцатого и семнадцатого элементов И, первый вход третьего элемента И соединен с вторыми входами шестнадцатого, пятого, шестого и четырнадцатого, с первым входом восемнадцатого элементов И, первый вхо четвертого элемента И соединен с вторым входом первого и с первыми входами девятнадцатого и двадцатого элементов И, первый вход пятого элемента И соединен с вторыми входами девятнадцатого и двадцатого элементов И первый вход восьмого элемента И соединен с вторыми входами тринадцатого одиннадцатого и семнадцатого, третьими входами пятого и десятого элементов И, первый вход девятого элемента И соединен с первым входом двадцать первого, вторым входом третьего третьими входами первого, тринадцатого и шестого элементов И, первый вход десятого элемента И соединен с третьими входами девятнадцатого, семнадцатого и второго, вторым входом двенадцатого, четвертым входом первого элементов И, первый вход двенадцатого элемента И соединен с четвертым входом тринадцатого и с третьими входами четвертого, третьего элементов И, инверсные выходы третьего, пятого, восьмого и шестнадцатого элементов И соединены с первым входом двадцать второго элемента И, второй вход которого соединен с инверсными входами первого, второго и четвертого, элементов И, четвертые выходы шестого, двенадцатого и тринадцатого элементов И соединены

с третьим входом двадцать второго элемента И, выходы одиннадцатого и десятого элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, инверсный выход которого соединен с первым входом седьмого элемента И, выход двадцатого элемента И соединен с первым входом второго элемента ИЛИ, выходы девятого, восемнадцатого, двадцать первого и двадцать третьего элементов И соединены соответственно с входами с первого по четвертый третьего элемента ИЛИ, инверсный выход которого соединен с первым входом двадцать четвертого элемента И, второй вход которого соединен с инверсными выходами пятнадцатого и семнадцатого элементов И, причем в третьем шифраторе первый вход второго элемента И соединен с вторыми входами третьего и четвертого элементов И, первый вход третьего элемента И соединен с первыми входами восьмого и девятого элементов И, первый вход четвертого элемента И соединен с вторыми входами седьмого и восьмого элементов И, первый вход пятого элемента И соединен с третьими входами четвертого и восьмого элементов И, первый вход шестого элемента И соединен с вторым входом второго и с первым входом десятого элементов И, выходы первого, шестого, седьмого и девятого элементов И соединены соответственно с входами с первого по четвертый элемента ИЛИ, инверсный выход восьмого элемента И, инверсные выходы третьего и четвертого элементов И соединены с вторым входом десятого элемента И, отличающее с я тем, что, с целью упрощения устройства, инверсные выходы четвертого и пятого разрядов регистра делителя соединены соответственно с вторыми входами шестого и девятого элементов И третьего шифратора, выход двадцать девятого элемента И первого шифратора соединен с третьими управляющими входами первого и пятого коммутаторов кратного, инверсный выход двадцать,четвертого и выход двадцать второго элементов И второго шифратора соединены соответственно с вторым и третьим управляюШИми входами второго и шестого коммутаторов кратного, прямой и инверсный вьпсоды двадцать четвертого элемента И второго шифратора соединены

с вторыми входами переноса первого и второго сумматоров с сохранением переносов, инверсный выход десятого элемента И третьего шифратора соединен с вторыми управляющими входами третьего и седьмого и с первыми управляющими входами четвертого и восьмого коммутаторов кратного, выход одиннадцатого элемента И третьего шифратора соединен с тре0тьими управляющими входами третьего и седьмого коммутаторов кратного, прямой выход десятого элемента И третьего шифратора соединен с вторыми управляющими входа5ми четвертого и восьмого коммутаторов кратного, прямой и инверсный выходы десятого элемента И третьего шифратора соединены с третьими входами переноса первого и второго сумма0торов с сохранением переносов, причем в первом шифраторе первый вход четвертого элемента И соединен с третьими входами десятого, третьего

5 и вторым входом двадцать восьмого элементов И, первый вход шестого элемента И соединен с четвертыми входами одиннадцатого, второго и девятого элементов И, первый вход пятого элемента И соед11нен с четвертым входом

0 десятого,ПЯТЫМ входом девятого, третьим входом двадцать первого, .вторыми входами двенадцатого и .восемнадцатого элементов И, первый вход первого элемента И соединен с третьим

5 входом восемнадцатого и четвертым входом двадцать третьего элементов И, первый вход третьего элемента И соединен с вторым входом двадцатого, третьими входами шестого и шестнадцатого элементов И, первый вход девятого элемента И соединен с третьими входами девятнадцатого и двадцатого, четвертым входом шестого элемента И, , первый вход одиннадцатого элемента И соединен с четвертым входом первого элемента ИЛИ и с третьим входом двенадцатого элемента И, первый вход двенадцатого элемента И соеда1неи с пятым входом одиннадцатого и вторым входом пятнадцатого элемента И, первый вход тринадцатого элемента И соединен с четвертыми входами третьего и семнадцатого, вторым входом двадцать седьмого элементов И, первый вход четьфнадцатого элемента И соединен с вторым входом двадцать пятого, четвертыми входами шестнадцатого и двадцать первого, с пятым входом

семнадцатого элементов И, выход первого элемента ИЛИ соединен с первым входом двадцать девятого элемента И, второй вход которого соединен с инверсными входами третьего, десятого и одиннадцатого элементов И, выходы пятнадцатого и двадцать седьмого элементов И соединены соответственно с третьим и четвертым входами второго элемента ИЛИ, инверсный выход которого соединен с первым входом седьмого элемента И, второй вход которого соединен с инверсным выходом третьего элемента ИЛИ, входы с второго по четвертый которого соединены соответственно с выходами двадцать второго, двадцать четвертого и двадцать пятого элементов И, инверсный выход двадцать третьего элемента И соединен с вторым входом восьмого элемента И, третий вход которого соединен с инверсным выходом шестнадцатого элемента И, причем во втором шифраторе первый вход второго элемента И соединен с третьим входом одиннадцатого элемента И и вторым входом второго элемента ИЛИ, первый вход третьего элемента И соединен со вторым входом двадцать первого и первым входом двадцать третьего элементов И, первый вход четвертого элемента И соединен с третьими входами шестнадцатого, восьмого и двенадцатого, четвертым входом пятого, первыми входами двадцать пятого, двадцать шестого и двадцать седьмого, четвертым входом семнадцатого элементов И, первый вход шестого элемента И соединен с вторыми входами двадцать пятого и двадцать седьмого элементов И, первый вход восьмого элемента И соединен с четвертыми входами четвертого и шестого, вторыми входами двадцать шестого и девятого, двадцать третьего и восемнадцатого, третьими входами двадцатого и двадцать седьмого элементов И, первьш вход десятого элемента И соединен с пятым входом тринадцатого, третьими входами двадцать пятого, двадцать шестого и пятнадцатого элементов И, первый вход одиннадцатого элемента И соединен с четвертыми входа да третьего, второго и пятнадцатого, третьими входами девятого и восемнадцатого элементов И, первый вход двенадцатого элемента И соединен с пятыми входами шестого и пят- надцатого, третьим входом двадцать третьего элементов И, первый вход тринадцатого элемента И соединен с пятым входом третьего, четвертыми входами восьмого и -двенадцатого элементов И, вьпсоды девятнадцатого и двадцать пятого элементов И соединены соответственно с третьим и чет- i.j вертым входами первого элемента ИЛИ, выходы двадцать шестого и двадцать седьмого элементов И соединены соответственно с третьим и четвертым входами второго элемента ИЛИ, выход которого соединен с инверсным выходом четырнадцатого элемента И и вторым входом седьмого элемента И, причем в третьем шифраторе первый вход второго элемента И соединен с вторыми входами первого и пятого, третьими входами седьмого и девятого эле ментов И, первый вход пятого элемента И соединен с третьим входом пер вого элемента И, первый вход седьмоо элемента И - с третьим входом . естого элемента И, второй вход коорого соединен с вторым входом пяого элемента И, инверсный выод элемента РШИ соединен с торым входом одиннадцатого лемента И.

fet;i:rzr:ii-7 III I III III

A В С Д P

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1280613A1 |

| Сумматор в знакоразрядной позиционно-остаточной системе счисления | 1986 |

|

SU1383349A1 |

| Устройство для обработки символьной информации | 1980 |

|

SU1010624A1 |

| Операционный модуль | 1984 |

|

SU1406592A1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2009 |

|

RU2408058C2 |

| СУММАТОР | 2008 |

|

RU2380739C1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| Устройство для вычисления симметрических булевых функций | 1991 |

|

SU1835542A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

Изобретение относится к области вычислительной техники и может быть использовано в арифметических устройствах быстродействующих ЭВМ. Целью изобретения является упрощение устройства. Поставленная цель достигается тем, что в устройстве, содержащем рёгист делимого, делителя и результата, три блока формирования дополнительного кода, пять блоков умножения, три шифратора, два сумматора с сохранением переносов, два сумматора с распространением переносов и восемь коммутаторов кратного, применены более простые шифраторы и соответственно изменены связи. 5 ил.

НСДЗ

| Устройство для деления | 1975 |

|

SU602944A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Конвейерное устройство для деления интерационного типа | 1984 |

|

SU1179321A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1985-03-18—Подача