Изобретение относится к вычислительной технике и может быть использовано в локальных кольцевых сетях ЭВМ.

Известно устройство управления передачей данных 1, содержащее блок для соединения линий связи, запоминающий блок, процессор, регистры постановки адресов, блоки формирования адресов, дешифратор адресов, модем. Устройство управляет обменом данными между процессорами высокого уровня иерархии и линиями связи с использованием программ, хранящихся в памяти.

Однако известное устройство не обес- печиаает достаточно высокий уровень достоверности передачи, та как в нем не предусмотрено исправлением фазовых ошибок.

Наиболее близким по технической сущности к предлагаемому является устройство для обмена информацией в кольцевом канале связ 2J, содержащее блок приемопередатчиков, блок переключения режима, блок передачи информации, три элемента ИЛИ, блок синхронизации, регистр приема, дешифратор, регистр передачи, три элемента И, элемент НЕ и два триггера.

Однако это устройство также не обеспечивает достаточно высокой достоверности передачи из-за отсутствия устранения фазовых ошибок,

Целью изобретения является повышение достоверности передачи за счет исправления фазовых ошибок. Цель достигается тем, что в устройство для обмена информацией, содержащее блок приемников, блок передатчиков, первый мультиплексор информации, два регистра, дешифратор, блок синхронизации, причем первый и второй выходы блока приемников соединены с информационным и синхронизирующим входом первого регистра, выход которого соединен с входом дешифратора, третий выход блока приемников соединен с информационным входом первого мультиплексора информации, выходы блока приемников и выходы блока передатчиков являются линейными входом и выходом устройства, введены мультиплексор синхроимпульсов, буферная память, блок управления памятью, второй мультиплексор информации, блок кодирования, при этом четвертый выход блока приемников соединен с информа- ционным входом . мультиплексора синхроимпульсов, управляющий вход которого соединен с выходом дешифратора, управляющимвходом первого мультиплексора информации и информационным входом второго регистра, выход которого соединен с синхровходом блока

0

0

0

передатчиков, информационный вход которого соединен с выходом блока кодирования, вход которого соединен с выходом второго мультиплексора информации, информационный вход которого соединен с выходом буферной памяти, информационный вход которой соединен с выходом муль- типлексора информации, выходы мультиплексора синхроимпульсов и блока синхронизации соединены с первым и вторым входамшблока управления памятью, первый и второй выходы которого соединены с управляющими входами буферной памяти и второго мультиплексора

5 информации.

При анализе известных технических решений не обнаружено решений с признаками, сходными с отличительными признаками заявляемого решения, что дает основание считать предлагаемое техническое решение соответствующим критериям существенные отличия и новизна. Этот вывод подтверждается тем, что создается недостижимый ранее положительный эф5 фект, заключающийся в повышении достоверности передачи сигналов и обусловленный новыми признаками по сравнению с использованием известных технических решений.

Благодаря введению мультиплексора синхроимпульсов, буферной памяти блока управления памятью, второго мультиплексора информации, блока кодирования с соответствующими связями заявляемое

5 техническое решение приобретает новые свойства, получение которых не обеспечивают прототип и другие технические решения, а именно создается возможность повысить достоверность передачи за счет

0 исправления фазовых ошибок.

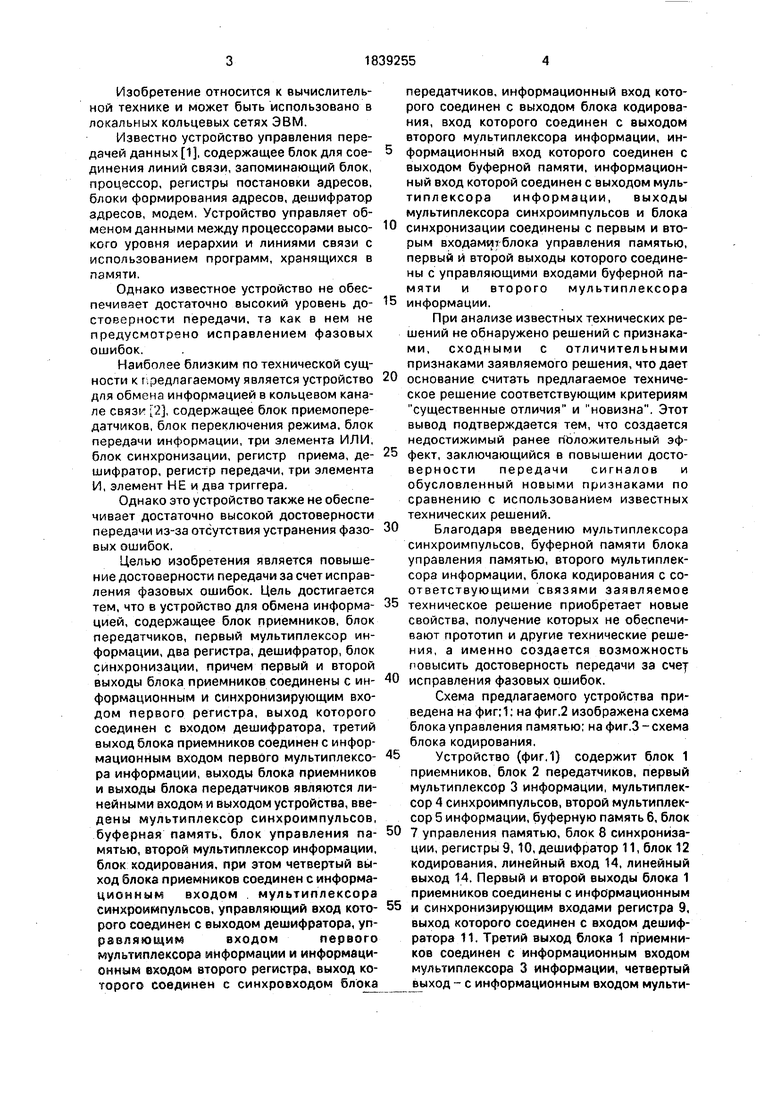

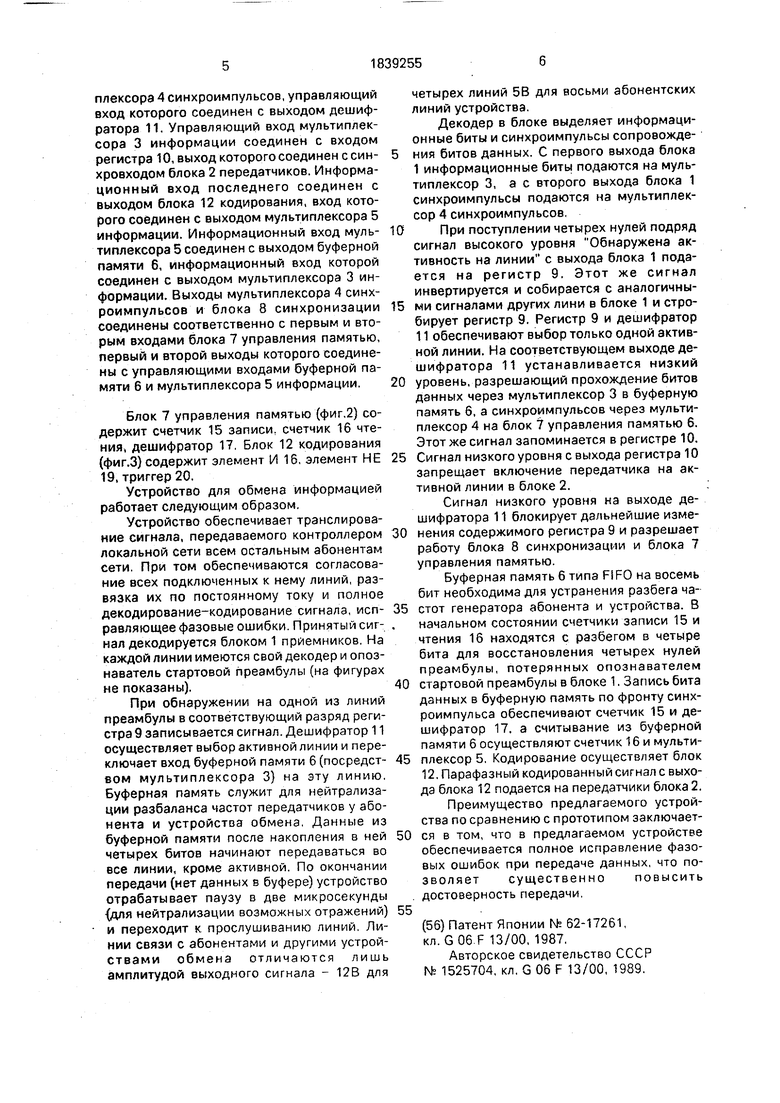

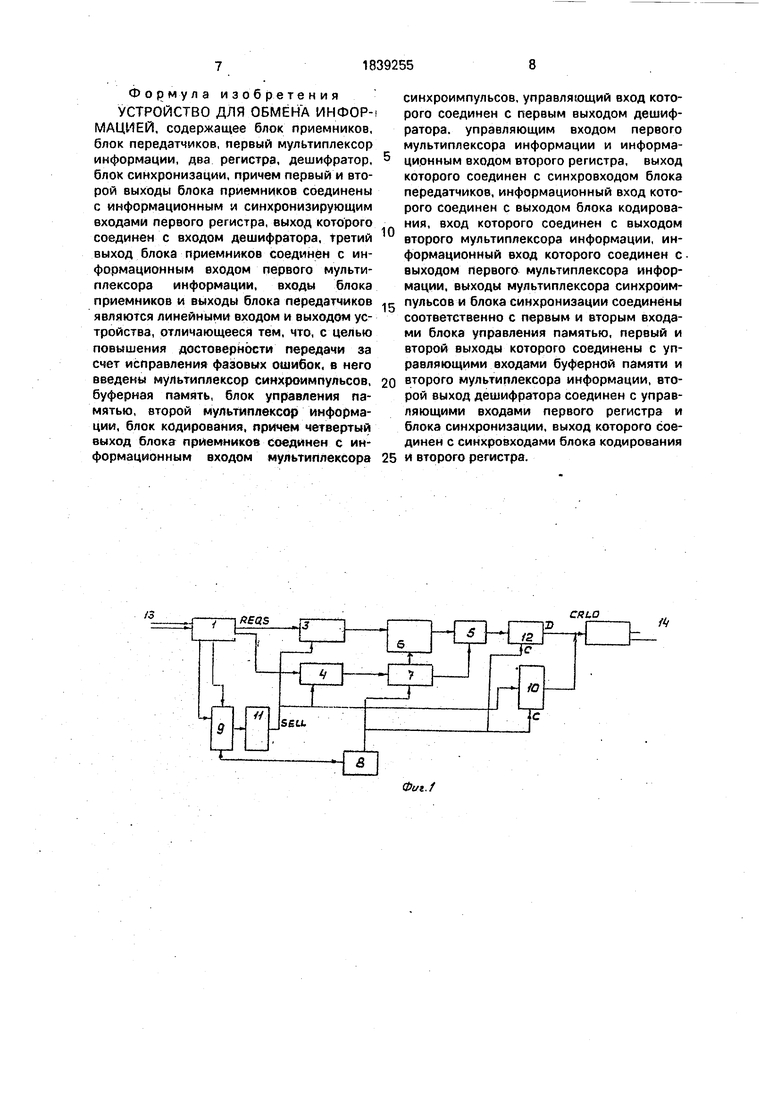

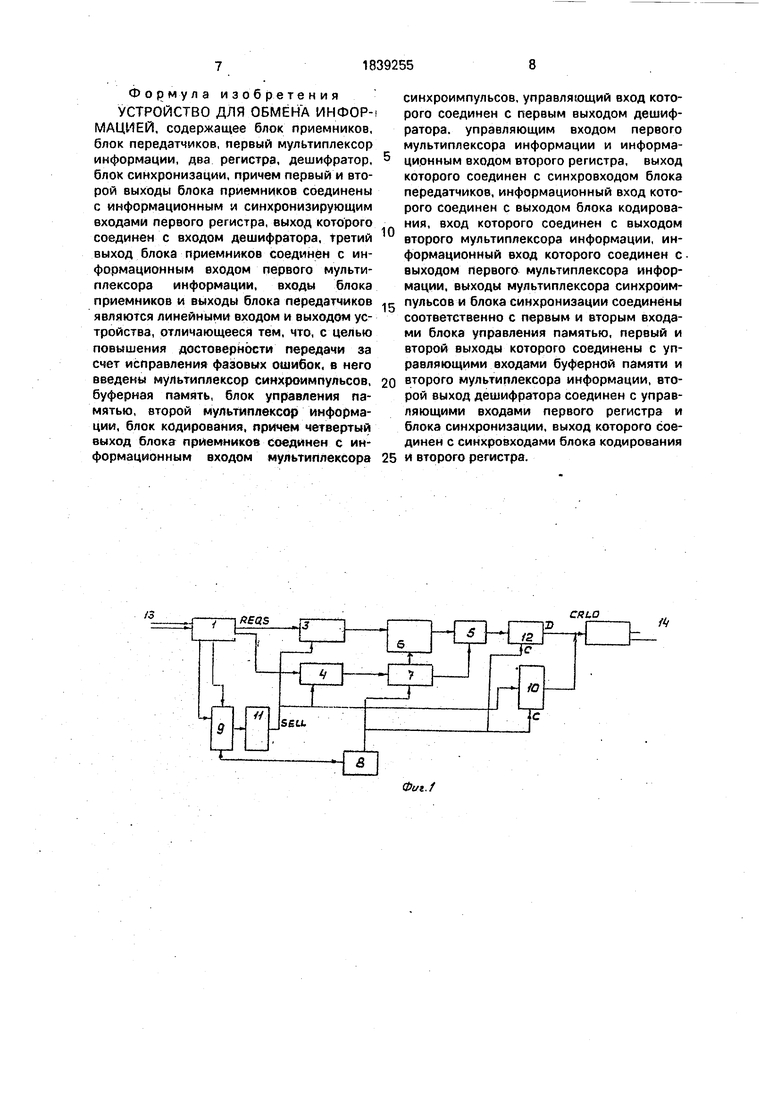

Схема предлагаемого устройства приведена на фиг;1; на фиг.2 изображена схема блока управления памятью; на фиг.З - схема блока кодирования.

Устройство (фиг,1) содержит блок 1 приемников, блок 2 передатчиков, первый мультиплексор 3 информации, мультиплексор 4 синхроимпульсов, второй мультиплексор 5 информации, буферную память 6, блок

0 7 управления памятью, блок 8 синхронизации, регистры 9,10, дешифратор 11, блок 12 кодирования, линейный вход 14, линейный выход 14. Первый и второй выходы блока 1 приемников соединены с информационным

5 и синхронизирующим входами регистра 9, выход которого соединен с входом дешифратора 11. Третий выход блока 1 приемников соединен с информационным входом мультиплексора 3 информации, четвертый выход - с информационным входом мульти5

плексора 4 синхроимпульсов, управляющий вход которого соединен с выходом дешифратора 11. Управляющий вход мультиплексора 3 информации соединен с входом регистра 10, выход которого соединен с син- хровходом блока 2 передатчиков. Информационный вход последнего соединен с выходом блока 12 кодирования, вход которого соединен с выходом мультиплексора 5 информации. Информационный вход мультиплексора 5 соединен с выходом буферной памяти 6, информационный вход которой соединен с выходом мультиплексора 3 информации. Выходы мультиплексора 4 синхроимпульсов и блока 8 синхронизации соединены соответственно с первым и вторым входами блока 7 управления памятью, первый и второй выходы которого соединены с управляющими входами буферной памяти 6 и мультиплексора 5 информации.

Блок 7 управления памятью (фиг.2) содержит счетчик 15 записи, счетчик 16 чтения, дешифратор 17. Блок 12 кодирования (фиг.3) содержит элемент И 16, элемент НЕ 19, триггер 20.

Устройство для обмена информацией работает следующим образом.

Устройство обеспечивает транслирование сигнала, передаваемого контроллером локальной сети всем остальным абонентам сети. При том обеспечиваются согласование всех подключенных к нему линий, развязка их по постоянному току и полное декодирование-кодирование сигнала, исправляющее фазовые ошибки. Принятый сигнал декодируется блоком 1 приемников. На каждой линии имеются свой декодер и опоз- наватель стартовой преамбулы (на фигурах не показаны).

При обнаружении на одной из линий преамбулы в соответствующий разряд регистра 9 записывается сигнал. Дешифратор 11 осуществляет выбор активной линии и переключает вход буферной памяти 6 (посредством мультиплексора 3} на эту линию. Буферная память служит для нейтрализации разбаланса частот передатчиков у абонента и устройства обмена, Данные из буферной памяти после накопления в ней четырех битов начинают передаваться во все линии, кроме активной. По окончании передачи (нет данных в буфере) устройство отрабатывает паузу в две микросекунды {для нейтрализации возможных отражений) и переходит к прослушиванию линий, Линии связи с абонентами и другими устройствами обмена отличаются лишь амплитудой выходного сигнала - 12В для

четырех линий 5В для восьми абонентских линий устройства.

Декодер в блоке выделяет информационные биты и синхроимпульсы сопровожде- ния битов данных. С первого выхода блока

I информационные биты подаются на мультиплексор 3, ас второго выхода блока 1 синхроимпульсы подаются на мультиплексор 4 синхроимпульсов,

При поступлении четырех нулей подряд сигнал высокого уровня Обнаружена активность на линии с выхода блока 1 подается на регистр 9. Этот же сигнал инвертируется и собирается с аналогичными сигналами других лини в блоке 1 и стро- бирует регистр 9. Регистр 9 и дешифратор

II обеспечивают выбор только одной активной линии. На соответствующем выходе дешифратора 11 устанавливается низкий

уровень, разрешающий прохождение битов данных через мультиплексор 3 в буферную память б, а синхроимпульсов через мультиплексор 4 на блок 7 управления памятью 6. Этот же сигнал запоминается в регистре 10.

Сигнал низкого уровня с выхода регистра 10 запрещает включение передатчика на активной линии в блоке 2.

Сигнал низкого уровня на выходе дешифратора 11 блокирует дальнейшие изменения содержимого регистра 9 и разрешает работу блока 8 синхронизации и блока 7 управления памятью.

Буферная память б типа FIFO на восемь бит необходима для устранения разбега частот генератора абонента и устройства. В начальном состоянии счетчики записи 15 и чтения 16 находятся с разбегом в четыре бита для восстановления четырех нулей преамбулы, потерянных опознавателем

стартовой преамбулы в блоке 1, Запись бита данных в буферную память по фронту синхроимпульса обеспечивают счетчик 15 и дешифратор 17. а считывание из буферной памяти 6 осуществляют счетчик 16 и мультиплексор 5. Кодирование осуществляет блок 12. Парафазный кодированный сигнал с выхода блока 12 подается на передатчики блока 2. Преимущество предлагаемого устройства по сравнению с прототипом заключается в том, что в предлагаемом устройстве обеспечивается полное исправление фазовых ошибок при передаче данных, что позволяет существенно повысить достоверность передачи,

(56) Патент Японии № 62-17261, кл. G06.F 13/00, 1987,

Авторское свидетельство СССР Ms 1525704, кл. G 06 F 13/00, 1989.

Формула изобретения УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОР- МАЦИЕЙ, содержащее блок приемников, блок передатчиков, первый мультиплексор информации, два регистра, дешифратор, блок синхронизации, причем первый и второй выходы блока приемников соединены с информационным и синхронизирующим входами первого регистра, выход которого соединен с входом дешифратора, третий выход блока приемников соединен с информационным входом первого мультиплексора информации, входы блока приемников и выходы блока передатчиков являются линейными входом и выходом устройства, отличающееся тем, что, с целью повышения достоверности передачи за счет исправления фазовых ошибок, в него введены мультиплексор синхроимпульсов, буферная память, блок управления памятью, второй мультиплексор информации, блок кодирования, причем четвертый выход блока приемников соединен с информационным входом мультиплексора

0

синхроимпульсов, управляющий вход которого соединен с первым выходом дешифратора, управляющим входом первого мультиплексора информации и информационным входом второго регистра, выход которого соединен с сиихровходом блока передатчиков, информационный вход которого соединен с выходом блока кодирования, вход которого соединен с выходом второго мультиплексора информации, информационный вход которого соединен с выходом первого мультиплексора информации, выходы мультиплексора синхроимпульсов и блока синхронизации соединены соответственно с первым и вторым входами блока управления памятью, первый и второй выходы которого соединены с управляющими входами буферной памяти и

0 второго мультиплексора информации, второй выход дешифратора соединен с управляющими входами первого регистра и блока синхронизации, выход которого соединен с синхровходами блока кодирования

5 и второго регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления динамической памятью | 1990 |

|

SU1777143A2 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

| Телеизмерительная система с управляющей обратной связью | 1988 |

|

SU1571636A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ И ДОСТУПА К КАНАЛУ ДЛЯ ЛОКАЛЬНОЙ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ | 1992 |

|

RU2060539C1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

Изобретение относится к вычислительной техника Целью изобретения является повышение достоверности передачи за счет исправления фазовых ошибок Устройство содержит блок приемников, блок передатчиков, мультиплексор информации, два регистра, дешифратор, блок синхронизации. Новым является введение мультиплексора синхронизации, буферной памяти, блока управления памятью, второго мультиплексора информации и блока кодирования Зия

CRi.0

Фи г. Z

Авторы

Даты

1993-12-30—Публикация

1990-05-31—Подача