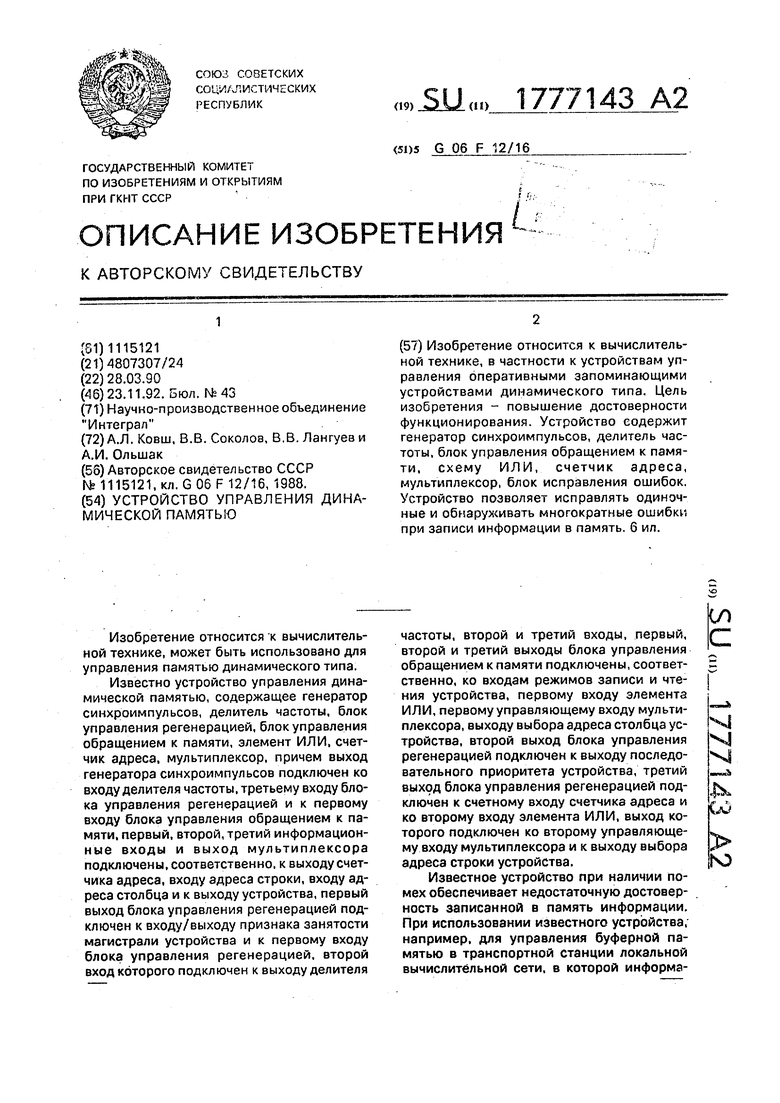

Изобретение относится к вычислительной технике, может быть использовано для управления памятью динамического типа.

Известно устройство управления динамической памятью, содержащее генератор синхроимпульсов, делитель частоты, блок управления регенерацией, блок управления обращением к памяти, элемент ИЛИ, счетчик адреса, мультиплексор, причем выход генератора синхроимпульсов подключен ко входу делителя частоты, третьему входу блока управления регенерацией и к первому входу блока управления обращением к памяти, первый, второй, третий информацион- ные входы и выход мультиплексора подключены, соответственно, к выходу счетчика адреса, входу адреса строки, входу адреса столбца и к выходу устройства, первый выход блока управления регенерацией подключен к входу/выходу признака занятости магистрали устройства и к первому входу блока управления регенерацией, второй вход которого подключен к выходу делителя

частоты, второй и третий входы, первый, второй и третий выходы блока управления обращением к памяти подключены, соответственно, ко входам режимов записи и чтения устройства, первому входу элемента ИЛИ, первому управляющему входу мультиплексора, выходу выбора адреса столбца устройства, второй выход блока управления регенерацией подключен к выходу последовательного приоритета устройства, третий выход блока управления регенерацией подключен к счетному входу счетчика адреса и ко второму входу элемента ИЛИ, выход которого подключен ко второму управляющему входу мультиплексора и к выходу выбора адреса строки устройства.

Известное устройство при наличии помех обеспечивает недостаточную достоверность записанной в память информации. При использовании известного устройства, например, для управления буферной памятью в транспортной станции локальной вычислительной сети, в которой информа(Л

С

ция из абонентской ЭВМ и из моноканала записывается для обработки и формирования массивов в буферную память, появление ошибок при записи приводит к невосстанавливаемым конфликтным ситуациям в реализации транспортного протокола.

Целью изобретения является повышение достоверности функционирования.

С этой целью в устройство управления динамической памятью введен блок исправления ошибок, причем первый и второй син- хровходы блока исправления ошибок подключены, соответственно, к выходу синхронизации приема информации и к выходу синхронизации выдачи информации блока управления обращением к памяти, информационный вход и информационный выход блока исправления ошибок подключены, соответственно, к информационным входу и выходу устройства, выход индикации неустранимой ошибки блока исправления ошибок исключен к выходу индикации ошибки устройства, причем блок исправления ошибок содержит регистр, узел контроля четности, схему сравнения, дешифратор и два коммутатора, причем М разрядов информационного входа блока исправления ошибок подключены к входу узла контроля четности, М разрядам информационного входа регистра, М разрядам первого входа схемы сравнения и М разрядам информационного входа первого коммутатора, где М - разрядность информации, К-й разряд выхода регистра подключен к К-м разрядам второго входа схемы сравнения и второго коммутатора, М+1-й выход регистра подключен к М+1-м разрядам второго входа схемы сравнения и второго коммутатора, М+1-й разряд информационного входа блока исправления ошибок подключен к М+2-му разряду второго входа схемы сравнения и М+1-м разрядам информационных входов первого коммутатора и регистра, М+2-й выход регистра подключен к М+1-му разряду первого входа схемы сравнения, М+2-й разряд информационного входа регистра подключен к выходу узла контроля четности и соединен с М+2-м разрядом первого входа схемы сравнения, выход схемы сравнения подключен к информационному входу дешифратора, первый, второй и третий выходы которого подключены, соответственно, к выходу индикации неустранимой ошибки блока исправления ошибок, стробирующим входам первого и второго коммутаторов, выходы которых подключены к информационному выходу блока исправления ошибок, первый и второй синхровходы блока исправления ошибок подключены, соответственно, к синхровходу регистра и стробиру- ющему входу дешифратора.

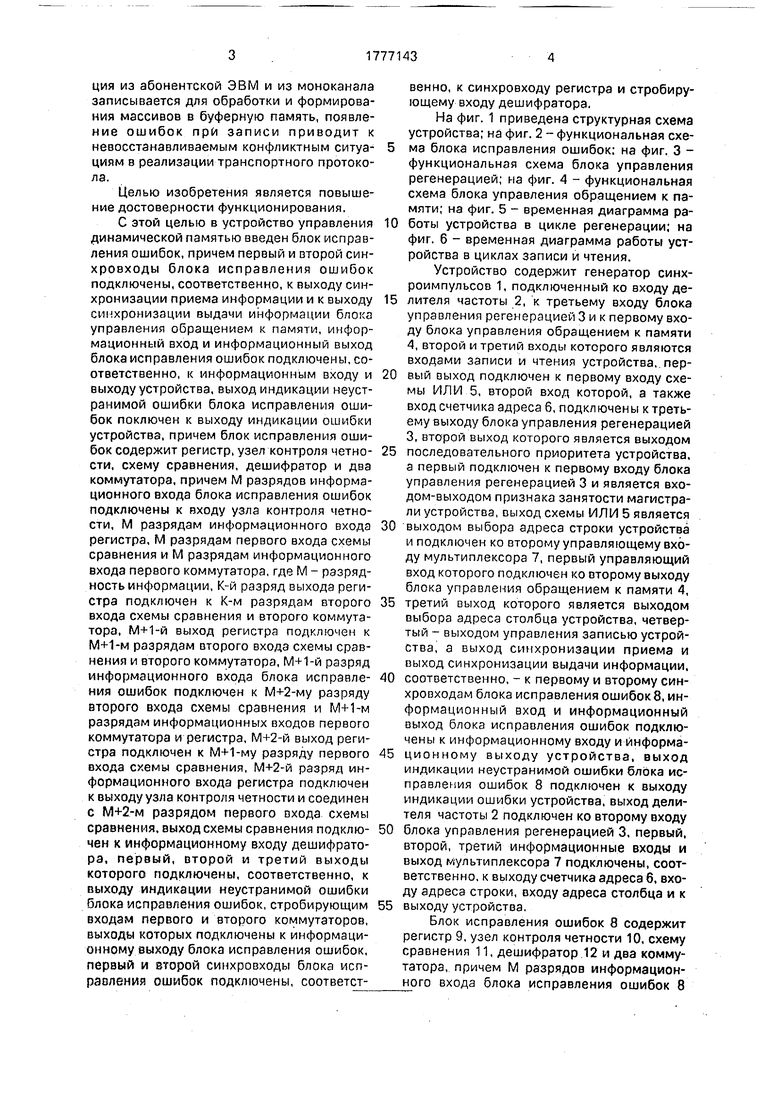

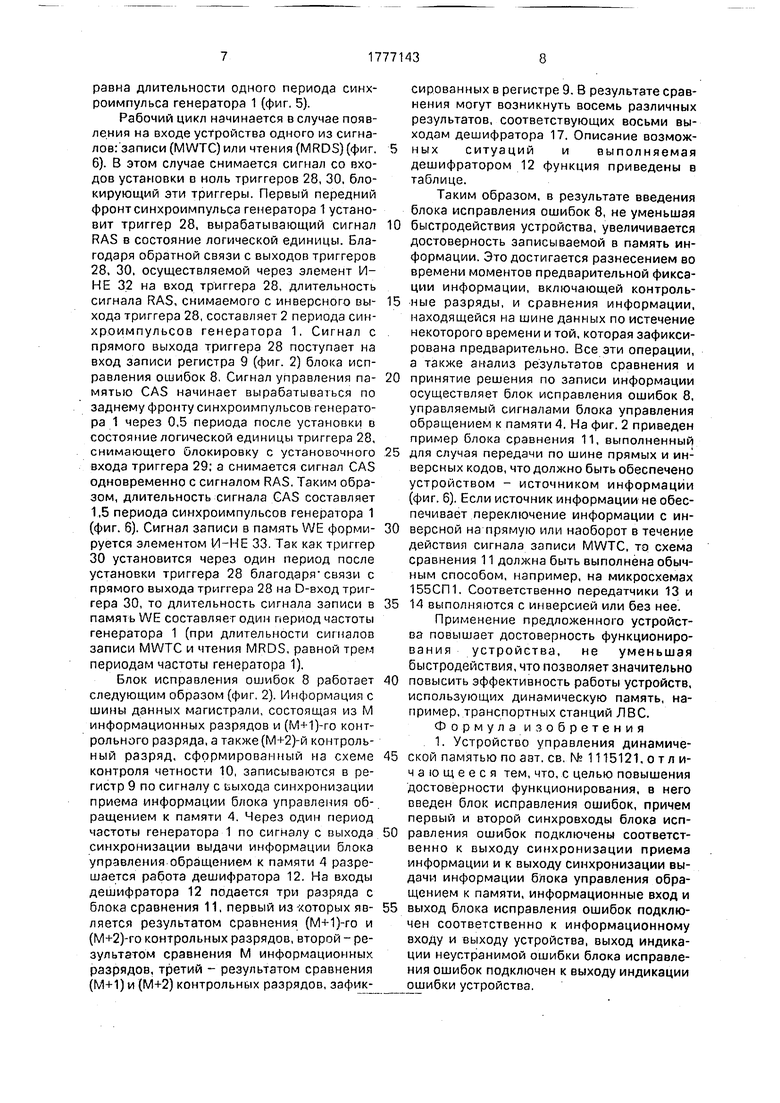

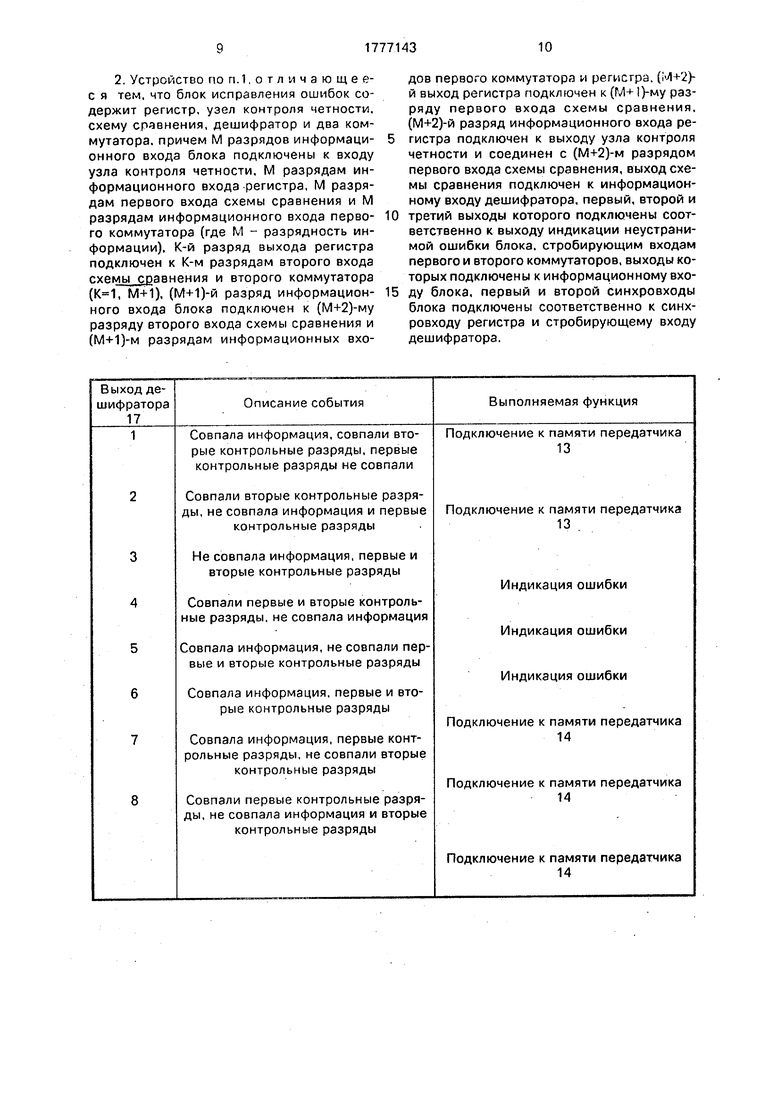

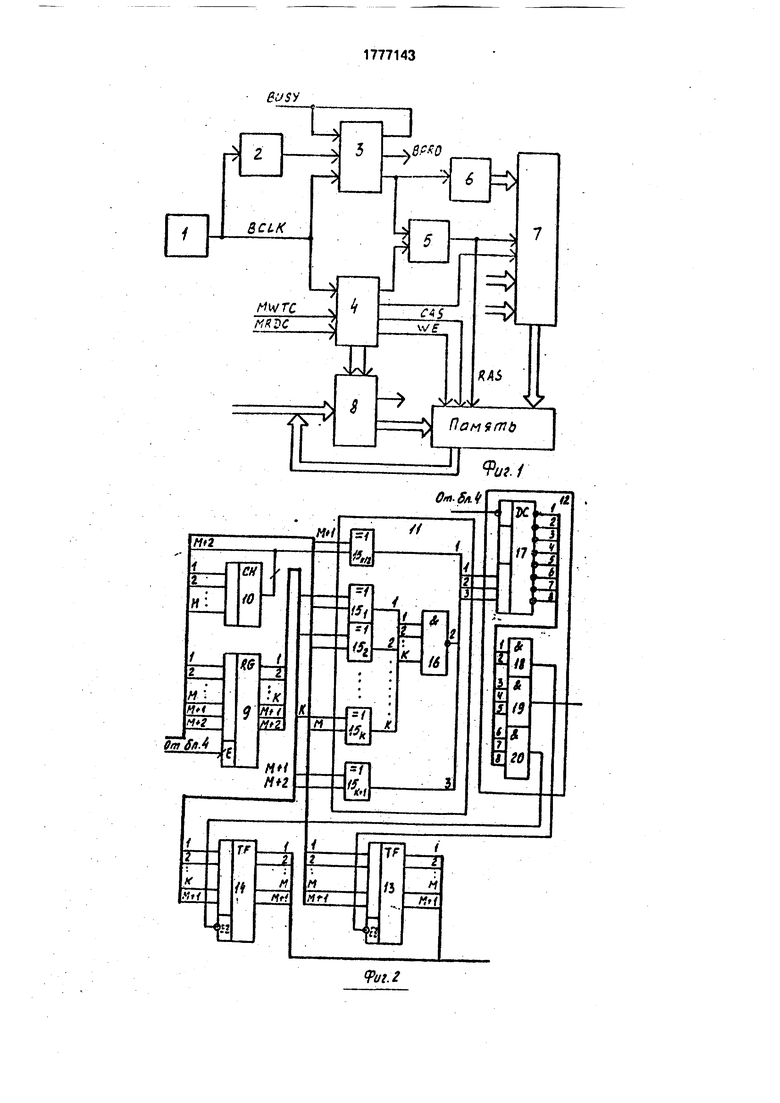

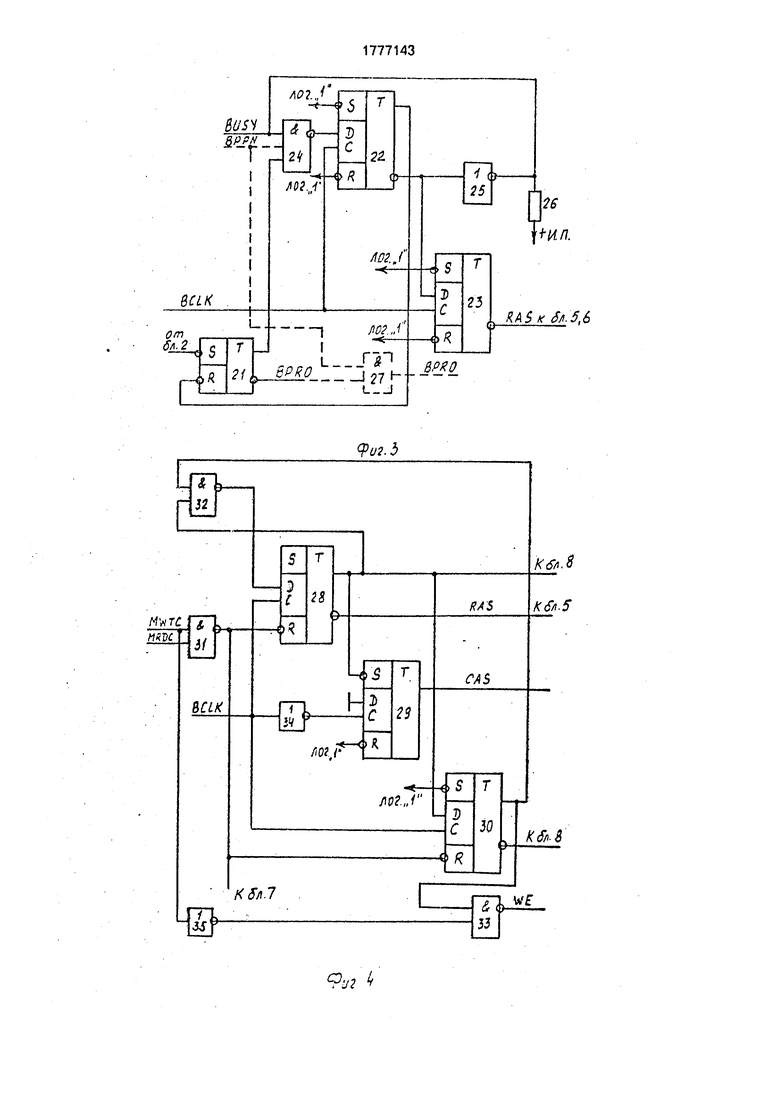

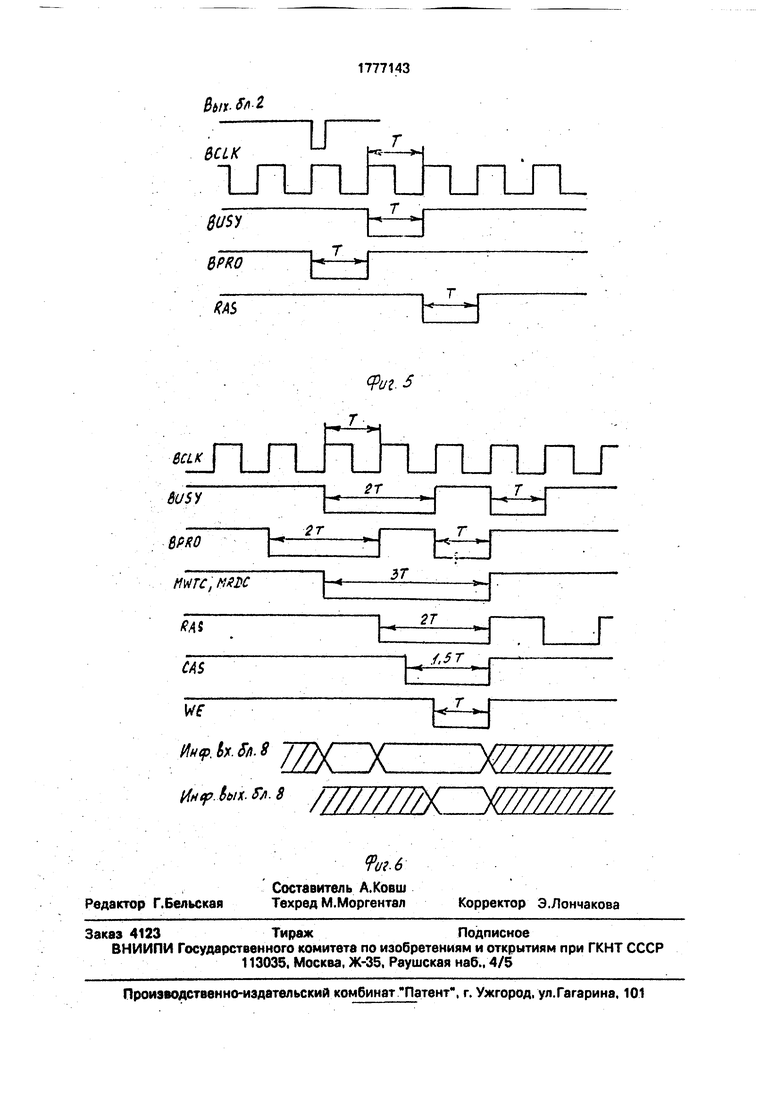

На фиг. 1 приведена структурная схема устройства; на фиг. 2 -функциональная схема блока исправления ошибок: на фиг. 3 - функциональная схема блока управления регенерацией; на фиг. 4 - функциональная схема блока управления обращением к памяти; на фиг. 5 - временная диаграмма ра0 боты устройства в цикле регенерации; на фиг. 6 - временная диаграмма работы устройства в циклах записи и чтения.

Устройство содержит генератор синхроимпульсов 1, подключенный ко входу де5 лителя частоты 2, к третьему входу блока управления регенерацией 3 и к первому входу блока управления обращением к памяти 4, второй и третий входы которого являются входами записи и чтения устройства, пер0 вый выход подключен к первому входу схемы ИЛИ 5, второй вход которой, а также вход счетчика адреса 6, подключены к третьему выходу блока управления регенерацией 3, второй выход которого является выходом

5 последовательного приоритета устройства, а первый подключен к первому входу блока управления регенерацией 3 и является входом-выходом признака занятости магистрали устройства, выход схемы ИЛИ 5 является

0 выходом выбора адреса строки устройства и подключен ко второму управляющему входу мультиплексора 7, первый управляющий вход которого подключен ко второму выходу блока управления обращением к памяти 4,

5 третий выход которого является выходом выбора адреса столбца устройства, четвертый - выходом управления записью устройства, а выход синхронизации приема и выход синхронизации выдачи информации,

0 соответственно, - к первому и второму син- хровходам блока исправления ошибок 8, ин- формационный вход и информационный выход блока исправления ошибок подключены к информационному входу и информа5 ционному выходу устройства, выход индикации неустранимой ошибки блока исправления ошибок 8 подключен к выходу индикации ошибки устройства, выход делителя частоты 2 подключен ко второму входу

0 блока управления регенерацией 3, первый, второй, третий информационные входы и выход мультиплексора 7 подключены, соответственно, к выходу счетчика адреса б, входу адреса строки, входу адреса столбца и к

5 выходу устройства.

Блок исправления ошибок 8 содержит регистр 9, узел контроля четности 10, схему сравнения 11, дешифратор 12 и два коммутатора, причем М разрядов информационного входа блока исправления ошибок 8

подключены ко входу узла контроля четности 10. М разрядам информационного входа регистра 9, М разрядам первого входа схемы сравнения 11 и М разрядам информационного Влода первого коммутатора 13, где М - разрядность информации, К-й разряд выхода регистра 9 подключен к К-м разрядам второго входа схемы сравнения 11 и второго коммутатора 14, М+1-й выход регистра 9 подключен к М+1-м разрядам второго входа схемы сравнения 11 и второго коммутатора 14, М+1-й разряд информационного входа блока исправления ошибок 8 подключен к М+2-му разряду второго входа схемы сравнения 11 и М+1-м разрядам информационных входов первого коммутатора 13 и регистра 9. М+2-й выход регистра 9 подключен к М+1-му разряду первого входа схемы сравнения 11, М+2-й разряд информационного входа регистра 9 подключен к выходу узла контроля четности 10 и соединен с М+2-м разрядом первого входа схемы сравнения 11, выход схемы сравнения 11 подключен к информационному входу дешифратора 12, первый, второй и третий выходы которого подключены, соответственно, к выходу индикации неустранимой ошибки блока исправления ошибок 8, стро- бирующим входам первого 13 и второго 14 коммутаторов, выходы которых подключены к информационному выходу блока исправления ошибок 8, первый и второй синхровходы блока исправления ошибок 8 подключены, соответственно, к синхровхо- ду регистра 9 и стробирующему входу дешифратора 12.

Схема сравнения 11 (фиг. 2) содержит М+2 схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 151...15к, 15к+1.15к+2. схему И-НЕ 16, причем выходы схем 15i...15K подключены ко входам схемы l/l-HE 16, а выходы схем . 15к+2 16 подключены ко входам дешифратора 12.

Дешифратор 12 (фиг. 2) содержит дешифратор 3x8 17 и три схемы И 18, 19. 20.

Блок управления регенерацией 3 (фиг. 3) содержит R-S-триггер 21, первый 22 и второй 23 D-триггеры, схему И-НЕ 24, инвертор 25, резистор 26. Блок 3 может в общем случае содержать схему И 27 (на фиг, 3 выделена штриховой линией).

Блок управления обращением к памяти 4 (фиг. 4) содержит первый 28, второй 29, трети 30 D-триггеры, первую 31, вторую 32 и третью 33 схемы И-НЕ, первый 34 и второй 35 инверторы.

Устройство работает следующим образом.

Делитель частоты 2 определяет временные циклы регенерации путем деления поступающей на его вход тактовой частот;- BCLK с генератора синхроимпульсов 1 на постоянный коэффициент. Этот коэффициент определяется типом памяти и частотой 5 генератора синхроимпульсов 1. Сигнал с делителя частоты 22, являющийся запросом на регенерацию, поступает на второй вход блока управления регенерацией 3. которым является S-вход триггера 21 (фиг. 3). Триггер

0 21 устанавливается в состояние логической единицы, которая поступает на вход элемента 24 И-НЕ.

Если сигнал BUSY, поступающий на один из входов элемента И-НЕ 24, находит5 ся в состоянии логической единицы, то это означает, что магистраль свободна.

Каждое активное устройство, работающее с динамической памятью, имеет свой сигнал BUSY. Эги сигналы, как правило,

0 формируются элементом с открытым коллектором. Таким элементом в устройстве является элемент НЕ 25. Сигнал BUCY, сформированный а помощью резистора 26, объединяется с сигналами BUSY всех дру5 гих активных устройств. В случае, если сигнал находится в состоянии логической единицы и установлен в логическую единицу триггер 21, на информационный вход триггера 22 подается потенциал логическо0 го нуля, который по переднему фронту сигнала с выхода генератора 1 устанавливает триггер 22 в состояние логического нуля, что приводит к сбросу триггера 21 в состояние логического нуля. На инверсном выходе

5 триггера 21 вырабатывается импульс, который является выходным сигналом последовательного приоритета для организации механизма синхронизации в работе активных устройств на магистрали. Входной сиг0 нал последовательного приоритета в устройстве отсутствует, так как оно имеет наивысший приоритет. Иначе этот сигнал должен быть заведен на элемент 24 И-НЕ, который в этом случае должен быть трехвы5 водным, а выходной сигнал последовательного приоритета снимается с выхода введенного элемента И 27, на входе которого подаются сигнал с инверсного выхода триггера 21 и выходной сигнал последова0 тельного приоритета BPRN. Установка триггера 22 в состояние логического нуля приводит к снятию сигнала BUSY и, таким образом, следующий передний фронт синхроимпульса генератора 1 возвратит триггер

5 22 в состояние логической единицы, а триггер 23 установит в состояние логической единицы благодаря связи инверсного выхода триггера 22 с информационным входом триггера 23. Длительность сигнала RAS, снимаемого с выхода триггера 23, также

равна длительности одного периода синхроимпульса генератора 1 (фиг, 5).

Рабочий цикл начинается в случае появления на входе устройства одного из сигналов: записи (MWTC) или чтения (MRDS) (фиг. 6). В этом случае снимается сигнал со входов установки о ноль триггеров 28, 30, блокирующий эти триггеры. Первый передний фронтсинхроимпульса генератора 1 установит триггер 28, вырабатывающий сигнал RAS в состояние логической единицы. Благодаря обратной связи с выходов триггеров 28, 30, осуществляемой через элемент И- НЕ 32 на вход триггера 28, длительность сигнала RAS, снимаемого с инверсного выхода триггера 28, составляет 2 периода синхроимпульсов генератора 1, Сигнал с прямого выхода триггера 28 поступает на вход записи регистра 9 (фиг. 2) блока исправления ошибок 8. Сигнал управления памятью CAS начинает вырабатываться по заднему фронту синхроимпульсов генератора 1 через 0,5 периода после установки в состояние логической единицы триггера 28, снимающего блокировку с установочного входа триггера 29; а снимается сигнал CAS одновременно с сигналом RAS. Таким образом, длительность сигнала CAS составляет 1,5 периода синхроимпульсов генератора 1 (фиг. 6). Сигнал записи в память WE формируется элементом И-НЕ 33. Так как триггер 30 установится через один период после установки триггера 28 благодаря связи с прямого выхода триггера 28 на D-вход триггера 30, то длительность сигнала записи в память WE составляет один период частоты генератора 1 (при длительности сигналов записи MWTC и чтения MRDS, равной трем периодам частоты генератора 1).

Блок исправления ошибок 8 работает следующим образом (фиг. 2). Информация с шины данных магистрали, состоящая из М информационных разрядов и (М+1)-го контрольного разряда, а также (М+2)-й контрольный разряд, сформированный на схеме контроля четности 10, записываются в регистр 9 по сигналу с ьыхода синхронизации приема информации блока управления обращением к памяти 4. Через один период частоты генератора 1 по сигналу с выхода синхронизации выдачи информации блока управления обращением к памяти 4 разрешается работа дешифратора 12. На входы дешифратора 12 подается три разряда с блока сравнения 11, первый из-которых является результатом сравнения (М+1)-го и (М+2)-го контрольных разрядов, второй - результатом сравнения М информационных разрядов, третий - результатом сравнения (М+1) и (М+2) контрольных разрядов, зафик-

сированных в регистре 9. В результате сравнения могут возникнуть восемь различных результатов, соответствующих восьми выходам дешифратора 17. Описание возможных ситуаций и выполняемая дешифратором 12 функция приведены в таблице.

Таким образом, в результате введения блока исправления ошибок 8, не уменьшая

0 быстродействия устройства, увеличивается достоверность записываемой в память информации. Это достигается разнесением во времени моментов предварительной фиксации информации, включающей контроль5 ные разряды, и сравнения информации, находящейся на шине данных по истечение некоторого времени и той, которая зафиксирована предварительно. Все эти операции, а также анализ результатов сравнения и

0 принятие решения по записи информации осуществляет блок исправления ошибок 8, управляемый сигналами блока управления обращением к памяти 4. На фиг. 2 приведен пример блока сравнения 11, выполненный

5 для случая передачи по шине прямых и инверсных кодов, что должно быть обеспечено устройством - источником информации (фиг. 6). Если источник информации не обеспечивает переключение информации с ин0 версной на прямую или наоборот в течение действия сигнала записи MWTC, то схема сравнения 11 должна быть выполнена обычным способом, например, на микросхемах 155СП1. Соответственно передатчики 13 и

5 14 выполняются с инверсией или без нее.

Применение предложенного устройства повышает достоверность функционирования устройства, не уменьшая быстродействия, что позволяет значительно

0 повысить эффективность работы устройств, использующих динамическую память, например, транспортных станций ЛВС. Формула изобретения 1. Устройство управления динамиче5 ской памятью по аат. св. № 1115121, отличающееся тем, что, с целью повышения достоверности функционирования, в него введен блок исправления ошибок, причем первый и второй синхровходы блока исп0 равления ошибок подключены соответственно к выходу синхронизации приема информации и к выходу синхронизации выдачи информации блока управления обращением к памяти, информационные вход и

5 выход блока исправления ошибок подключен соответственно к информационному входу и выходу устройства, выход индикации неустранимой ошибки блока исправления ошибок подключен к выходу индикации ошибки устройства.

2. Устройство по п.1. о т л и ч а ю щ е е- с я тем. что блок исправления ошибок содержит регистр, узел контроля четности, схему сравнения, дешифратор и два коммутатора, причем М разрядов информационного входа блока подключены к входу узла контроля четности, М разрядам информационного входа регистра, М разрядам первого входа схемы сравнения и М разрядам информационного входа первого коммутатора (где М - разрядность информации), К-й разряд выхода регистра подключен к К-м разрядам второго входа схемы сравнения и второго коммутатора (, М+1), (М+1)-й разряд информационного входа блока подключен к (М+2)-му разряду второго входа схемы сравнения и (М+1)-м разрядам информационных входов первого коммутатора и регистра. (1И+2)- й выход регистра подключен к (М+ 1)-му разряду первого входа схемы сравнения, (М+2)-й разряд информационного входа регистра подключен к выходу узла контроля четности и соединен с (М+2)-м разрядом первого входа схемы сравнения, выход схемы сравнения подключен к информационному входу дешифратора, первый, второй и

третий выходы которого подключены соответственно к выходу индикации неустранимой ошибки блока, стробирующим входам первого и второго коммутаторов, выходы которых подключены к информационному входу блока, первый и второй синхровходы блока подключены соответственно к синх- ровходу регистра и стробирующему входу дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для контроля памяти | 1982 |

|

SU1020865A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1580442A1 |

| Система управления технологическим процессом дискретного производства | 1984 |

|

SU1251110A1 |

Изобретение относится к вычислительной технике, в частности к устройствам управления оперативными запоминающими устройствами динамического типа. Цель изобретения - повышение достоверности функционирования. Устройство содержит генератор синхроимпульсов, делитель частоты, блок управления обращением к памяти, схему ИЛИ, счетчик адреса, мультиплексор, блок исправления ошибок. Устройство позволяет исправлять одиночные и обнаруживать многократные ошибки при записи информации в память. 6 ил.

Выход дешифратора17

Описание события

Совпала информация, совпали вторые контрольные разряды, первые контрольные разряды не совпали

Совпали вторые контрольные разряды, не совпала информация и первые контрольные разряды

Не совпала информация, первые и вторые контрольные разряды

Совпали первые и вторые контрольные разряды, не совпала информация

Совпала информация, не совпали первые и вторые контрольные разряды

Совпала информация, первые и вторые контрольные разряды

Совпала информация, первые контрольные разряды, не совпали вторые контрольные разряды

Совпали первые контрольные разряды, не совпала информация и вторые контрольные разряды

Выполняемая функция

Подключение к памяти передатчика 13

Подключение к памяти передатчика 13

Индикация ошибки

Индикация ошибки

Индикация ошибки

Подключение к памяти передатчика 14

Подключение к памяти передатчика 14

Подключение к памяти передатчика 14

JMJ

BUK

:

21,

I

1

L Q

(I

D

3

4i

гз

e«/f

/. 7

9

5

Г

+кп.

23

.5,6

BPKQ

.b

/TeCr.5

4Ј

hf

X5

S

Т с

30

&

WE

fan. 6

миге,

kf

. Јх Л. Ј

Put 5

зт

«-I-.

W//////////

| Устройство для гашения электрической дуги | 1982 |

|

SU1115121A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-11-23—Публикация

1990-03-28—Подача