Изобретение относится к вычислительной технике и может быть использовано для подключения ЭВМ к магистрали локальной сети.

Известно устройство для сопряжения абонента с каналом передачи данных 1, содержащее блок усилителей передачи, блок усилителей приема, блок готовности связи, блок приема знака, блок шифрации сигналов передачи данных, блок передачи знака, регистр приема данных и регистр передачи данных.

Недостатками данного устройства являются ограниченность области его применения (1 канал), а также недостаточность достоверности приема информации ввиду отсутствия ее контроля.

Наиболее близким по технической сущности к предлагаемому является устройство для сопряжения ЭВМ с магистралью системы 2, содержащее буферный регистр, дешифратор команд, дешифратор адреса, дешифратор состояния, одновибратор, формирователь импульсов, два шинных формирователя, узел выделения информации, блок управления, коммутатор, задатчик адреса, регистра адреса и генератор импульсов.

Устройство обеспечивает связь между ЭВМ по локальной вычислительной сети. Однако оно не контролирует принимаемую информацию, что не обеспечивает достаточной достоверности приема и расширения области применения.

Целью изобретения является повышение достоверности приема и расширение Области применения.

Цель достигается тем, что устройство для сопряжения магистрали локальной сети с ЭВМ, содержащее блок развязки, буферный регистр, формирователь импульсов, блок выделения информации и первый счетчик, причем вход-выход блока развязки соединены с сетевым входом устройств и с первым входом блока выделения информации, выход которого соединено с входом формирователя импульсов, первый выход которого соединен со счетным входом счетчика, второй выход - с вторым входом блока выделения информации, выходы буферного регистра являются выходами данных устройства, при этом блок выделения информации содержит первый триггер и элемент И, первый вход которого соединен с выходом первого триггера, дополнительно содержит четыре триггера, регистр сдвига, второй счетчик, и блок выделения информации содержит второй, третий и четвертый триггеры и усилитель, причем в блоке выделения информации входы элемента И соединены с

выходами второго и третьего триггеров, син- хровходы которых соединены с выходами усилителя, входы которого являются первым входом блока выделения информации,

установочные входы второго и третьего и синхровход первого триггеров соединены с выходом элемента И, первый выход первого триггера соединен с установочным входом четвертого триггера, выход которого соединен с входом сброса первого триггера, вход данных которого соединен с его вторым выходом, который является выходом блока выделения информации, второй вход которого соединен с синхровходом четвертого триг5 гера, при этом в устройстве выход блока выделения информации соединен с входом данных регистра сдвига, параллельный выход которого соединен с входом данных буферного регистра, синхровход которого

0 соединен с выходом первого счетчика и синхровходом триггера готовности, выход и вход сброса которого являются выходом готовности и входом чтения устройства, второй выход формирователя импульсов

5 соединен с синхровходами второго счетчика регистра сдвига и триггера управления, установочный вход и вход сброса которого соединены с его первым выходом и выходом второго триггера сброса, синхровход кото0 рого соединен с выходом второго счетчика, вход сброса которого и вход сброса второго триггера сброса соединены с выходом первого триггера сброса, синхровход и вход сброса которого являются одноименными

5 входами устройства, а вход данных соединен с выходом одного из разрядов буферного регистра, вход разрешения второго счетчика и вход данных триггера управления соединены с выходами соответствую0 щих разрядов регистра сдвига, а второй выход соединен с входом разрешения первого счетчика.

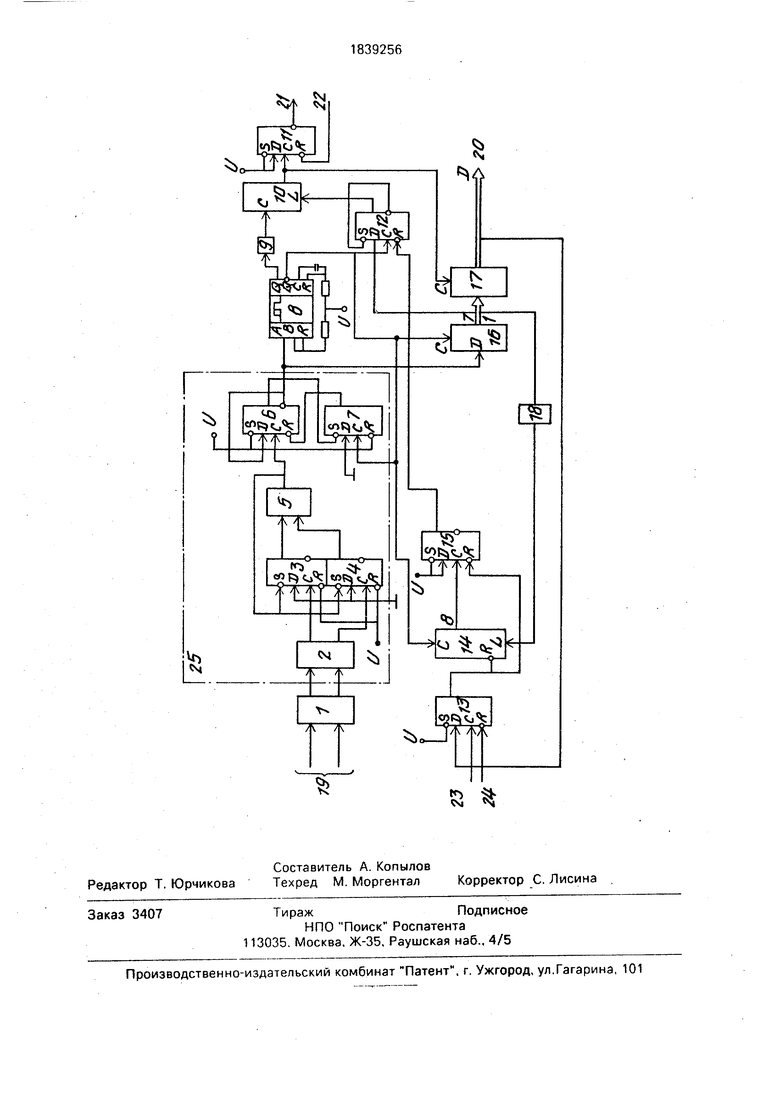

Схема предлагаемого устройства приведена на чертеже содержит блок 1 разряд5 ки, усилитель 2, первый 3 и второй 4 триггеры, элемент И 5, третий 6 и четвертый 7 триггеры, формирователь 8 импульсов, усилитель 9, первый счетчик 10, триггер 11 готовности, триггер 12 управления и первый

0 триггер 13 сброса, второй счетчик 14, второй триггер 15 сброса, регистр 16 сдвига, буферный регистр 17. усилитель 18, вход 19 магистрали локальной сети, выходная шина 20 данных, выход 21 готовности, синхровходы

5 22, 23 чтения, вход 24 сброса, блок 25 выделения информации. Входы и выходы блока 1 соединены с сетевым входом устройства и с первым входом блока 25, выход которого соединен с входом формирователя 8, первый выход которого соединен со счетным

входом счетчика 10, второй выход - с вторым входом блока 25. Выходы буферного регистра 17 являются выходами 20 данных устройства, выход блока 25 соединен с входом данных регистра 16, параллельный вы- ход которого соединен с входом данных буферного регистра 17. Синхровход последнего соединен с выходом счетчика 10 и синхровхрдом триггера 11, выход и вход сброса которого являются выходом 21 го- товности и входом 22 чтения устройства. Второй выход формирователя 8 соединен с синхровходами счетчика 14, регистра 16 и триггера 12, установочный вход и вход сброса которого соединены с его первым выхо- дом и выходом триггера 15, Синхровход триггера 15 соединен с выходом счетчика 14, вход сброса которого и вход сброса триггера 15 соединен с выходом триггера 13. Синхровход 23 и вход 24 сброса триггера 13 являются одноименными входами устройства, а вход данных соединен с выходом одного из разрядов буферного регистра 17, Вход разрешения счетчика 14 и вход да иных триггера 12 соединены с выходами соответству- ющих раз рядов регистра 16, а второй выход триггера 12 соединен с входом разрешения счетчика 10. В блоке 25 выделения информации входы элемента И 5 соединены с выходами триггеров 3 и 4, синхровходы которых соединены с выходами усилителя 2, входы которого являются первым входом блока 25. Установочные входы триггеров 3, 4 и Синхровход триггеров соединены с выходом элемента И 5, первый выход триггера 6 соединен с установочным входом триггера 7, выход которого соединен с входом сброса триггера 6. Вход данных триггера 6 соединен с его вторым выходом, который является выходом блока 25, второй вход которого соединен с синхровходом триггера 7.

Блок 1 развязки представляет собой трансформатор. Триггеры 3, 4, 11,12,13, 15 выполнены на микросхемах типа 555ТМ2, элемент И 5 изготовлен на микросхеме 555ЛИ1, а триггеры 6 и 7 - на микросхемах 531ТМ2. Формирователь 8 выполнен на микросхемах 155АГЗ, усилитель 9 - на микросхемах 555ЛИ1. Счетчики 10 и 14 выполнены на микросхемах типа 555ИЕ10, а регистры 16 и 17 - на микросхемах типа 53ИР24 и 555ИР23 соответственно. Усилитель 18 изготовлен на микросхемах 531ЛП5.

Устройство работает следующим образом.

Устройство предназначено для приема сигналов из магистрали локальной сети, выделения из этих сигналов преамбулы, информационных сигналов и импульсов синхронизации, формирования кода данных требуемого формата и выдачи его в ЭВМ. В магистрали локальной сети данные закодированы с помощью кода DF (двойная частота). Блок 1 осуществляет развязку между магистралью локальной сети и устройством сопряжения и может быть выполнен в виде трансформатора. Поступившие из локальной сети через блок 1 сигналы усиливаются усилителем 2 и поступают на блок 25 выделения информации, который преобразует код DF в данные. С выхода блока 25 сигналы поступают на формирователь 8, который на своих прямом и инверсном выходах формирует синхроимпульсы, которые управляют формированием выходного кода.

Вначале поступает преамбула, состоящая из восьми нулей, очищающих регистр 16 сдвига, а затем стартовая 1, которая записывается в первый разряд регистра 16 сдвига по синхроимпульсу с инверсного выхода формирователя 8, при этом устанавливается триггер 12, разрешающий работу счетчика 10, который считает импульсы с прямого выхода формирователя 8, Сосчитав заданное число импульсов, он устанавливает триггер 11, с выхода которого сигнал готовности поступает в ЭВМ. Поступающие затем разряды данных с выхода блока 25 преобразуются в регистре 16 в параллельный код и при этом каждый раз прибавляется 1 в счетчик 14, который считает до восьми и устанавливает затем триггер 15, который сбрасывает триггер 12. По заполнении регистра 16 сдвига на его выходе формируется сигнал, запрещающий работу счетчика 14, а с выхода счетчика 10 поступает сигнал, разрешающий запись содержимого регистра 16 сдвига в буферный регистр 17, с выхода которого данные поступают на шину данных ЭВМ. Сигнал записи, поступающий на вход 23 из ЭВМ, устанавливают триггер 13, с выхода которого сигнал сброса поступает на счетчик 14 и триггер 15, подготавливая устройство к приему очередной порции данных.

(56) Авторское свидетельство СССР № 1490677,кл. G 06 F13/00, 1989.

Авторское свидетельство СССР Ns 1487052,кл. G 06 F13/00, 1989,

Формула изобретения

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ МАГИСТРАЛИ ЛОКАЛЬНОЙ СЕТИ С ЭВМ, содержащее блок развязки, буферный ре- гистр, формирователь импульсов, блок выделения информации и первый счетчик, причем вход и выход блока развязки соединены с сетевым входом устройства и с первым входом блока выделения информа- ции. выход которого соединен с входом формирователя импульсов, первый выход которого соединен со счетным входом счетчика, второй выход формирователя импульсов соединен с вторым входом блока выделения информации, выходы буферного регистра являются выходами данных устройства, при этом блок выделения информации содержит первый триггер и элемент 14, первый вход которого соединен с выходом первого триггера, отличающееся тем, что, с целью повышения достоверности приема и расширения области применения, оно содержит четыре триггера, регистр сдвига, второй счетчик, а блок выделения информации содержит второй, третий и четвертый триггеры и усилитель, причем в блоке выделения информации второй вход элемента И соединен с выхо- дами второго триггера, синхроаходы первого и второго триггеров соединены с выходами усилителя, входы которого являются первым входом блока выделения информации, установочные входы первого и второго и синхровход третьего триггеров соединены с выходом элемента И, первый

15

5 20 25 30 35

выход третьего триггера - с установочным входом четвертого триггера, выход которого соединен с входом сброса третьего триггера, вход данных которого соединен с его вторым выходом, который является выходом блока выделения информации, второй вход которого соединен с синхровходом четвертого триггера, при Этом в устройстве выход блока выделения информации соединен с входом данных регистра сдвига, параллельный выход которого соединен с входом данных буферного регистра, синхровход которого соединен с выходом первого счетчика, и синхровходом триггера готовности, выход и вход сброса которого являются выходом готовности и входом чтения устройства, второй выход формирователя импульсов соединен с синхровходами второго счетчика, регистра сдвига и триггера управления, установочный вход и вход сброса которого соединены с его первым выходом и выходом второго триггера сброса, синхровход которого соединен с выходом второго счетчика, вход сброса которого и вход сброса второго триггера сброса соединены с выходом первого триггера сброса, синхровход и вход сброса которого являются одновременно входами устройства, а вход данных соединен с выходом одного из разрядов буферного регистра, вход разрешения второго счетчика и вход данных триггера управления соединены с выходами соответствующих разрядов регистра сдвига, а второй выход соединен с входом разрешения первого счетчика.

5

EH N

3

/4Y

5

A

1

fcj | OftVj«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для ввода изображения в ЭВМ | 1986 |

|

SU1432494A1 |

| Устройство для сопряжения абонента с каналом связи | 1989 |

|

SU1667088A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Многоканальное устройство для сопряжения ЭВМ с последовательными линиями связи | 1990 |

|

SU1839259A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Устройство для сопряжения ЭВМ с каналом передачи данных | 1989 |

|

SU1647580A1 |

| Устройство для управления вводом изображения | 1989 |

|

SU1751738A1 |

| Устройство для сопряжения с линией связи | 1983 |

|

SU1118998A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1990 |

|

SU1839257A1 |

Устройство для сопряжения магистральной локальной сети и ЭВМ относится к вычислительной технике. Цепь изобретения - повышения достоверности приема и расширения области применения Устройство содержит блок развязки, буферный регистр, формирователь импульсов, блок выделения информации, содержащий четыре триггера и усилитель, первый и второй счетчики и регистр сдвига 1 ил.

Авторы

Даты

1993-12-30—Публикация

1990-06-29—Подача