Изобретение относится к вычислительной технике и может быть использовано для подключения ряда последовательных линий к ЭВМ.

Известно устройство для сопряжения ЭВМ с абонентом 1, содержащее два блока канальных приемников, блок канальных приемопередатчиков, блок шифрации управляющих сигналов, блок преобразования параллельного кода в последовательный и обратно, буферный регистр, генератор синхроимпульсов, коммутатор режима, регистр режима, регистр адреса вектора прерывания, мультиплексор данных и блок прерывания. Однако область использования этого устройства ограничена.

Наиболее близким к предлагаемому по технической сущности является устройство для сопряжения абонентов в многоканальном комплексе 2, содержащее генератор тактовых импульсов, четыре счетчика, три элемента НЕ, шесть триггеров, мультиплексор два в один, мультиплексор шестнадцать в один, схему сравнения, элемент ИЛИ, два элемента И-НЕ, три элемента И, переклю- чатель, галетный переключатель, переключатель Номер абонента, схему сравнения кодов, универсальный асинхронный передатчик, передающий оптрон, приемный оп- трон и нагрузочные резисторы, Схема известного устройства достаточно сложная, а область использования ограничена.

Целью изобретения является упрощение устройства при одновременном расширении области применения.

Цель достигается тем, что многоканальное устройство для сопряжения ЭВМ с последовательными линиями связи, содержащее селектор адреса, генератор

импульсов, делитель частоты, а в каждом

канале универсальный асинхронный приемопередатчик, приемный оптрон, передающий оптрон, два триггера, причем выход передающего оптрона и вход приемного оп- трона являются линейными выходом и вхо- дом соответствующего канала устройства, выход генератора импульсов соединен с тактовым входом делителя частоты, содержит блок перемычек, регистр адреса, дешифратор, два блока шинных формирователей и восемь усилителей, причем первый вход-выход первого по пятый усилителей и выходы шестого и седьмого усилителей соединены соответственно с первым и вторым входами данных, сброса, строба адреса, строба данных, чтения и первым и вторым выходами запросов прерываний устройства, второй вход-выход первого блока шинных формирователей соединен с входом данных селектора адреса, парал0 5

0 5 0

5

0

5 0 5

лельными входами данных универсальных асинхронных приемопередатчиков всех каналов и выходом второго блока шинных формирователей, синхровход селектора адреса соединен с выходом первого усилителя, выход второго усилителя соединен с входами сброса регистра -адреса и универсальных асинхронных приемопередатчиков, всех каналов, в каждом канале последовательный выход данных универсального асинхронного приемопередатчика через восьмой усилитель соединен с входом передающего оптрона, последовательный вход данных - с выходом приемного оптрона, а выходы приема и выдачи - с синхров- ходами первого и второго триггеров, установочные входы которых соединены с первым и вторым выходами дешифратора, третий выход которого соединен с управляющим входом первого блока шинных формирователей, выход селектора адреса соединен с входом данных регистра адреса, синхровход которого и первый вход дешифратора соединены с выходом третьего усилителя, выход регистра адреса соединен с вторым входом дешифратора, третий и четвертый входы которого соединены с выходами четвертого и пятого усилителей, второй выход дешифратора соединен с управляющим входом второго блока шинных формирователей и входами чтения универсальных асинхронных приемопередатчиков всех каналов, входы записи которых соединены с первым выходом дешифратора, а параллельные выходы данных.- с входом данных второго блока шинных формирователей, инверсные выходы первого и второго триггеров соединены с входами шестого и седьмого усилителей, выходы делители частоты соединены с входами блока перемычек, выходы которого соединены с синхровходами универсальных асинхронных приемопередатчиков соответствующих каналов.

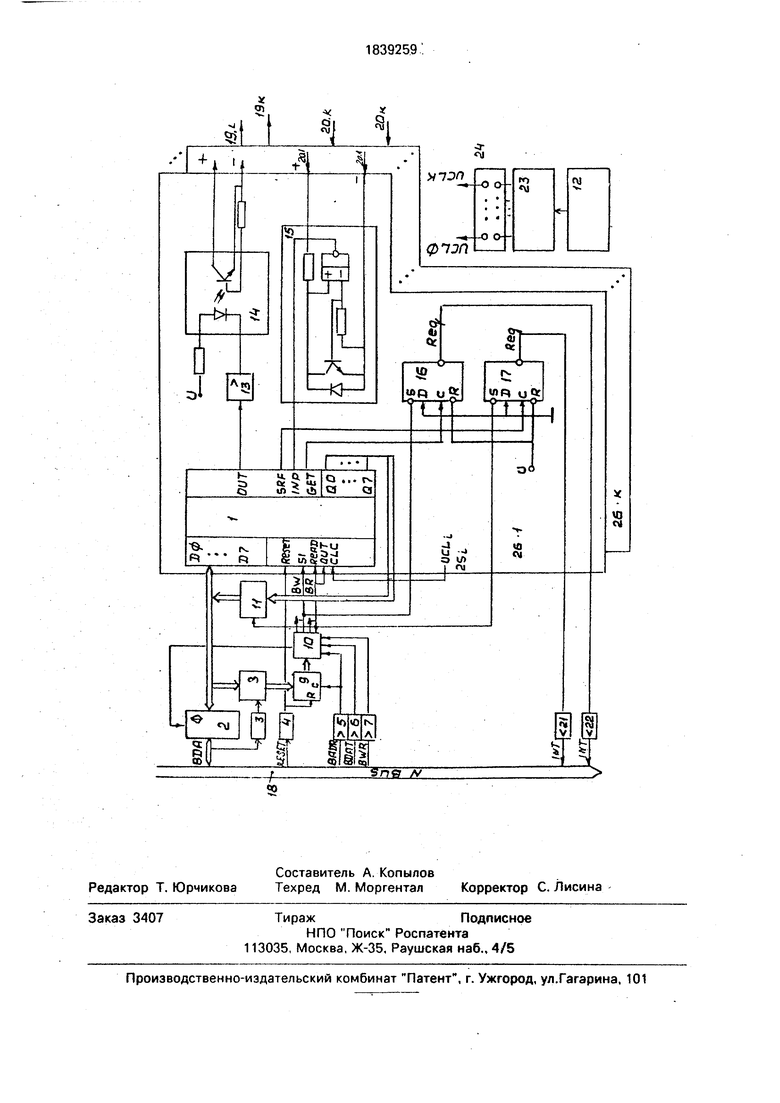

Схема предлагаемого устройства приведена на чертеже.

Устройство содержит универсальный асинхронный приемопередатчик 1, первый блок 2шинных формирователей, с первого по пятый усилители 3-7, селектор 8 адреса, регистр 9 адреса, дешифратор 10, второй блок 11 шинных формирователей, генератор 12 импульсов, восьмой усилитель 13, передающий оптрон 14, приемный оптрон 15, первый 16 и второй 17 триггеры, магистраль 18 ЭВМ, выходная 19 и входная 20 последовательные линии связи (интерфейсы), шестой 21 и седьмой 22 усилители, делитель 23 частоты, блок 24 перемычек, линия 25 синхронизации,каналы 26 устройства. Выход оптрона 14 и вход оптрона 15 являются линейными выходом 19 и входами 20 соответствующего канала устройства, выход генератора 12 соединен с тактовым входом делителя 23 частоты. В каждом ка- нале первый вход-выход блока 2, входы усилителей 3-7 и выходы усилителей 21 и 22 соединены с первым и вторым входами данных, сброса, строба адреса, строба данных, чтения и первым и вторым выходами запро- сов прерываний устройства, второй вход- выход блока 2 соединен с входом данных селектора 8, параллельными входом данных приемопередатчика 1 и выходом блока 11. Синхровход селектора 8 соединен с выхо- дом усилителя 3, выход усилителя 4 - с входами сброса регистра 9 и приемопередатчика 1, последовательный выход данных которого через усилитель 13 соединен с входом оптрона 14, последова- тельный вход данных - с выходом оптрона 15. а выходы приема и выдачи - с синхров- ходами триггеров 16, 17. Установочные входы последних соединены с первыми и вторыми выходами дешифратора 10, третий выход которого соединен с управляющим входом блока 2. Выход селектора 8 соединен с входом регистра 9, синхровход которого и вход дешифратора 10 соединены с выходом усилителя 5. Выход регистра 9 со- единен с вторым входом дешифратора 10, третий и четвертый входы которого соединены с выходами усилителей 6, 7, второй выход- с управляющим входом блока 11 и входом чтения приемопередатчика 1. Вход записи приемопередатчика 1 соединен с первым выходом дешифраторе 10, а параллельный выход данных - с входом данных блока 11. Инверсные выходы триггеров 16, 17 через усилители 21, 22 соединены с вы- ходами запросов прерываний устройства. Выходы делителя 23 частоты соединены с входами блока 24, выходы которого соединены с синхровходами приемопередатчиков 1 соответствующих каналов.

Универсальный асинхронный приемопередатчик выполнен на микросхеме типа 1002ХЛ1, блок 2 шинных формирователей - на микросхемах 531АПЗ. С первого по пятый усилитель 3-7, 13 выполнены на микро- схемах типа 555АПЗ, селектор 8 адреса - на микросхемах 555ЛА1, а регистр 9 адреса - на микросхемах типа 555ТМ9. Дешифратор ТО выполнен на микросхемах 555ИД7, блок 11 шинных формирователей - на микросхе- мах555АП4, триггеры 16, 17 - на микросхемах типа 555ТМ2. Усилители 21, 22

выполнены на микросхемах типа 559ИП1, а делитель 23 частоты, состоящий из двух последовательно соединенных счетчиков, выполнен на микросхемах типа 555ИЕ10.

Прием и передачу данных в каждом канале 26 проводит блок 1 (микросхема 1002ХЛ1). Оптронные развязки 14 и 15 на входе и выходе каждого канала 26 обеспечивают полную изоляцию интерфейсов 19, 20 от внешних устройств при работе в режиме RS-232C. Наличие на внешних разъемах напряжений +12 и -12 В позволяет с помощью несложной внешней коммутации организовать интерфейс V-24.

Делитель 23 частоты осуществляет деление на число от 1 до 16, а затем на два в степени 2...5. Перемычками блока 24 выбирается необходимая частота каждого интерфейса.

По окончании приема или передачи байта данных одним из каналов взводится соответствующий триггер 16 или 17 запроса, который сбрасывается циклом чтения или записи этого канала.

Блок 11, включающийся в цикле чтения последовательных линий, обеспечивает преобразование уровней из КМОП в ТТЛ.

Работает устройство следующим образом,

В исходном состоянии от ЭВМ на вход усилителя 4 поступает сигнал Сброс, который сбрасывает регистр 9 адреса и приемопередатчик 1. Обмен информации начинается с цикла адресации, С приходом сигнала BADR в случае опознания селектором 8 адреса одного из разрешенных адресов данного устройства указанный адрес записывается в регистр 9. Дешифратор 10 по коду .адреса, записанному в регистр 9, выдает один из управляющих сигналов, выбирая один из каналов 26.1-26.16 связи.

По окончании цикла адресации происходит обмен данными через приемопередатчик 1 соответствующего канала с выбранной линией связи в соответствии с управляющими сигналами, поступившими на входы усилителей 6 и 7, т.е. прием данных из линии в ЭВМ либо выдача данных из ЭВМ в соответствующую линию связи. Цикл обмена фиксируется установкой одного из триггеров 16 или 17. По окончании обмена триггер 16(17) сбрасывается.

(56) Авторское свидетельство СССР № 1334154,кл, G 06 F13/24, 1987.

Авторское свидетельство СССР Me 1522222,кл. G 06 F13/10, 1989.

Формула изобретения

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ПОСЛЕДОВАТЕЛЬНЫМИ ЛИНИЯМИ СВЯЗИ, содержащее селектор адреса, генератор импульсов, делитель частоты, а в каждом канале - универсальный асинхронный приемопередатчик, приемный и передающий оптроны, два триггера, причем выход передающего и вход приемного оптронов являются линейными выходом и входом соответствующего канала устройства, выход генератора импульсов соединен с тактовым входом делителя частоты, отличающееся тем, что, с целью упрощения устройства и расширения области применения, оно содержит блок перемычек, регистр адреса, дешифратор, два блока шинных формирователей и восемь усилителей, причем первый вход-выход первого блока шинных формирователей, входы с первого по пятый усилителей и выходы шестого и седьмого усилителей соединены соответственно с первым и вторым входами данных, сброса, строба адреса, строба данных, чтения и первым и вторым выходами запросов прерываний устройства, второй вход-выход первого блока шинных формирователей соединен с входом данных селектора адреса, параллельными входами данных универсальных асинхронных приемопередатчиков всех каналов и выходом второго блока шинных формирователей, синхровход селектора адреса соединен с выходом первого усилителя, выход второго усилителя соединен с входами сброса регистра адреса и универсальных асинхронных приемопередатчиков всех каналов, причем в каждом канале последовательный выход данных универсального асинхронного приемопередатчика

через восьмой усилитель соединен с входом передающего оптрона, последовательный вход данных - с выходом приемного оптрона, а выходы приема и выдачи - с синхровходами первого и второго триггеРОВ, установочные входы которых соединены с первым и вторым выходами дешифратора, третий выход которого соединен с управляющим входом первого блока шинных формирователей, выход

селектора адреса соединен с входом данных регистра адреса, синхровход которого и первый вход дешифратора соединены с выходом третьего усилителя, выход регистра адреса соединен с вторым входом дешифратора, третий и четвертый входы которого соединены с выходами четвертого и пятого усилителей, второй выход дешифратора соединен с управляющим входом второго блока шинных формирователей и входами чтения универсальных асинхронных приемопередатчиков всех каналов, входы записи которых соединены с первым выходом дешифратора, а параллельные выходы данных - с входом данных второго блока шинных формирователей, инверсные выходы первого и второго триггеров соединены с входами шестого и седьмого усилителей, выходы делителя час стоты соединены с входами блока перемычек, выходы которого соединены с синхровходами универсальных асинхронных приемопередатчиков соответствующих

каналов.

0

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для ввода-вывода информации | 1988 |

|

SU1587520A1 |

| Устройство управления вводом-выводом | 1990 |

|

SU1839254A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1990 |

|

SU1839257A1 |

| Устройство для сопряжения двух магистралей | 1987 |

|

SU1418728A1 |

| Устройство для обмена информацией между персональной ЭВМ и управляющим вычислительным комплексом | 1991 |

|

SU1838819A3 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

Устройство относится к вычислительной технике и используется для подключения ряда последовательных линий связи к ЭВМ. Цель изобретения - упрощение устройства и расширение области его применения Согласно изобретению устройство содержит селектор адреса, генератор импульсов, де-. литель частоты, асинхронный приемопередатчик, приемный и передающий оптроны, два триггера, блок перемычек, регистр адреса, дешифратор, два блока шинных формирователей и восемь усилителей. 1 ид

Авторы

Даты

1993-12-30—Публикация

1990-06-28—Подача