Изобретение относится к вычислитель- ной технике и может быть использовано в системах технического зрения для управления вводом видеоинформации в ЭВМ

Известен блок управления в устройстве для ввода изображения в электронную вычислительную машину, содержащий блок управления сканированием,интенсивностью и апертурой электронного луча. Формирователи сигналов управляющих перестройкой апертуры, блок управления режимом перестройки апертуры, включающий схему сравнения и два ключа, формирователь управляющих сигналов, два регулируемых источника тока и двухпозиционный переключатель

Недостатки этого устройства - сложность, невысокая надежность за счет низкой помехозащищенности и возможности сбоев в работе при преобразовании аналогового сигнала в дискретный код и записи в оперативную память

Известен также блок управления в устройстве для сопряжения цифровой вычислительной машины с устройством ввода изображений содержащий два входных регистра, блок дешифрации команд, выполненный на программируемой логической матрице, буферную память микрокоманд, выходной регистр, регистр управления, регистру текущего адреса и следующего адреса, узлы управления обменом и блок распределения синхроимпульсов.

Данное устройство характеризуется сложностью, низкой помехозащищенностью, ограниченными функциональными возможностями.

Наиболее близким к предлагаемому техническим решением является блок управления с формирователем импульсов в устройстве для ввода изображения в ЭВМ, содержащий счетчик бит, три элемента НЕ, четыре элемента И-НЕ, четыре элемента ИЛИ-НЕ, три триггера, формирователь импульсов, включающий узел задержки, ждущий мультивибратор, усилитель, триггер, элемент ИЛИ-НЕ, два формирователя фронта, причем вход узла задержки является входом запуска формирователя, а выход является первым выходом формирователя и подключена к входу ждущего мультивибратора, выход которого соединен с входом

(Л

С

х| ел

ы

00

силителя, первого формирователя фронта синхровходов триггера, установочный ход которого соединен с единичным выхоом триггера и четвертым выходом формиователя, выход усилителя является вторым 5 ыходом формирователя, выход первого ормирователя фронта соединен с первым входом элемента ИЛИ-НЕ, второй вход коорого является разрешающим входом форирователя, а выход является третьим 10 выходом формирователя.

Недостатками известного устройства являются сложность, невысокая надежность из-за низкой помехозащищенности, бусловленной возможными сбоями в рабо- 15 е устройства, и ограниченные функциональные возможности. Сбои в работе устройства могут возникнуть при разбросе параметров RC-цепей, на базе которых организованы сигналы записи информации, 20 выборки, смены адреса. Устройство также дает сбои в работе, если увеличивается тактовая частота от телекамеры, например 10 мГц вместо 5.,

Цель изобретения - повышение поме- 25 хозащииценности.

Поставленная цель достигается тём, что устройство, содержащее первый, второй, третий элементы НЕ, первый, второй, четвертый и пятый элементы И-НЕ, первый, 30 второй и третий элементы ИЛИ-НЕ, второй и третий элементы ИЛИ, первый, второй, третий и четвертый триггеры, формирователь импульсов, элемент задержки, счетчик, выход переполнения которого соединен с 35 входом элемента задержки, выход которого является выходом строба перезаписи устройства, причем первый вход пятого элемента И-НЕ является входом сигнала Синхронизация активного устройства, С- 40 входы второго триггера являются соответственно входами сигналов Первый разряд и Вывод, а инверсный выход второго триггера соединен с вторым входом пятого элемента И-НЕ, первым входом третьего 45 элемента ИЛИ-НЕ и первым входом второго элемента ИЛИ-НЕ, второй вход и выход которого соединен соответственно с выходом первого триггера и с первым входом четвертого элемента И-НЕ, выход которого 50 является выходом тактовой частоты а второй, третий и четвертый входы четвертого элемента И-НЕ соединены соответственно с выходами первого, второго и третьего элемента НЕ, вход которого является входом 55 для подключения сигнала гашения шины телекамеры и соединен с первыми входами первого элемента ИЛИ-НЕ и первого элемента И-НЕ, выход которого является выходом сигнала Счет строк, а второй вход

первого элемента И-НЕ соединен с выходом второго триггера, входом формирователя импульсов, первым входом второго элемента И-НЕ, второй вход которого соединен с входом второго элемента НЕ и является входом для подключения сигналов кадровых импульсов шины телекамеры, в выход второго элемента И-НЕ соединен с С-входом первого триггера, D-вход которого соединен с Общим, а S-вход - с R-входом второго триггера и выходом второго элемента ИЛИ, первый вход которого соединен с S-входом четвертого триггера и является входом сигнала Переполнение счетчика адреса, а второй вход второго элемента ИЛИ соединен с первым входом третьего элемента ИЛИ и является входом Сброс, выход четвертого триггера является выходом сигнала Седьмой разряд, вход первого элемента НЕ является входом для подключения сигналов тактовой частоты шины телекамеры, выход первого элемента ИЛИ-НЕ соединен с вторым входом третьего элемента ИЛИ-НЕ, выход которого является выходом сигнала Сброс 1-4 разрядов счетчика адреса, выход формирователя соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с R-входом четвертого триггера, вторым входом первого элемента ИЛИ-НЕ и является выходом сигнала Сброс 5-12 разрядов счетчика адреса, выход пятого элемента И-НЕ является, вы ходом сигнала Разрешение на счетчик адреса, в него введены четвертый и пятый элементы НЕ, третий элемент И-НЕ, второй и третий элементы И, первый элемент ИЛИ, четвертый элемент ИЛИ-НЕ, пятый и шестой триггеры, дешифратор, первый элемент И, первый, второй, третий входы и выход которого соединены соответственно с выходом первого элемента НЕ, выходом второго элемента НЕ, выходом второго элемента ИЛИ-НЕ и счетным входом счетчика, выход переполнения и группа информационных выходов счетчика соединены соответственно с S-входом третьего триггера и группой информационных входов дешифратора, управляющие входы которого соединены с. Общим, а выходы первого, второго, десятого и шестнадцатого импульсов соединены соответственно с первым входом второго элемента И, первым входом третьего элемента И, входом пятого элемента НЕ и входом четвертого элемента НЕ, выход которого соединен с С-входом шестого триггера, D-вход которого соединен с инверсным выходом третьего триггера, вторым входом третьего элемента И, Овходом пятого триггера и вторым входом второго элемента И, выход которого соединен с

S-входом пятого триггера, С-вход которого соединен с выходом пятого элемента НЕ и первым входом третьего элемента И-НЕ, второй вход и выход которого соединены соответственно с выходом третьего элемента НЕ и с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента ИЛИ, а выход первого элемента ИЛИ соединен с R-входом третьего триггера, входом сброса счетчика, R-входом пятого триггера, выход которого соединен с первым входом четвертого элемента ИЛИ-НЕ, второй вход и выход которого являются соответственно входом сигнала Адрес и выходом сигнала Выборка, S-вход шестого триггера соединен с выходом третьего элемента И, а инверсные выходы пятого и шестого триггеров являются соответственно выходом сигнала Запись в буферное запоминающее устройство и выходом сигнала Прибавление единицы в счетчик адреса.

Существенными отличиями устройства являются наличие дешифратора, пятого и шестого триггеров, первого элемента ИЛИ, третьего элемента И-НЕ, первого, второго и третьего элементов И, четвертого и пятого элементов НЕ, четвертого элемента ИЛИ- НЕ, а также связей этих элементов между собой и с известными блоками и элементами, что позволяет организовать сигналы записи, выборки, смены адресов во временном цикле записи информации в, блок буферной памяти, причем для формирования сигналов записи, выборки, смены адреса используются импульсы тактовой частоты, получаемой с выхода телекамеры, что дает возможность исключить сбои в работе устройства, а также позволяет работать с телекамерами, имеющими различные тактовые частоты.

/

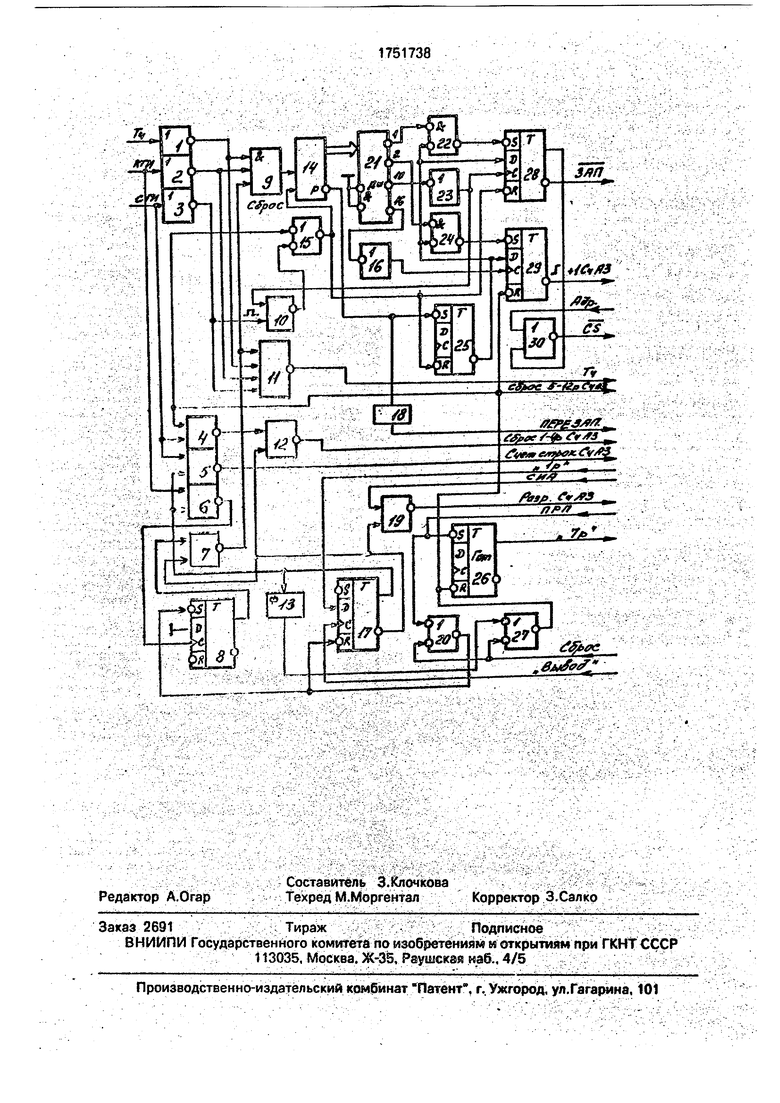

На чертеже приведена структурная схема устройства.

Устройство содержит первый 1, второй 2 и третий 3 элементы НЕ, первый элемент ИЛИ-НЕ 4, первый 5 и второй 6 элементы И-НЕ, второй элемент ИЛИ-НЕ 7, первый триггер 8, первый элемент И 9, третий 10 и четвертый 11 элементы И-НЕ, третий элемент ИЛИ НЕ 12,формирователь импульсов, счетчик 14, первый элемент ИЛИ 15, четвертый элемент НЕ 16, второй триггер 17, элемент 18 задержки, пятый элемент И-НЕ 19. второй элемент ИЛИ 20, дешифратор 21, второй элемент И 22, пятый элемент НЕ 23, третий элемент И 24, третий 25 и четвертый 26 триггеры, третий элемент ИЛИ 27, пятый 28 и шестой 29 триггеры четвертый элемент ИЛИ-НЕ 30.

Предлагаемое устройство работает в составе известного устройства ввода изображения в ЭВМ, в которое входят известные блоки - регистр сдвига, регистр приема 5 блок буферной памяти, счетчик адреса, блок канальных приемопередатчиков, блок связи с ЭВМ. Устройство предназначено для уп равления указанными блоками в режимах записи изображения в блок буферной памя- 10 ти и считывания его из блока буферной памяти в ЭВМ для обработки.

В устройстве с первого по третий элементы НЕ 1-3, первый элемент ИЛИ-НЕ 4, первый 5 и второй 6 элементы И-НЕ, второй 5 элемент ИЛИ-НЕ 7, первый триггер 8, первый элемент 9 И, третий 10 и четвертый 11 элементы И-НЕ, третий элемент ИЛИ-НЕ 12, формирователь 13, счетчик 14 бит, первый элемент ИЛИ 15, четвертый элемент НЕ

0 16, второй триггер 17, элемент 18 задержки, пятый элемент И-НЕ 19, второй элемент ИЛИ 20, четвертый триггер 26 и третий элемент ИЛИ 27 образуют узел управления, предназначенный для управления приемом

5 одного кадра телевизионного изображения Элементы выполнены на микросхемах серии 155, в частности элементы 15, 20, 27, 22 и 24 выполнены на микросхеме К155ЛИ1, К155ЛЛ1. Получив команду от ЭВМ на ввод

0 изображения (сигнал Первый разряд на D -вход второго триггера 17}, узел управления по началу следующего кадра выдает разрешение на ввод изображения в блок буферной памяти, открывает четвертый эле5 мент И-НЕ 11, а по окончании ввода выставляет сигнал готовности в ЭВМ с выхода триггера 26 по 7 разряду шины данных ЭВМ.

Дешифратор 21, счетчик 14 бит, четвер0 тый элемент НЕ 16, второй элемент И 22, пятый элемент НЕ 23, третий элемент И 24, третий 25, пятый 28 и шестой 29 триггеры, четвертый элемент ИЛ И-НЕ 30 и связи между ними образуют формирователь цикла за5 писи, выборки, смены адреса в циклах записи 16-разрядных слов в блок буферной памяти. При этом в формировании сигналов записи ЗАГГ и выборки CS для блока буферной памяти участвуют четвертый эле0 мент ИЛИ-НЕ 30, третий 25 и пятый 28 триггеры, второй элемент И 22, пятый элемент НЕ 23, дешифратор 21 (выходы 1-го и 10-го импульсов), счетчик 14 бит, первый элемент И 9, третий элемент И-НЕ 10, пер5 вый злеглент ИЛИ 15, а при формировании сигнала смены адреса +1 Сч A3 для счетчика адреса участвуют третий 25 и шестой 29 триггеры, третий элемент И 24, четвертый элемент НЕ 16, дешифратор 21 (выходы второго и шестнадцатого импульсов), счетчик

14 бит, первый элемент И 9, третий элемент И-НЕ 10, первый элемент ИЛИ 16, импульсы с выхода дешифратора 21 синхронизированы импульсами тактовой частоты Тч, поступающей с выхода телекамеры на счетный вход счетчика 14 бит через первый элемент НЕ 1 и первый элемент И 9

Счетчик бит предназначен для подсчета в блоке числа бит информации, поступающей на вход регистра сдвига в виде видеосигнала, для выдачи при переполнении счетчика 4 бит сигнала перезаписи 16-разрядного слова из регистра сдвига в регистр приема, для формирования двоичных кодов на информационных выходах счетчика 14 бит и на входах дешифратора 21 по мере заполнения счетчика 14 биттз ктовой частотой

Режстр сдвига - это регистр последовательно-параллельного действия, предназначенного для преобразования видеосигнала, поступающего на информационный вход регистра сдвига, в параллельный 16-разрядный код при подаче на вход синхронизации регистра сдвига 16 импульсов тактовой частоты

Регистр приема предназначен для приема информационного 16-разрядного слова от регистра сдвига в момент переполнения счетчика 14 бит и для хранения этого слова в течение каждого последующего, начиная с второго, цикла заполнения счетчика 14 бит шестнадцатью битами, в течение этого вре- 2 го, 1-го, 10-го и 16-го битов формируются импульсы записи ЗАП, выборки CS и смены адреса +1Сч A3, предназначенного для записи 16-разрядного слова из регистра приема в блок буферной памяти. По окончании цикла записи слова в блок буферной памяти по выбранному адресу адрес увеличивается на единицу по импульсу, сформированному с переднего фронта импульса смены адреса +1Сч A3.

Блок буферной памяти предназначен для заполнения и хранения введенного кадра телевизионного изображения, Блок выполнен на 16-статических запоминающих элементах.

Счетчик адреса предназначен для формирования адреса, по которому происходит запись очередного информационного слова в блок буферной памяти в режиме ввода изображения в блок буферной памяти, и для записи адреса от ЭВМ по которому производится считывание информации из блока буферной памяти в канал ЭВМ в режиме ввода информации в ЭВМ.

Блок канальных приемопередатчиков предназначен для приема информации из блока буферной памяти в ЭВМ, передачи

данных и адреса из ЭВМ в блок управления. Блок канальных приемопередатчиков состоит из 4 магистральных приемопередатчиков, которые находятся в режиме приема

информации от ЭВМ. В режим выдачи информации в ЭВМ приемопередатчики переводятся сигналом ПРД от блока связи с ЭВМ,

Блок связи с ЭВМ предназначен для

0 организации обмена информацией с ЭВМ, в его функции входит дешифрация адреса, выполнение канальных операций Ввод-вывод.

Устройство работает следующим обра5 зом.

Устройство обеспечивает работу в двух режимах - в режиме ввода информации в блок буферной памяти от телекамеры и обмена с ЭВМ.

0 Режим ввода информации от телекамеры.- -

В этом режиме видеоинформация, принимаемая от телекамеры регистром сдвига, поступает пословно в регистр приема, из

5 него в блок буферной памяти и запоминается в последнем.

Порядок выполнения операций следующий. Для перевода устройства в режим приема информации от телекамеры, ЭВМ

0 формирует команду сброса устройства, поступающую на элементы 20 и 27, а затем записывает единицу (по 1-му разряду канала данных ЭВМ) в регистр управления и состояния (включающий первый триггер 8

5 разрешения приема, второй триггер 17 пуска, четвертый триггер 26 готовности); для этого в цикле работы Вывод ЭВМ подает импульс Первый разряд на D-вход триггера 17, в результате чего триггер 17 пуска

0 переводится в единичное состояние, формирователь 13 формирует положительный импульс по переднему фронту сигнала Пуск, который переводит устройство в исходное состояние, организуя сигнал сброса

5 устройства на выходе третьего элемента ИЛи 27,

Сигнал Пуск поступает на вход второго элемента И-НЕ, на выходе которого формируется положительный перепад по

0 заднему фронту кадрового импульса КГИ, поступающему на второй вход второго элемента И-НЕ, т. е. по началу телевизионного кадра, устанавливающий первый триггер 8 Разр. пр. в О сигналом с выхода второго

5 элемента И-НЕ, поступающего на С-вход первого триггера 8.

На выходе второго элемента ИЛИ-НЕ 7 формируется сигнал высокого уровня, разрешающий прохождение тактовой частоты Тч через четвертый элемент И-НЕ 11 на

вход синхронизации регистра сдвига и через первый элемент И 9 на счетный вход счетчика 14 Опт. Счетчик 14 бит по мере заполнения его импульсами тактовой частоты формирует на информационных выходах коды, поступающие на входы дешифратора 21, формирующего на выходах (первом, втором, десятом и шестнадцатом) импульсы, служащие Для формирования на элементах 16,22,23,24,25,28,29 и 30 сигналов записи, выборки для блока буферной памяти и сигнала смены адреса для счетчика адреса.

На выходе переполнения счетчика 14 бит по каждому 16 му импульсу тактовой частоты формируется импульс переполне- ния, который через элемент 18 задержки, воздействуя на синхровход регистра приема, перезаписывает информационное слово из регистра сдвига в регистр приема, кроме того, импульс переполнения с выхода счетчика бит переводит третий триггер 25 в состояние 1, сигнал с инверсного выхода триггера 25 разрешает формирование сигналов записи ЗАП на выходе пятого 28 триггера и сигнала выборки CS на выходе четвертого элемента ИЛИ-НЕ 30 для блока буферной памяти и для счетчика адреса сигнала смены адреса +1 Сч A3, на выходе шестого триггера, который увеличивает содержимое счетчика адреса на единицу

После заполнения информацией блока буферной памяти счетчик адреса вырабатывает сигнал переполнения ПРП, который устанавливает четвертый триггер 26 готовности в единичное состояние и сбрасывает первый триггер 8 Разр пр. и второй триггер 17 Пуск. На этом процесс ввода изоб ра- жения в блок буферной памяти прекращается.

Режим обмена с ЭВМ.

В этом режиме информация, записанная в блок буферной памяти, может быть Считана ЭВМ при выполнении канальной операции Ввод. Порядок выполнения операций следующий. ЭВМ в адресной части передает адрес ячейки памяти блока буферной памяти по шинам адреса и данных КДА (СО-15)Н в блок канальных приемопередатчиков и по шинам адреса, данных и управления в блок связи с ЭВМ. Блок связи С ЭВМ дешифрирует адрес данного блока управления.

Через 150 не после выдачи адреса в канал ЭВМ вырабатывается сигнал КСИ- АН, поступающий на один вход второго элемента И-НЕ 19, на второй вход которого поступает открывающий сигнал в виде высокого потенциала с инверсного выхода второго триггера 17. С выхода второго элемента И-НЕ 19 передний фронт сигнала

СИАН записывает в счетчик (регистр) адреса адрес выбранной ячейки блока буферной памяти, адрес запоминается в регистре адреса. Далее ЭВМ снимает информацию с линии КДА(СО-15)Н, выставляете блок связи сигнал КВВЛДН, сигнализируя о готовности ЭВМ принять информацию. Блок связи с ЭВМ, приняв сигналы КСИАН и КВВДН, формирует сигнал ПРД, который переводит блок канальных приемопередатчиков в режим чтения информации в ЭВМ. Сигнал выборки CS для блока буферной памяти при чтении из него информация в канал ЭВМ при выполнении ЭВМ цикла Ввод формируется в блоке связи с ЭВМ из дешифрированного в блоке связи с ЭВМ адреса и сигнала СИАН, этот сигнал поступает на один вход Адр. четвертого элемента ИЛИ-НЕ 30, с выхода которого, он поступает на вход CS блока буферной памяти и разрешает его работу. В результате информация из нужной ячейки памяти блока буферной памяти поступает в ЭВМ для дальнейшей обработки.

Блок связи с ЭВМ формирует с задержкой относительно сигнала К Ввод Н сигнал К СИП Н, который извещает ЭВМ, что информация выставлена в канал ЭВМ, ЭВМ принимает сигнал К СИП Н, данные из канала и снимает сигнал К Ввод. Блок связи с ЭВМ снимает сигнал К СИП Н, завершая передачу данных к ЭВМ, по заднему фронту сигнала К СИП Н снимает сигнал К СИП А, завершая канальный цикл Ввод.

VcTponctBO может быть использовано при создании гибких производственных модулей для очувствлений роботов и т. д. в случаях, когда применяется обработка дву.- мерных изображений бинарным методом. Устройство позволяет вести ввод видеоинформации в ЭВМ со скоростью телевизирн- ной развертки, при этом устройство может работать благодаря введению блока управления, с различной тактовой частотой, принимаемой с интерфейса телекамеры. Введение дешифратора 21, триггеров 28 и 29, элементов 9, 10, 15, 16, 23, 22, 24 и 27 со связями позволяет увеличить помехозащищенность устройства, исключая сбои в работе за счет формирования фронтов и спадов импульсов записи, выборки, смены адреса от тактовой частоты.

Предлагаемое устройство по сравнению с известным позволяет повысить помехозащищенность и расширить функциональные возможности устройства для ввода изображения в ЭВМ за счет обеспечения возможности работы с различными тактовыми частотами и устранения сбоев при записи информации в буферную память

Формула изобретения Устройство для управления вводом изображения, содержащее три элемента НЕ, четыре элемента И-НЕ, три элемента ИЛИ- НЕ. два элемента ИЛИ, четыре триггера, формирователь импульсов, элемент задержки и счетчик, выход переполнения которого соединен с входом элемента задержки, выход которого является первым выходом блока управления, первый вход третьего элемента И-НЕ является перв йм вУодом блока управления, первый вход третьего элемента И-НЕ является первым входом устройства, D и С-входы второго триггера являются соответственно вторым и третьим входами устройства, второй выход второго триггера соединен с вторым вводом третьего элемента И-НЕ, первыми входами третьего и второго элемента ИЛИ-НЕ, второй вход и выход последнего соединены соответственно с выходом первого триггера и с первым входом четвертого элемента И-НЕ, выход которого является вторым выходом устройства, второй - четвертый входы четвертого элемента И-НЕ соединены соответственно с выходами первого - третьего элементов НЕ, вход третьего элемента НЕ является четвертым входом устройства и соединен с первыми входами первого элемента ИЛИ-НЕ и первого элемента И-НЕ, выход которого является третьим выходом устройства, второй вход первого элемента И-НЕ соединен с первым выходом второго триггера, входом формирователя импульсов, первым входом второго элемента И-НЕ, второй вход которого соединен с входом второго элемента НЕ и является пятым входом устройства, выход второго эле- мента И-НЕ соединен с входом синхронизации первого триггера, D-вход которого соединен с шиной нулевого потенциала устройства, а S-вход - с входом обнуления второго триггера и выходом второго элемента ИЛИ, первый вход которого соединен с S-входом четвертого триггера и является шестым входом устройства, второй вход второго элемента ИЛИ соединен с первым входом первого элемента ИЛИ и является седьмым входом устройства, выход четвертого триггера является четвертым выходом устройства, вход первого элемента НЕ является восьмым входом устройства.

выход первого элемента ИЛИ-НЕ соединен с вторым входом третьего элемента ИЛИ- НЕ, выход которого является пятым выходом устройства, выход формирователя

импульсов соединен с вторым входом первого элемента ИЛИ, выход которого соединен с входом обнуления четвертого триггера, вторым входом первого элемента ИЛИ-НЕ и является шестым выходом устройства, выход третьего элемента И-НЕ является седьмым выходом устройства, отличающееся тем, что, с целью повышения помехозащищенности устройства, оно содержит четвертый и пятый элементы НЕ,

пятый элемент И-НЕ, три элемента И, третий элемент ИЛИ, четвертый элемент ИЛИ- НЕ, пятый и шестой триггеры, дешифратор, первый - третий входы и выход первого элемента И соединены соответственно с выходами первого и второго элементов НЕ, выходом второго элемента ИЛИ-НЕ и счетным входом счетчика, выход переполнения и группа информационных выходов счетчика соединены соответственно с S-входом

третьего триггера и группой информационных входов дешифратора, первый-четвертый выходы которого соединены соответственно с первыми входами второго и третьего элементов И, входами пятого и

четвертого элементов НЕ, выход последнего соединен с входом синхронизации шестого триггера, D-вход которого соединен с выходом третьего триггера, вторым входом третьего элемента И, D-входом пятого триггера и вторым входом второго элемента И, выход которого соединен с S-входом пятого триггера, вход синхронизации которого соединен с выходом пятого элемента НЕ и первым входом пятого элемента И-НЕ, второй вход и выход которого соединены соответственно с выходом третьего элемента НЕ и с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента ИЛИ, выход третьего элемента ИЛИ - с входами обнуления третьего триггера, счетчика и пятого триггера, выход которого соединен с первым входом четвертого элемента ИЛИ-НЕ, второй вход и выход которого яеляются соответственно

девятым входом и восьмым выходом устройства, S-вход шестого триггера соединен с выходом третьего элемента И, выходы пятого и шестого триггеров являются соответственно девятым и десятым выходами

устройства.

Ъ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА ИЗОБРАЖЕНИЯ В ЭВМ | 2000 |

|

RU2166790C1 |

| Устройство для ввода изображения в ЭВМ | 1986 |

|

SU1432494A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИЗОБРАЖЕНИЯ В ЭВМ | 2003 |

|

RU2256210C2 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в устройствах считывания изобретения. Цель изобретения - повышение помехозащищенности устройства. За счет введения дешифратора, триггеров и элементов И. И-НЕ.НЕ, ИЛИ-НЕ, ИЛИ появилась возможность работы устройства с различными тактовыми частотами и устранились сбои при записи информации в буферную память 1 ил.

| Устройство для ввода изображений в электронную вычислительную машину | 1983 |

|

SU1226434A2 |

Авторы

Даты

1992-07-30—Публикация

1989-10-11—Подача