Известны демодуляторы циклических групповых кодов, выполняющие мажоритарную демодуляцию. Однако в этих устройствах демодуляция каждого символа производится без учета значений основных символов, что снижает эффективность демодуляции.

Предложенное устройство отличается от известных тем, что, с целью увеличения его эффективности, оно содержит элемент ИЛИ, один из входов которого подключен к выходу детектора, второй вход но цени обратной связи подсоединен к выходу порогового устройства, и выход соедииен с входом линии задержки.

Процесс демодуляции нроиллюстрируем на конкретном примере кода (7,3).

Для этого кода порождающий многочлен имеет вид g(x)- xi- -x-2- -x+, и любой символ кодовой комбинации может быть определен системой четырех независимых уравнений. Если с помощью этих уравнений определять первый символ Oi, то система имеет вид

«1 «5 +«7

«1 аа + «6

Й1 3 -f fli

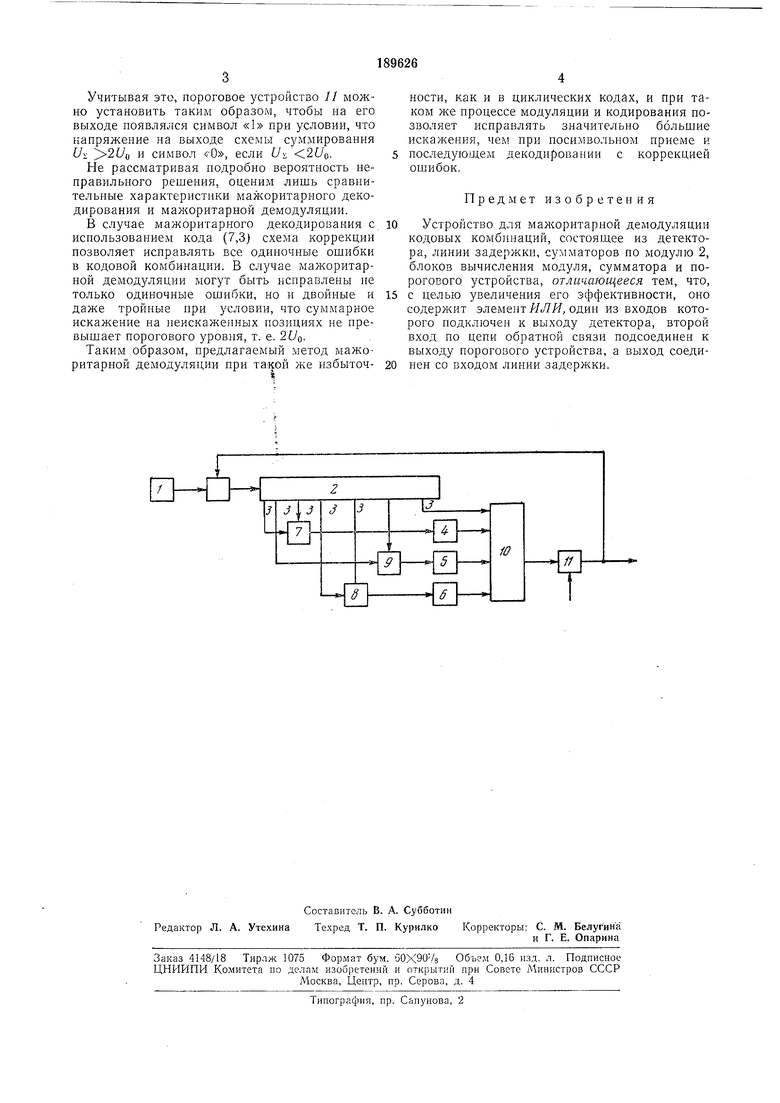

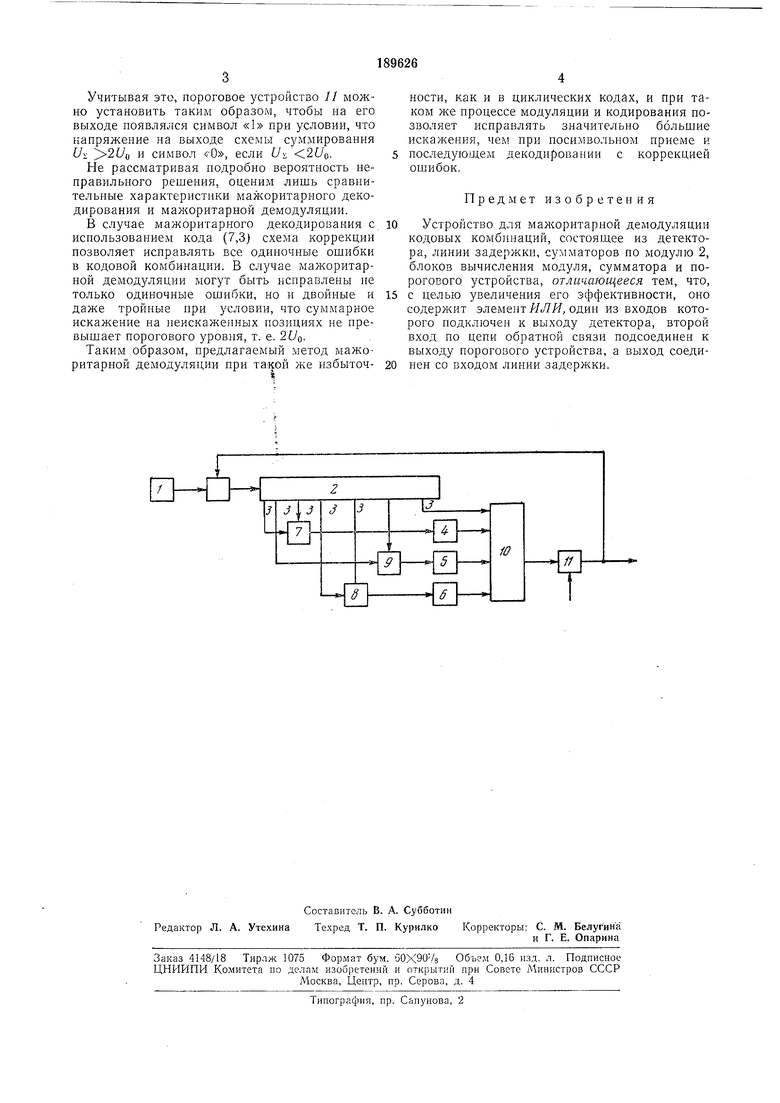

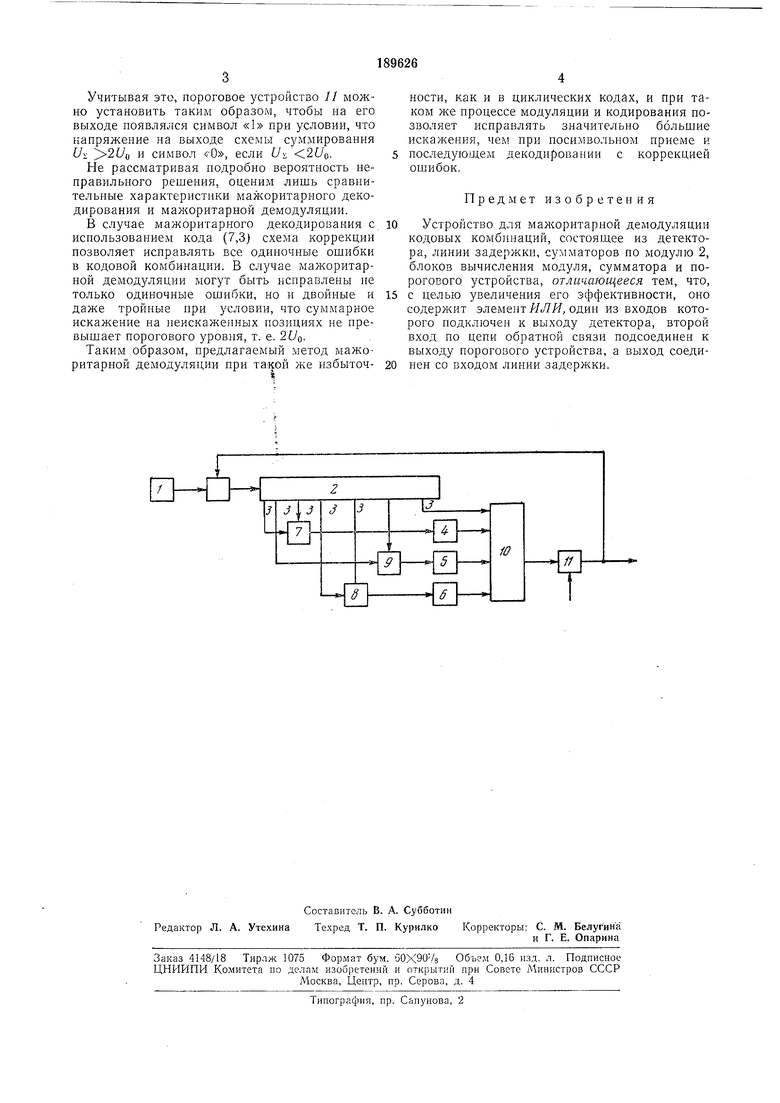

Принимаемые сигналы после детектирования детектором 1 поступают па линию задержки 2, имеющую ряд отводов 3. Число отводов равно числу символов в кодовой комбинации, а расстояние между ними соответствует времени передачи одного символа.

В соответствии с системой уравнений тнпа (1) блоками 4, 5 и 6 вычисляются модули разностей сигналов, снимаемых с отводов, соответствующнх полол ению символов fis и а-, а-2 и «с; из и «i при вводе всей кодовой комбинации в линию задерл-ски. Сами разности образуются сумматорами 7, 8 и 9. Вычисленные модули разности, а также

сигнал, соответствующий символу а, поступают на схему суммирования 10 и затем на нороговое устройство 11.

Предположим, что передаваемая информация модулируется таким образом, что символам «1 на выходе детектора соответствует некоторое напряжение Uo, а символам нулевое напрялсенне.

Аналогичным образом можно рассмотреть и случай, когда символам соответствуют напря

жения ±t/o. Тогда, если нереданный символ был равен «I, то при отсутствии искал ений в линии на выходе схемы суммирования нанряжение равно 40, а при условии, что «1 О, выход схемы суммирования будет такУчитывая это, пороговое устройство 11 можно установить таким образом, чтобы на его выходе появлялся символ «1 при условии, что напряжение на выходе схемы суммирования f/v 2(7о и символ --0, если f/s 2(7о.

Не рассматривая подробно вероятность неправильного решения, оценим лишь сравнительные характеристики мажоритарного декодирования и мажоритарной демодуляции.

В случае мажоритарного декодирования с использованием кода (7,3) схема коррекции позволяет исправлять все одиночные ошибки в кодовой комбинации. В случае мажоритарной демодуляции могут быть исправлены не только одиночные ошибки, но и двойные и даже тройные нри условии, что суммарное искажение на неискаженных позициях не превышает порогового уровня, т. е. 21.

Таким образом, предлагаемый метод мажоритарной демодуляции при же избыточности, как и в циклических кодах, и при таком же процессе модуляции и кодирования позволяет исправлять значительно большие искажения, чем при посимвольном приеме и последующем декодировании с коррекцией ошибок.

Предмет изобретения

Устройство для мажоритарной демодуляции кодовых комбинаций, состоящее из детектора, линии задержки, сумматоров по модулю 2, блоков вычисления модуля, сумматора и порогового устройства, отличающееся тем, что,

с целью увеличения его эффективности, оно содержит элемент ЯЛЯ, один из входов которого нодключен к выходу детектора, второй вход по цепи обратной связи подсоединен к выходу порогового устройства, а выход соединен со входом линии задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарное декодирующее устройство | 1975 |

|

SU538502A1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ДЛЯ ЦИКЛИЧЕСКИХ | 1970 |

|

SU261460A1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| Мажоритарное декодирующее устройство корректирующего кода Рида-Маллера | 1980 |

|

SU902283A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ С ЖЕСТКИМИ И МЯГКИМИ РЕШЕНИЯМИ ДЛЯ ДВУХСТУПЕНЧАТОГО КАСКАДНОГО КОДА И МОДУЛЯЦИИ ПО ТИПУ СТЫКА С1-ФЛ | 2024 |

|

RU2834891C1 |

| Устройство для исправления ошибок в информации, закодированной циклическим кодом | 1974 |

|

SU512589A1 |

| Декодер циклического кода | 1988 |

|

SU1599996A1 |

| Устройство мажоритарного декодирования кода Рида-Соломона по k-элементным участкам кодовой комбинации | 2015 |

|

RU2613760C2 |

Авторы

Даты

1966-01-01—Публикация