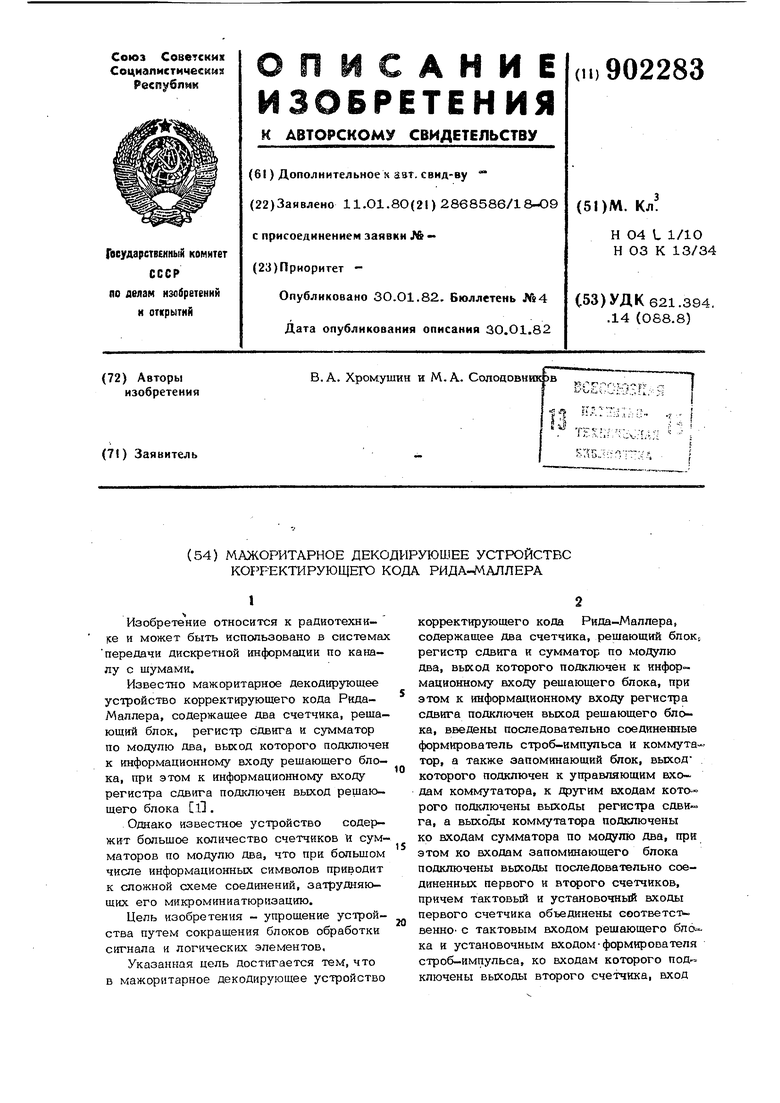

(54) МАЖОРИТАРНОЕ ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО КОРРЕКТИРУЮЩЕГО КОДА РИДА-МАЛЛЕРА

1

Изобретение относится к радиотехни1се и может быть использовано в системах передачи дискретной информации по каналу с шумами.

Известно мажоритарное декодирующее устройство корректирующего кода РидаМаллера, содержащее два счетчика, решающий блок, регистр сдвига и сумматор по модулю два, выход которого подключен к информационному входу решающего блока, при этом к информационному входу регистра сдвига подключен выход решающего блока ll.

Однако известное устройство содержит большое количество счетчиков И сумматоров по модулю два, что при большом числе информационных символов приводит к сложной схеме соединений, затрудняющих его микроминиатюризацию.

Цель изобретения - упрощение устройства путем сокращения блоков обработки сигнала и логических элементов.

Указанная цель достигается тем, что в мажоритарное декодирующее устройство

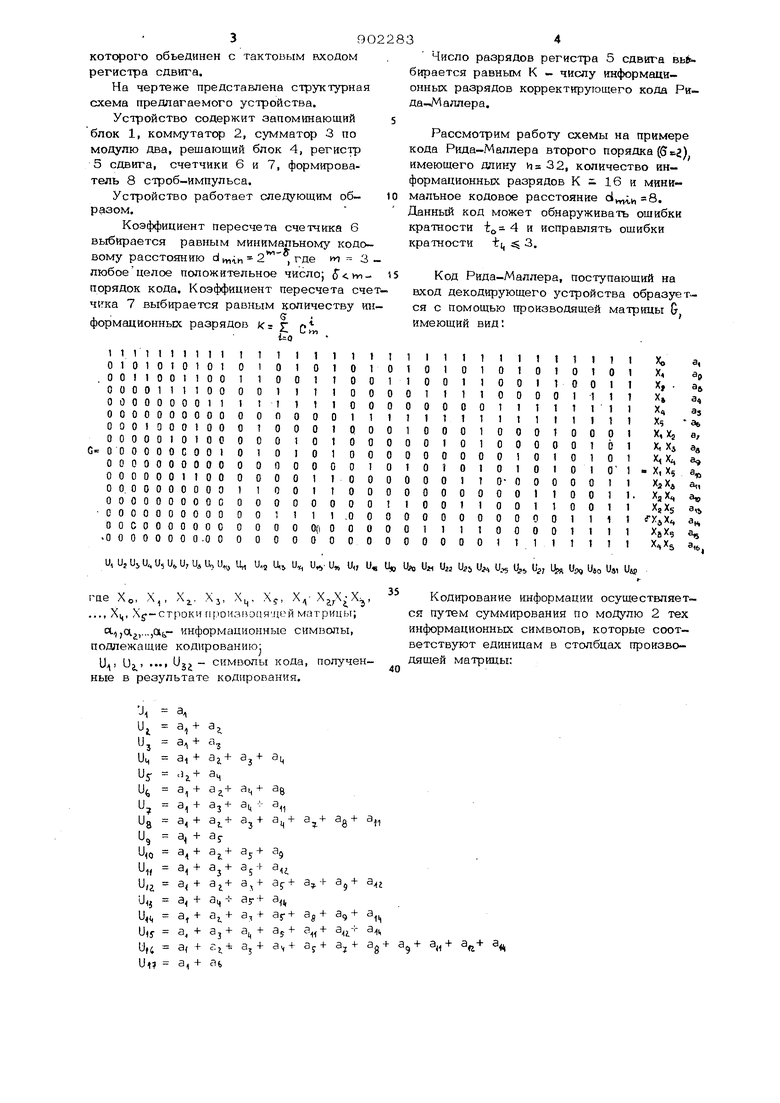

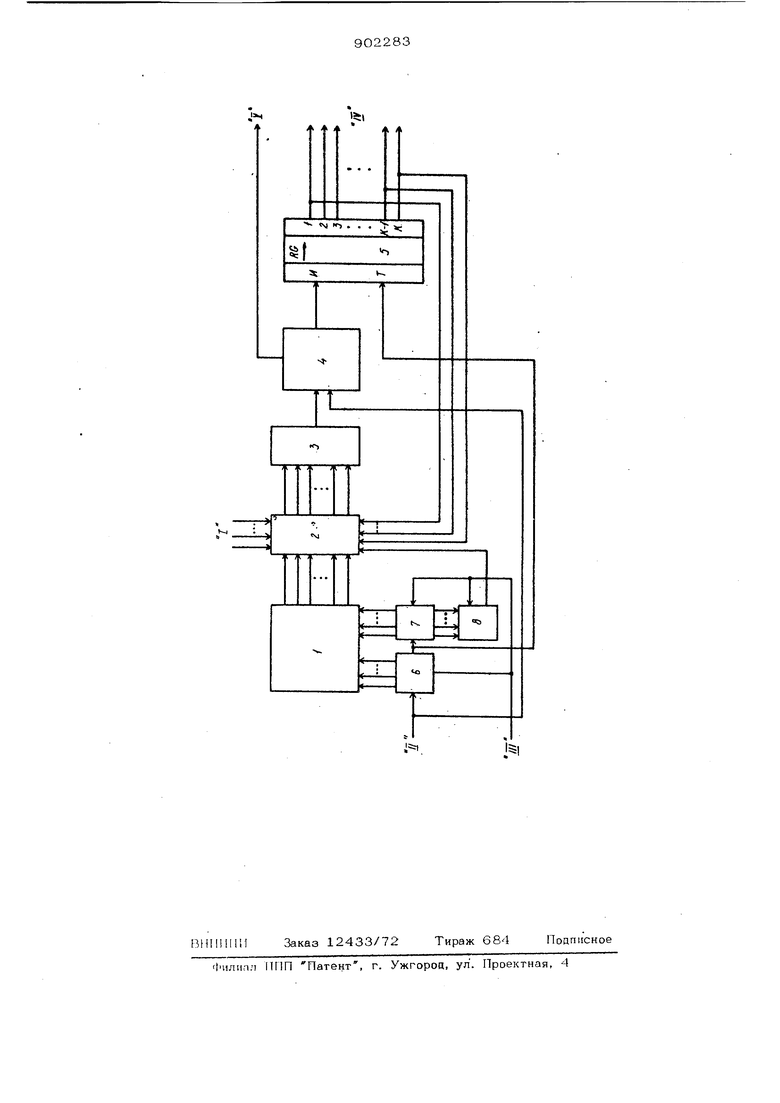

корректирующего кода Рида-Маллера, содержащее два счетчика, решающий блокг регистр сдвига и сумматор по модулю два, выход которого подключен к информационному входу решающего блока, при этом к информационному входу регистра сдвига подключен выход решающего блока, введены последовательно соединенные формирователь строб-импульса и коммута--тор, а также запоминающий блок, выход которого подключен к управляющим входам коммутатора, к другим входам котсм рого пошслючены выходы регистра сдвига, а выходы коммутатора подключены ко входам сумматора по модулю два, при этом ко входам запоминающего блока подключены выходы последовательно соединенных первого и второго счетчиков, причем тактовьй и установочный входы первого счетчика объединены соответственно с тактовым входом решающего блбка и установочным входом-формирователя строб-импульса, ко входам которого под ключены выходы второго счетчика, вход которого объединен с тактовым входом регистра сдвига. На чертеже представлена структурная схема предлагаемого устройства. Устройство содержит запоминающий блок 1, коммутатор 2, сумматор 3 по модулю два, решающий блок 4, регистр 5 сдвига, счетчики 6 и 7, формирователь 8 строб-импульса. Устройство работает следующим об- разом. Коэффициент пересчета счетчика 6 выбирается равным минимальному кодо вому расстоггнию ,an , где и 3 любоецелое положительное число; ( порядок кода. Коэффициент пересчета сч чкка 7 выбирается равным количеству и формационных разрядов К Число разрядов регистра 5 сдвига вь& бирается paBHbnvi К - числу информацйoHHbix разрядов корректирующего кода Рн- да- Маллера. Рассмотрим работу схемы на примере кода Рида-Маллера второго порядка (5 2) имеющего длину ii 32, количество информационных разрядов К - 16 и Минимальное кодовое расстояние . Данный код может обнаруживать ошибки кратности t(j- 4 и исправлять ошибки кратности ti, 3. Код Рида-Маллера, поступающий на вход декодирующего устройства образуется с помощью производящей матрицы & имеющий вид:

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Устройство цикловой синхронизации порогового декодера | 1987 |

|

SU1483661A2 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302701C1 |

и, и, и,, Щ и, и и, и и, и Urt и,2 U,,, и и. и, и« и, Цс и«

x,;(-x,

Xc, X,

рце Xo, X,

Ч

ц..., Хц, Xj--CTpoK4 произноцядой матрицы;

«.,,cx,,...,a(- информационные символы, подлежащие кодированию:

Щ Uj, .... Uj2 - символы кода, полученные в результате кодирования.

Кодирование информации осуществляется путем суммирования по модулю 2 тех информационных символов, которые соответствуют единицам в столбцах производящей матрицы:

3ft+

а,+

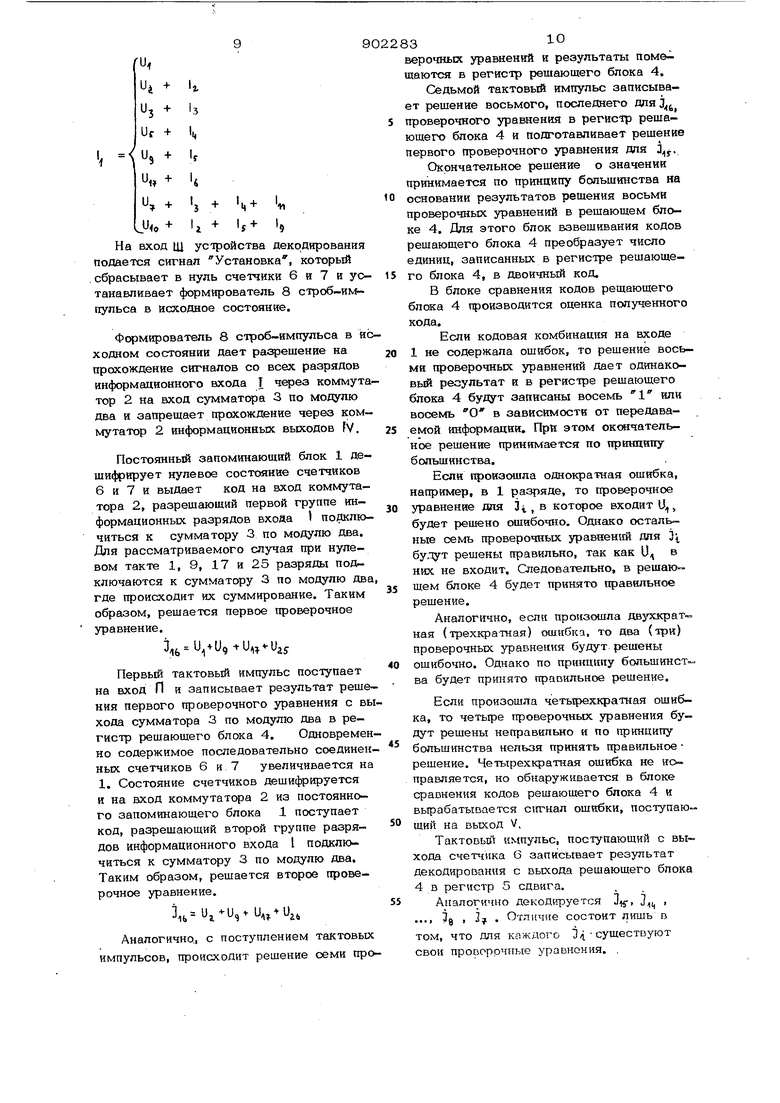

а,+ Uj3 и и.- и,,, и, L UM Ujo Us, Ujs 1г+ 1 На вход Ш устройства декодирования подается сигнал Установка, который .сбрасывает в нуль счетчики 6 и 7 и устанавливает формирователь 8 строб-импульса в исходное состояние. Формирователь 8 строб-импульса в ис ходном состоянии дает разрешение на прохождение сигналов со всех разрядов информационного входа Т через коммута тор 2 на вход сумматора 3 по модулю

два и запрещает прохождение через коммутатор 2 информационных выходов fV,

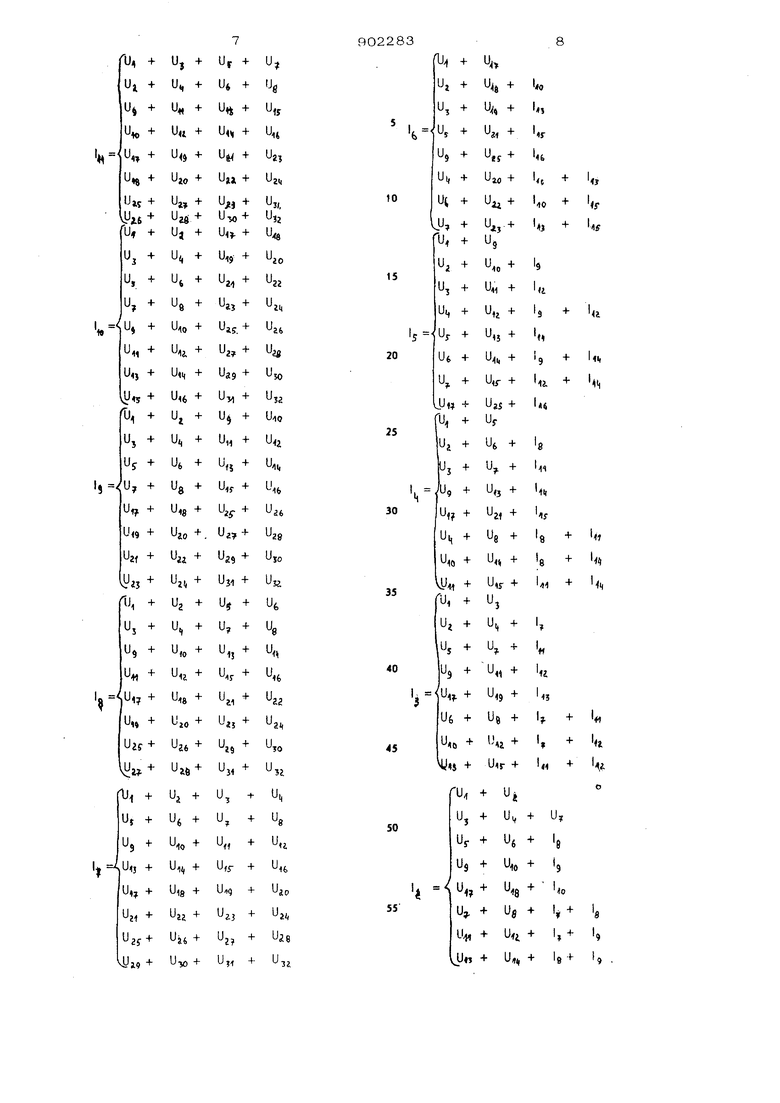

Постоянный запоминающий блок 1 дешифрирует нулевое состояние счетчиков 6 и 7 и выдает код на вход коммутатора 2, разрешающий первой группе информационных разрядов входа подключиться к сумматору 3 по модулю два. Для рассматриваемого случая при нулевом такте 1, 9, 17 и 25 разряды подключаются к сумматору 3 по модулю два где происходит их суммирование. Таким образом, решается первое проверочное уравнение.

Первый тактовый импульс поступает на вход П и записывает результат решения первого проверочного уравнения с выхода сумматора 3 по модулю два в регистр решаюшего блока 4. Одновременно содержимое последовательно соединенных счетчиков 6 и 7 увеличивается на 1. Состояние счетчиков дешифрируется и на вход коммутатора 2 из постоянного запоминающего блока 1 поступает код, разрешающий второй группе разрядов информационного входа I подклк читься к сумматору 3 по модулю два. Таким образом, решается второе проверочное уравнение.

,, и,-и,.и„-и,,

Аналогично., с поступлением тактовых импульсов, происходит решение семи про9

восемь О в зависимости от передава-

5 емой информации. При этом окончательное решение принимается по принципу большинства.

Если произошла однократная ошибка, например, в 1 разряде, то проверочное

0 уравнение для 3i, в которое входит U,, будет решено ошибочно. Однако остальные семь проверочных уравнен1П1 для 3 будут решены правильно, так как Од в них не входит. Следовательно, в решаю-

щем блоке 4 будет принято правильное решение.

Аналогично, если произошла двухкрат- Ная (трехкратная) ошибка, то Два (три) проверочньк уравнения будут решены

ошибочно. Однако по принципу большинст ва будет принято правильное решение.

Если произошла четырехкратная ошибка, то четьфе проверочных уравнения будут решены неправильно и по принципу большинства нельзя принять правильноерешение. Четырехкратная ошибка не исправляется, но обнаруживается в блоке сравнения кодов решаюшего блока 4 и вьфабатывается С1п:нал ошибки, поступающий на выход V,

Тактовый импульс, поступающий с вы хода счетчика 6 записывает результат декодирования с выхода решаюшего блока 4 в регистр 5 сдвига.

Аналогично декодируется З,-, j , ..., 9 Отличие состоит лишь в том, что для каждого j/j существуют свои проворрчиые уравнения. . 310 верочных уравнений и результаты помещаются в регистр решающего блока 4. Седьмой тактовый импульс записывает решение восьмого, последнего для j проверочного уравнения в регистр решающего блока 4 и подготавливает решение первого проверочного уравнения для 3,.. Окончательное решение о значении принимается по принципу большинства на основании результатов решения восьми проверочных уравнений в решающем блоке 4, Для этого блок взвешивания кодов решающего блока 4 преобразует число единиц, записанных в регистре решающе- го блока 4, в двоичный код. В блоке сравнения кодов решающего блока 4 производится оценка полученного Если кодовая комбинация на входе 1 не содержала ошибок, то решение восьми проверочных уравнений дает одинаковый ресультат и в регистре решающего блока 4 будут записаны восемь 1 или Декодирование j, , 3, ... ij, 54 бази руется на использовании ранее вычисленных значений З. При переходе к вычислениям 3(j, ,.., J состояние счетчика 7 дашифрируется в формирователе 8 строб-импульса и триггер формирователя 8 строб-импульса опрокидывается и до окончания цикла декодирования 16, 24, 26, 27, 28, 29, ЗО, 31 и 32 разряды входного кода 1 от сумматора 3 по модулю два и подклю чает вместо них 2, 3, ..., 16 разряды выходного кода IV. Декодирование J , 3j , ..., ils-,Jb осуществляется аналогично D, , ... j соответствии с системой проверочных уравнений. Конструктивно декодирующее устройство может быть выполнено на серийно выпускаемых микросхемах малой и повышенной степени интеграции. Формула изобретения Мажоритарное декодирующее #Ьтройство корректирующего кода Рида-Маллера, содержащее два счетчика, решающий блок, регистр сдвига и сумматор по модулю два, выход которого подключен к информационному входу решающего блока, при этом к информационному входу ре- гистра сдвига подключен выход решающего блока, отличающееся тем, что, с целью упрощения устройства путем сокращения блоков обработки сигнала и логических элементов, введены последо- . вательно соединенные формирователь строб-импульса и коммутатор, а также запоминающий блок, выход которого подключен к управляющим входам коммутатора, к другим входам которого подключены выходы регистра сдвига а выходы коммутатора подключены ко входам сумматора по модулю два, при этом ко входам запоминающего блока подключены выходы последовательно соединенных перво го и второго счетчиков, причем тактовый и установочный входы первого c4eTw чика объединены соответственно с тактовым входом решающего блока и установочным входом формирователя строб-импульса, ко входам которого подключены вьрсоды второго счетчика, вход которого объединен с тактовым входом регистра сдвига. Источники информации, принятые во внимание при экспертизе 1, Авторское свидетельство СССР № 415819, кл. Н 04 L 1/1О, 1971 (прототип).

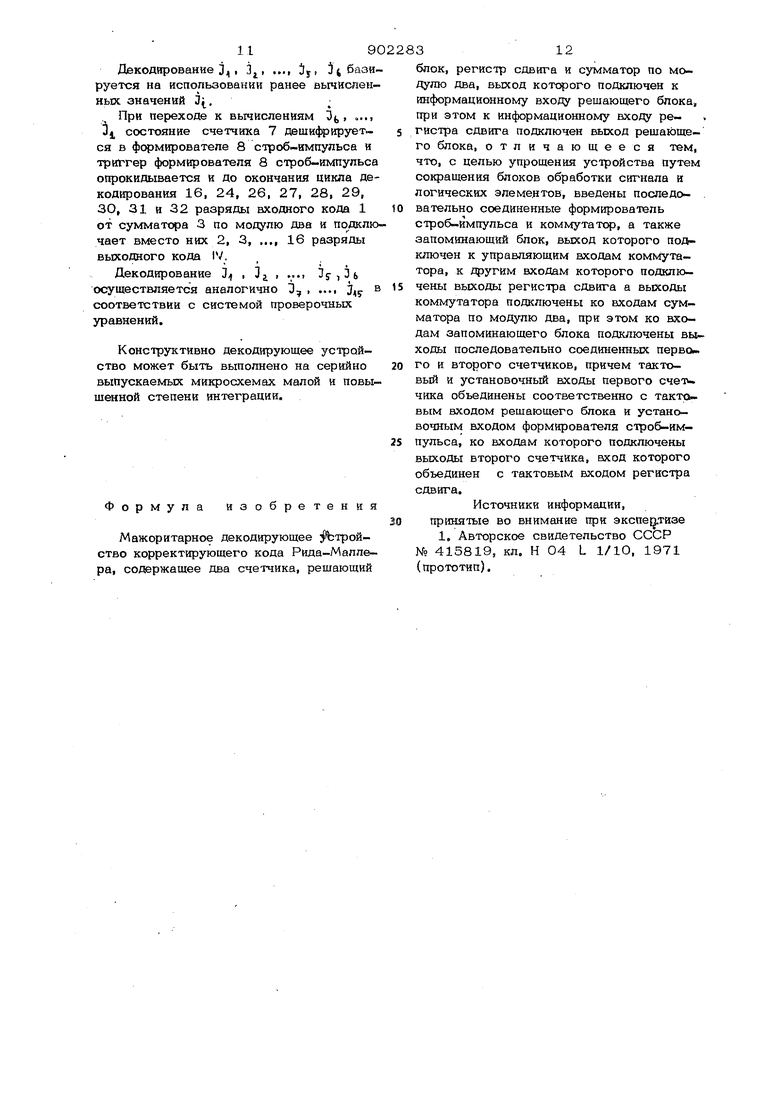

Авторы

Даты

1982-01-30—Публикация

1980-01-11—Подача