.Известны двоичные последовательные сумматоры на феррит-диодных элементах с управлением полупроводниковыми ключевыми триодами, содержащие две схемы разноименности и цепь образования переносов.

В предложенном сумматоре входные обмотки записи феррит-Диодных элементов схем разноименности присоединены « базам ключевых триодов, в коллекторные цепи которых включены обмотки запрета элементов, относящихся к противоположному входу, и обмотки схем совпадения цепи переноса. Благодаря такому Бьшолнению повышается надежность сумматора и уменьшается влияние разброса параметров составных элементов.

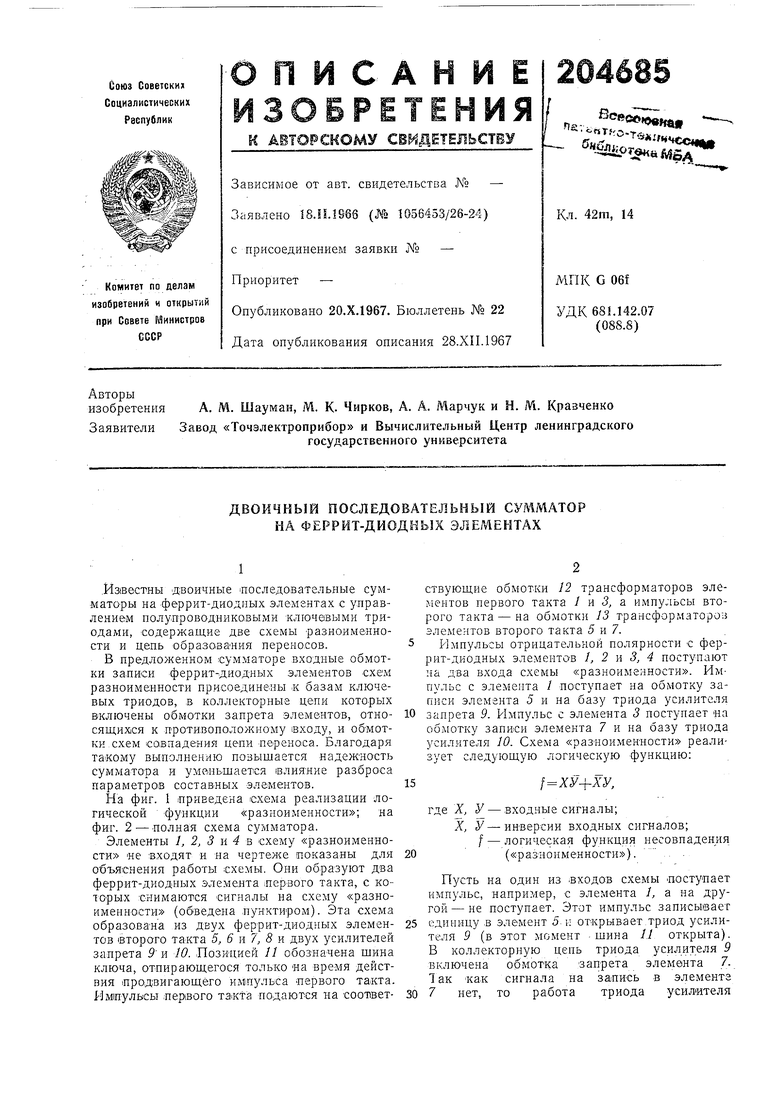

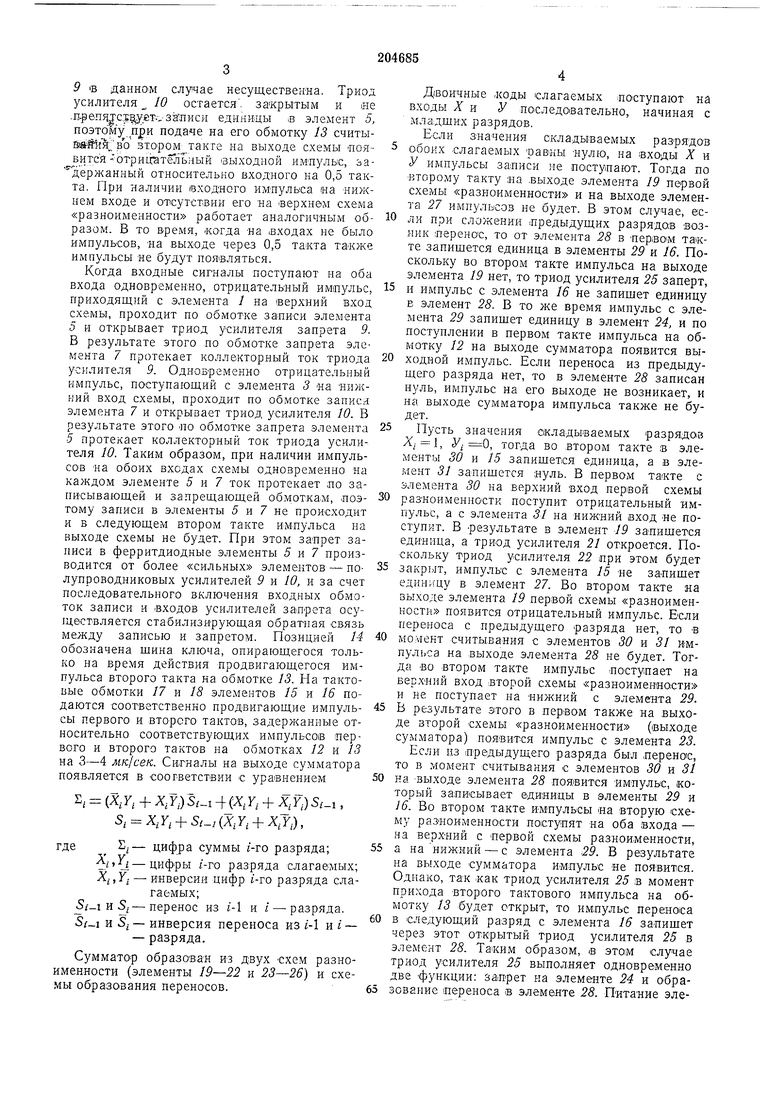

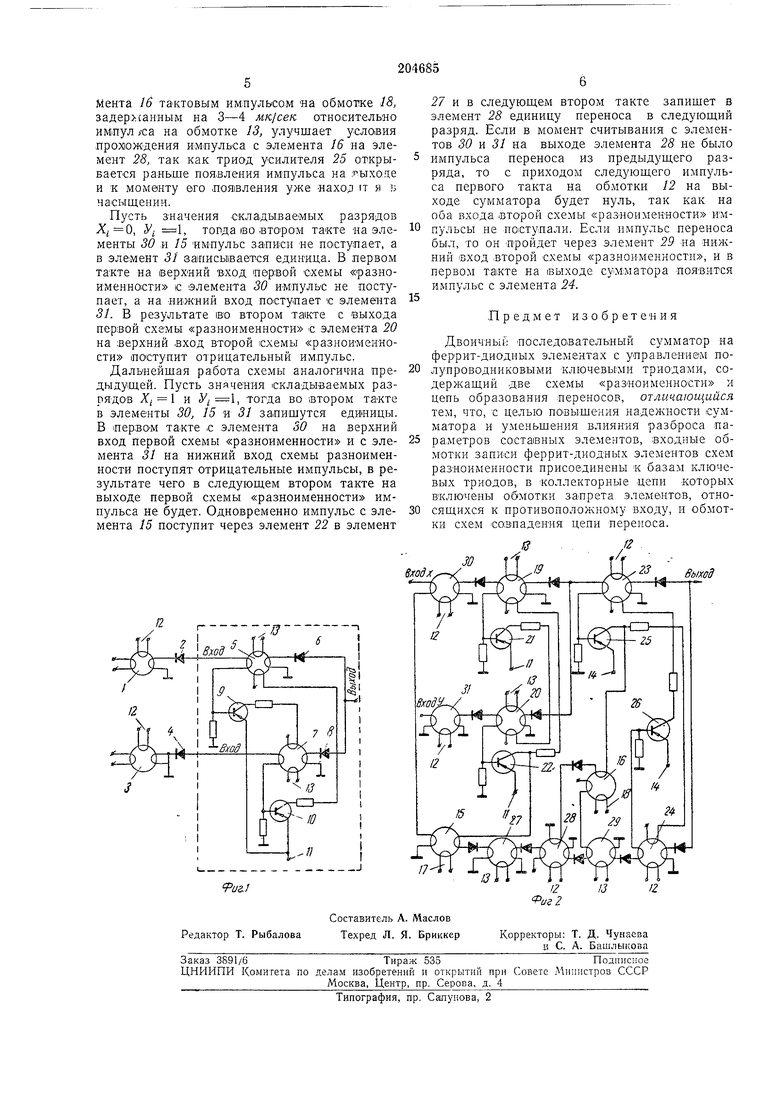

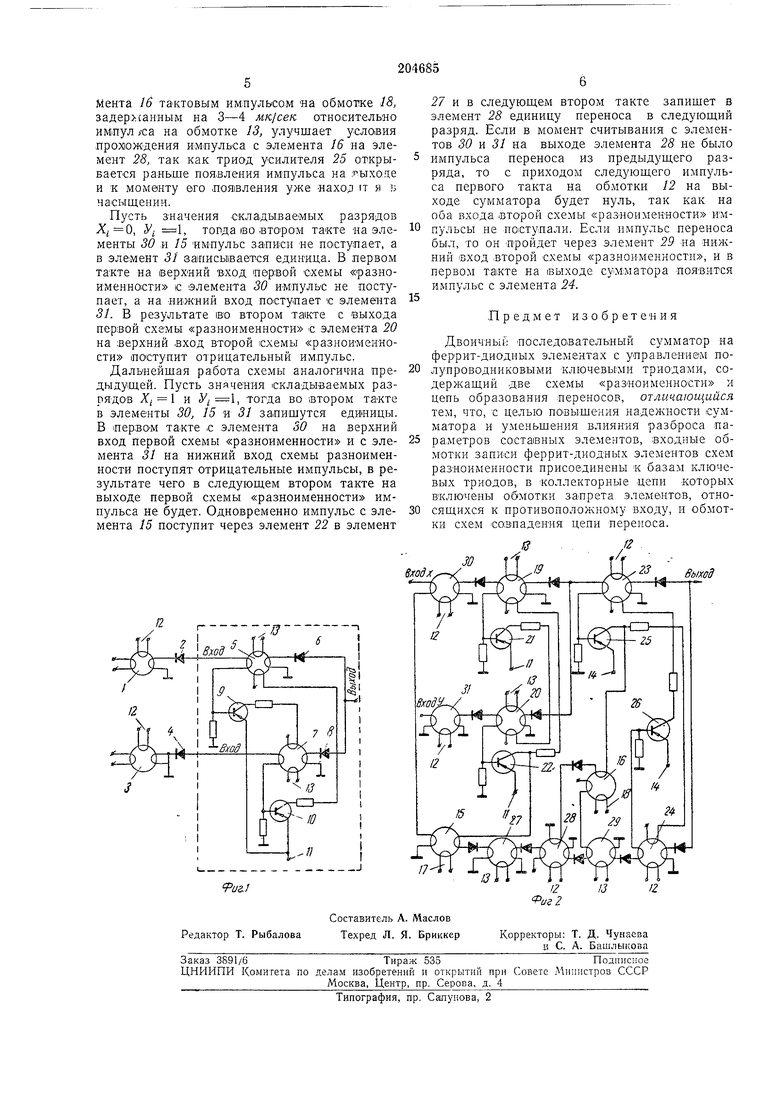

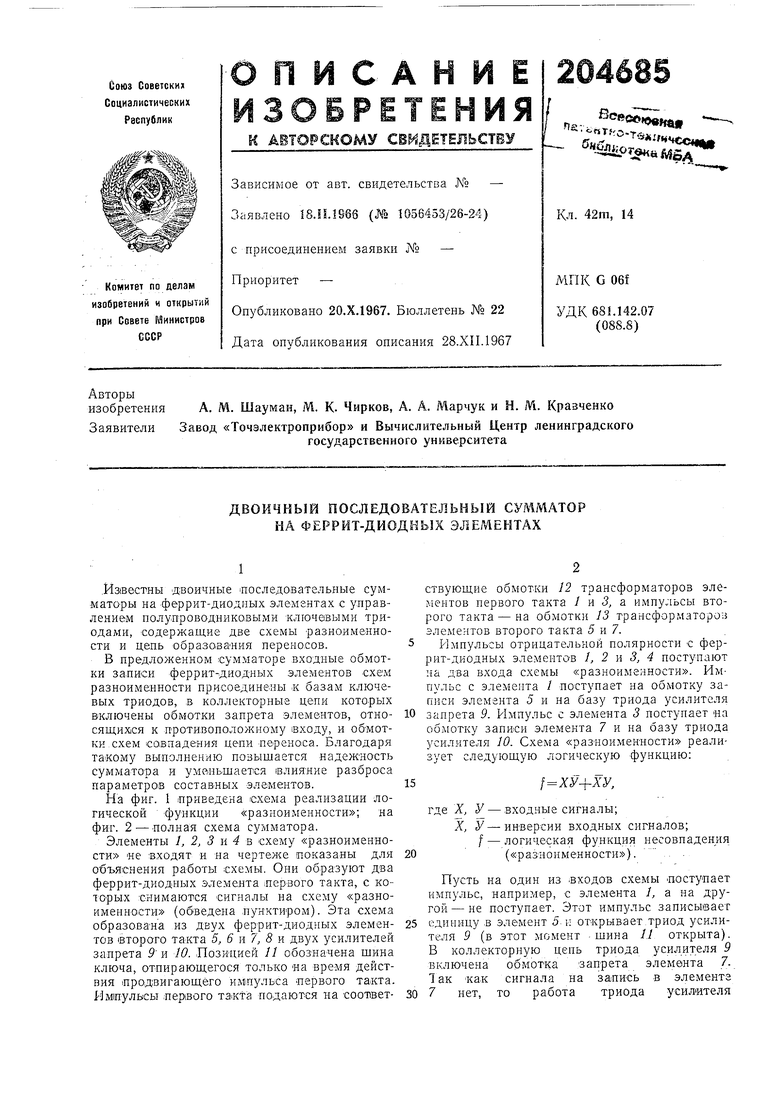

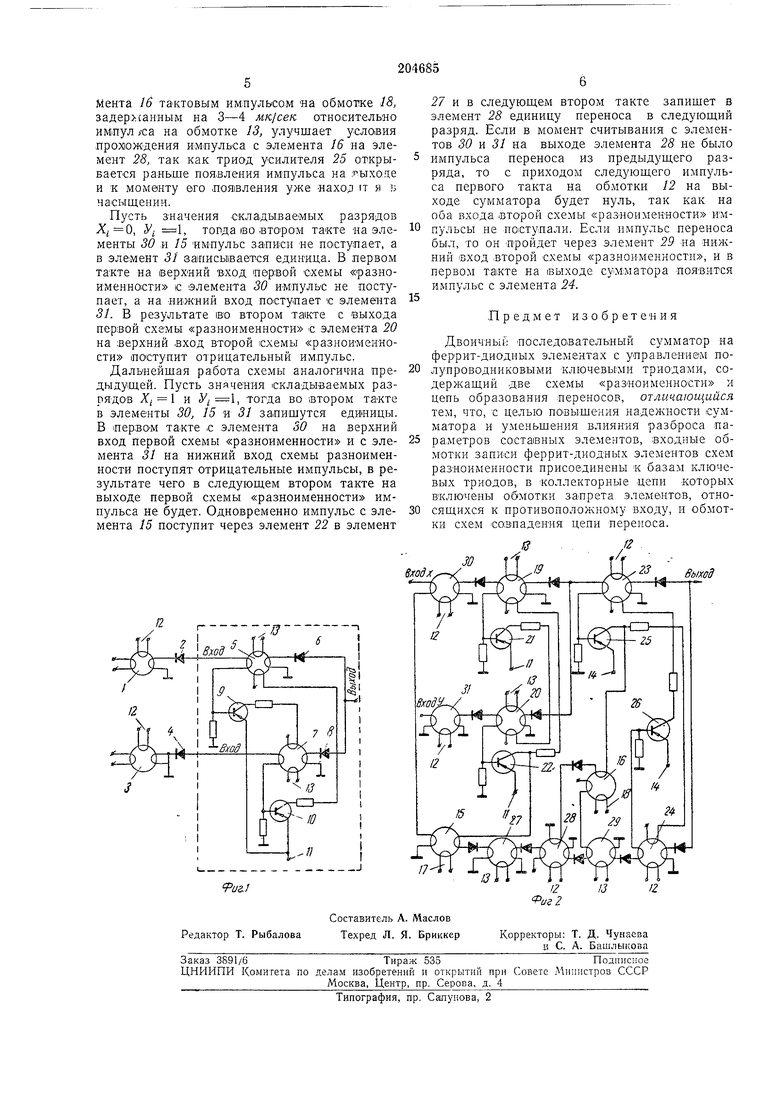

На фиг. 1 приведена схема реализации логической функции «разноименнОСти ; на фиг. 2-полная схема сумматора.

Элементы 1, 2, 3 и 4 в схему «разноименности не входят и на чертелсе показаны для объяснения работы схемы. Они образуют два феррит-диодных элемента лервого такта, с которых снимаются Сигналы на схему «разноименности (обведена цунктиром). Эта схема образовала из двух феррит-диодных элементов второго такта 5, 6 7, 8 w. двух усилителей запрета 5и 10. Позицией // обозначена шина ключа, отпирающегося только на время действия продвигающего импульса первого такта. Импульсы первого таКТа подаются на соот1ветствующие обмотки 12 трансформаторов элементов первого такта 1 3, & импульсы второго такта - на обмотки 13 трансформаторе;} элементов второго такта 5 и 7.

Импульсы отрицательной полярности с феррит-диодных элементов 1, 2 м 3, 4 поступают па два входа схемы «разноименности. Импульс с элемента / поступает на обмотку записи элемента 5 и на базу триода усилителя запрета 9. Импульс с элемента 3 поступает «а обмотку записи элемента 7 к на базу триода усилителя 10. Схема «разноименности реализует следующую логическую функцию:

,

где J, У - входные сигналы;

X, У-инверсии входных сигналов;

f - логическая функция несовпадения («разнонменности).

Пусть на один из входов схемы поступает импульс, например, с элемента /, а на другой - не поступает. Этот импульс записывает единицу в элемент 5 и открывает триод усилителя 9 (в этот момент шина // открыта). В коллекторную цепь триода усилителя 9 включена обмотка запрета элемента 7. Так Ка.к сигнала на запись в элемента 7 нет, то работа триода усилителя

9 в данном случае несущественна. Триод усилителя 10 остается , закрытым и яе .п-рбпч с$|у :т.-зЁписи единицы в элемент 5, поэтому при подаче на его обмотку 13 считый Й я во втором такте на выходе схемы появится-oтpи гaтёльi ый выходной имнулыс, ьа держанный относительно входного на 0,5 такта. При наличии /входного имнулыса на нижнем входе и отсутствии его на верхнем схема «разноименности работает аналогичяым образом. В то время, .когда яа .входах не было импульсов, на выходе через 0,5 такта также импульсы не будут появляться.

Когда входные сигналы поступают на оба входа одновременно, отрицательный нмюульс, приходящий с элемента / на верхний вход схемы, проходит но обмотке записи элемента 5 и открывает триод усилителя запрета 9. В результате этого по обмотке запрета элемента 7 протекает коллекторный ток триода уснлигеля 9. Одновременно отрицательный импульс, поступающий с элемента 3 «а -нижний вход схемы, проходит по обмотке записи элемента 7 и открывает триод усилителя 10. В результате этого ото обмотке запрета элемента 5 протекает коллекторный ток триода усилителя 10. Таким образом, при наличии импульсов «а обоих входах схемы одновременно на каждом элементе 5 и 7 ток протекает ,по записывающей и запрещающей обмоткам, поэтому записи в элементы 5 и 7 не происходит и в следующем втором такте импульса на выходе схемы не будет. При этом запрет записи в ферритдиодные элементы 5 и 7 производится от более «сильных элементов - полупроводниковых усилителей 9 и 10, н за счет последовательного включения входных обмоток записи и входов усилителей запрета осуществляется стабилизирующая обратная связь между записью и запретом. Позицией 14 обозначена щина ключа, опирающегося только на время действия продвигающегося импульса второго такта на обмотке 13. Па тактовые обмотки 17 и 18 элементов 15 и 16 подаются соответственно продвигающие импульсы первого и второго тактов, задержанные относительно соответствующих импульсов первого и второго тактов на обмотках 12 и 13 на 3-4 мк/сек. Сигналы на выходе сумматора появляется в соогветствии с уравнением

Ц И У, + Х,У,) S,i -+(Х,Г, + X,Y,} , S, X,Y, + Si,j(XJ, + XJ,},

цифра суммы г-го разряда;

г -цифры г-го разряда слагаемых; X,YI - инверсии цифр 1-го разряда слагаемых;

и S;-перенос из t-l и / - разряда. и 5; - инверсия переноса из г-1 и i - - разряда.

Двоичные .коды слагаемых поступают на входы X и У последовательно, начиная с младщих разрядов.

Если значения складываемых разрядов обоих слагаемых равны нулю, на входы X и У импульсы записи не поступают. Тогда по второму такту яа выходе элемента 19 первой схемы «разноименности и на выходе элемента 27 импульсов не будет. В этом случае, если при сложении .предыдущих разрядов возник перенос, то от элемента 28 в первом такте запищется единица в элементы 29 и 16. Поскольку во втором такте импульса на выходе элемента 19 пет, то триод усилителя 25 заперт,

и импульс с элемента 16 не запищат единицу Е элемент 28. В то же время импульс с элемента 29 запищет единицу в элемент 24, и по поступлении в первом такте импульса на обмотку 12 на выходе сумматора появится выходной импульс. Если перекоса из предыдущего разряда нет, то в элементе 28 записан нуль, импульс на его выходе не возникает, и на выходе сумматора импульса также не будет.

Пусть значения складываемых разрядов Xi l, У 0, тогда во втором такте в элементы 30 и 15 запищется единица, а в элемент 31 запищется нуль. В первом такте с элемента 30 на верхний вход первой схемы

разноименности поступит отрицательный импульс, а с элемента 31 на нижний вход не поступит. В результате в элемент 19 запишется единица, а триод усилителя 21 откроется. Поскольку триод усилителя 22 при этом будет

закрыт, импульс с элемента 15 не запишет единицу в элемент 27. Во втором такте на выходе элемента 19 первой схемы «разноименности появится отрицательный импульс. Если переноса с предыдущего разряда нет, то в

момент считывания с элементов 30 и 31 импульса на выходе элемента 28 не будет. Тогда во втором такте импульс поступает на верхний вход второй схемы «разноименности и не поступает на нижний с элемента 29.

В результате этого в первом также на выходе второй схемы «разноименности (выходе сумматора) появится импульс с элемента 23. Если из предыдущего разряда был .перенос, то в момент считывания с элементов 30 и 31

на выходе элемента 28 появится ймпульс, который записывает единицы в элементы 29 и 16. Во втором такте и-мпульсы на вторую схему разноименности поступят на оба .входа - на верхний с первой схемы разнои-менности,

а на нилсний - с элемента 39. В результате на выходе сумматора импульс не появится. Однако, так как триод усилителя 25 в момент прихода второго тактового нм.пульса на обмотку 13 будет открыт, то имлульс переноса

в следующий разряд с элемента 16 запишет через этот открытый триод усилителя 25 в элемент 28. Таким образом, в этом случае триод усилителя 25 выполняет одновременно две функции: запрет на элементе 24 и обра

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР НА ФЕРРИТ-ТРАНЗИСТОРНЫХ МОДУЛЯХ | 1970 |

|

SU277409A1 |

| ДЕСЯТИЧНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК НА ФЕРРИТ-ТРАНЗИСТОРНЫХ ЯЧЕЙКАХ | 1969 |

|

SU251275A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| СУММАТОР ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU268008A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 1967 |

|

SU197281A1 |

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1970 |

|

SU272672A1 |

| УСТРОЙСТВО ЦИКЛИЧЕСКОЙ, СИНХРОННОЙ, с ВРЕМЕННЫМ | 1970 |

|

SU277009A1 |

| Однотактный одноразрядный сумматор на феррит-транзисторных ячейках | 1959 |

|

SU126662A1 |

Авторы

Даты

1967-01-01—Публикация