Известны устройства управления цифровой вычислительной машины, построенные по принципу динамического анализа приоритета выполнимости элементов рабочего языка и хранения числовой и служебной информации в отдельных стеках памяти, содержащие регистры различного назначения.

Предлагаемое устройство отличается от известных тем, что оно содержит блок автоматического управления, подключенный к командному блоку, регистру текущего элемента командного блока, регистру и схеме приоритета выполнения программы; блок динамического хранения содержимого оперативных ячеек, соединенный общей шиной с логическим блоком вычисления булевых функций, регистром режима, оперативным регистром стековой памяти, регистром текущего командного элемента програм.мы, регистром следующего элемента программы, блоком динамической адресации ячеек памяти, оперативным и долговременным запоминающим устройством и с выходом блока чтения программы, выход блока динамической адресации соединен с оперативным запоминающим устройством.

Это позволяет увеличить быстродействие устройства и его экономичность.

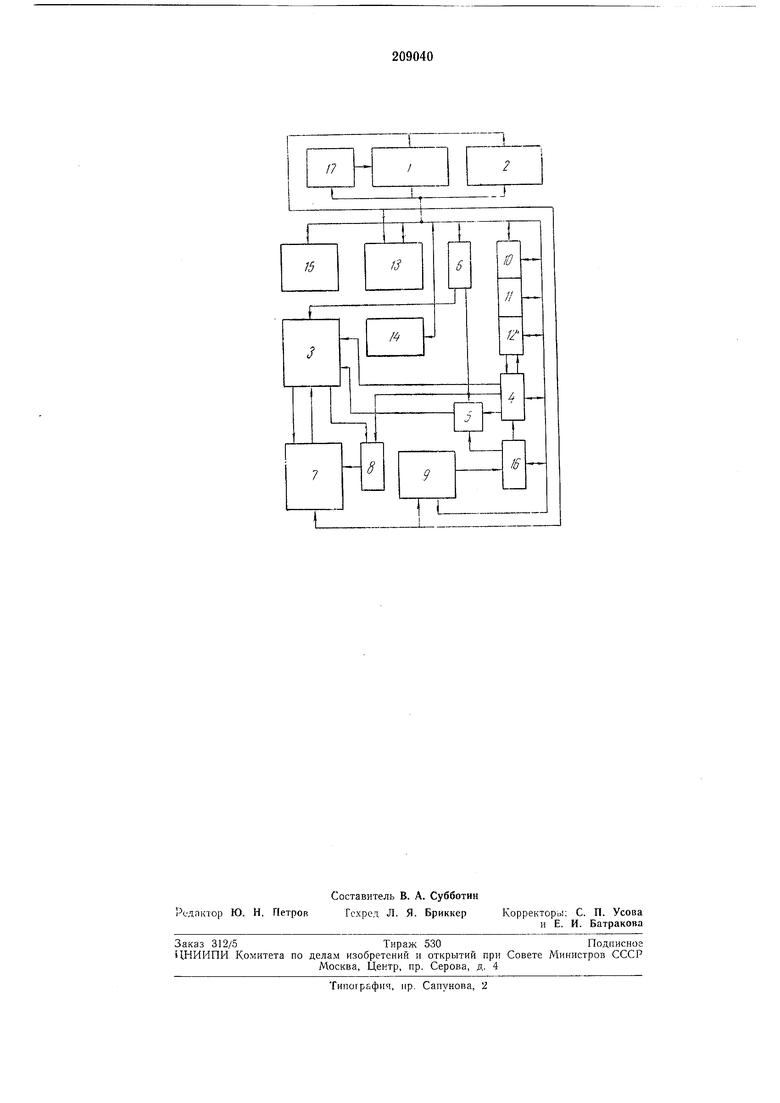

нающего устройства 2 представлена на чертеже.

Устройство состоит из блока автоматного управления 3, связанного, в частности, с регистром 4 текущего командного элемента

программы, схемой приоритета выполнения

элементов программы 5, регистром режима 6

и командным блоком 7.

Командный блок 7 связан с общей кодовой

шиной числа запоминающих устройств / и 2 и адресным регистром 8. Адрес в регистр 8 может быть занесен как из блока автоматного управления 3, так и из регистра 4 текущего элемента программы.

С общей кодовой щиной числа связаны также блок чтения программы 9, оперативные регистры стековой памяти 10, 11 п 12 и блок динамического хранения содержимого оперативных ячеек устройства 13.

Номером 14 обозначена группа индекс-регистров, счетчиков и сумматор устройства управления. Предусмотрен также логический блок 15 вычисления булевских функций. Все регистры устройства связаны между собой и адресными регистрами запоминающих устройств / и 2 через общую кодовую шину адреса. Кроме того, между некоторыми из них имеется непосредственная связь. В частности, блок чтения программы 9, связан с регистром

16 - с регистром 4, а регистр 4 - с одним и;; полей оперативного регистра стековой памяти - регистром 12.

Чтение и выделение элементов рабочей программы выполняется блоком 9. Очередной командный элемент програл1мы, состоящий в случае языка АЛГОЛ-60 из кода ограничителя и признака операнда, принимается из блока 9 на регистр следующего командного элемента 16.

Выполнение (интерпретация) командных элементов программы осуществляется в соответствии с приоритетом из выполнимости, проверяемым на дешифраторе 5 выполнимости.

Выполняемый командный элемент программы помещается на регистр 4.

Командный элемент программы, который не может быть выполнен, и его операнд переписываются на регистры 10, 11 и 12, составляющие вместе один оперативный регистр стековой памяти.

. В зависимости от интенсивности использования алгоритмы интерпретации реализуются либо в автомате управления 3, либо в командном блоке 7 в виде запоминаемых микропрограмм. Выполнение запоминаемых микропрограмм вызывается по адресу в регистре 8, который пересылается туда из регистра текущего командного элемента 4, либо устанавливается из автомата управления 3.

Блоком 7 реализуется система команд, которая имеет адресную структуру и обеспечивает запуск операций, выполняемых в смежных устройствах, и управление операциями над содержимым регистров устройства управления и ячеек оперативной памяти /, выполняемых средствами устройства управления.

Способ интерпретации командного элемента программы зависит от вида синтаксического понятия языка, которому этот элемент принадлежит.

Признактекущего интерпретируемого понятия языка фиксируется в регистре 6, связанном с общей кодовой щиной и автоматом управления 3, и схемой приоритета 5.

Устройство управления располагает своим сумматором, используемым для модификации адресов, органической группой счетчиков и регистров 14, связанными между собой и с другими регистрами устройства управления.

Широкое использование стандартных ячеек оперативной памяти в качестве регистров хранения обеспечивается применением в устройстве блока 13 для динамического храпения

содержимого запоминаемых регистров. Адрес требуемой ячейки, принятый с кодовой щины в блок 13, сравнивается с адресами ячеек, содержимое которых хранится в этом же блоке. При совпадении адресов требуемый код выдается из выбранного регистра блока 13 на кодовую щину. Если среди адресов в блоке 13 нет адреса искомой ячейки, содержимое одного из регистров блока нереписывается в

соответствующую ячейку памяти, а на его место вызывается содержимое требуемой ячейки. В результате указанной динамической замены в блоке 4 удерживается содержимое регистров, которые используются наиболее активно.

Для вычисления переключательных функций, в том числе и от переменных выходных сигналов схем устройства управления, в устройство управления введен логический блох 3.

Обращение к оперативной памяти 1 может выполняться как непосредственно по физическому адресу, так и через блок динамической адресации 17 по математическому адресу. В последнем случае требуемый сегмент информации, если он отсутствует в оперативной памяти 1, вызывается в нее из внешней памяти.

Предмет изобретения

Устройство управления цифровой вычислительной мащины, построенное по принципу динамического анализа приоритета выполнимости элементов рабочего языка и хранения чиеловой и служебной информации в отдельных стеках памяти, содержащее регистры, отличающееся тем, что, с целью увеличения его быстродействия и экономичности, оно содержит блок автоматического управления, подключенный к командному блоку, регистру текущего элемента командного блока, регистру режима и схеме приоритета выполнения программы; блок динамического хранения содержимого оперативных ячеек, соединенный общей щиной с логическим блоком вычисления булевых функций, регистром режима, оперативным регистром стековой памяти, регистром текущего командного элемента программы, регистром следующего элемента программы,

блоком динамической адресации ячеек памяти, оперативным и долговременным запоминающим устройством и с выходом блока чтения программы; выход блока динамической адресации соединен с оперативным запо-минающим устройством.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления цифровой вычислительной машины | 1971 |

|

SU437074A1 |

| Устройство для обработки выражений языков программирования | 1974 |

|

SU519715A1 |

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С КОМАНДОПОДОБНЫМИ ЛОГИЧЕСКИМИ УПРАВЛЯЮЩИМИ ЭЛЕМЕНТАМИ | 1997 |

|

RU2143726C1 |

| Устройство для управления параллельным выполнением команд в стековой электронной вычислительной машине | 1976 |

|

SU556440A1 |

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С РАСШИРЕННЫМ СЛОВОМ СОСТОЯНИЯ | 1999 |

|

RU2149444C1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1069001A1 |

| Вычислительная машина со структурной интерпретацией входного алгоритмического языка | 1966 |

|

SU208353A1 |

| Процессор микропрограммируемой ЭВМ | 1979 |

|

SU860077A1 |

| Устройство для синтаксического анализа программ | 1980 |

|

SU918950A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

Авторы

Даты

1968-01-01—Публикация