(54) ПРОЦЕССОР МИКРОПРОГРАЬШИРУБМОЙ ЭВМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор микропрограмируемой ЭВМ | 1989 |

|

SU1697082A1 |

| Устройство для стековой адресации | 1979 |

|

SU783793A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для управления параллельным выполнением команд в стековой электронной вычислительной машине | 1976 |

|

SU556440A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Процессор | 1976 |

|

SU670935A1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Устройство для отладки программ | 1979 |

|

SU849218A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения различных ЭВМ с микропрограммным управлением,предназначенных для эффективной реализации микропрограммными средствами проблемно и машинно-ориентированнах языков высокого уровня. Известен микропрограммируелий процессор, использующий общую дисковую память для хранения микропрограм М данных,причем память разбита на, дв самостоятельные области с регулируем границей, предназначенные для раздельного хранения отдельных подпрогракм (макрокоманд) и последовательностей отдельных микрокоманд (микропрограмм) l. Отсутствие в данном процессоре специальных аппаратных средств для организации безадресной обработки данных, т.е. стекового механизма,, предполагает программную реализацию такого механизма в дисковой памяти процессора, что приводит к заметному возрастанию числа обращений в дисковую память и снижению производительности процессора при реализации входных языков, предусматривающей безадресную обработку данных. Повышение производительности процессора за счет использования более быстродействующей основной памяти достигается в известных процессорах микропрограммируемых ЭВМ 2 } и З J, . предназначенных для экономной работы с полями переменной длины в основной памяти. В TaKitx процессорах основная память совмещает функции управляющей и основной памяти и используется для хранения как микропрограмм, -faK и данных 2 , либо управляющая и основная памяти выполнены раздельно при хранении микропрограмм как в Управляющей, так и в основной памяти, и возможности динамической первзаписи управляющей памяти Гз. Однако в упомянутых процессорах также отсутствует аппаратная реализация стекового механизма, и программная реализация его в основной памяти приводит к снижению производительности процессора при выполнении безадресной обработки данных. Известны процессоры 4, имеющие в своем составе стековую память для эффективной реализаций безгщреснай обработки данных. Эти процессоры не микропрограммируемые, отличительной их Особенностью является чисто магазинная, стековая организация, которой подчинена вся структура процессора и система программирования и которая ориентирована на стековую обработку данных фиксированной длины Однако применение чисто магазинной организации в структуре процессора микропрограммируемой ЭВМ и ее системе микрокоманд нецелесообразно, так как это приводит к резкому возрастанию числа обращений в стековую память и сказывается на производительности процессора. Наиболее близок к предлагаемому процессор, включающий регистр микрокоманды, память микрокоманд, регистр .адреса очередной микрокоманды, схему обращения в адресный стек, функци ональный блок, регистры левого и пр вого операнда, регистр настройки, первый и второй регистры общего назначения, схему сдвига, регистр адр са поля данных, регистр типа и длин поля данных, первую и вторую секции буферной памяти, схему модификации, схему установки переноса, схему установки типа и дЛины поля данных, с му пропуска микрокоманды, схему интерфейса s. Одной из отличительных черт этого процессора является возможность доступа к полям переменной длины с точ ностью до бита, а байтовой основной памяти. Микрокоманды хранятся как в управляющей, так и в основной памяти. Обращение в основную память з очередной микрокомандой происходит только в случае ее отсутствия в управляющей памяти. Микрокоманда, выделяемая из управляющей памяти или основной памяти, заносится непосред ственно в регистр микрокоманды. К недостатку процессора следует отнести существенное замедление его работы при выполнении безадресной обработки данных. Отсутствие стековой памяти в его структуре приводит к необходимости программной регшиза ции стекового механизма в основной памяти процессора и, вследствие это го, к существенному возрастанию чис ла обращений в основную память приреализации проблемно и машинно-ррие тированных входных языков, предусма ривафщей безадресную обработку данных. Цель изобретения - снижение частоты обращений из процессора в осно ную память, и следовательно, повыше ние производительности процессора при микропрограммной реализации входных языков, предусматривающей безадресную обработку данных. Поставленная цель достигается те что в процессор микропрограммируемо ЭВМ, содержащий регистр микрокоманды, блок памяти микрокоманд, регистр адреса микрокоманды, блок адресации, блок стековой памяти адресов, арифметическо-логический блок, регистр Левого операнда, регистр правого операнда, блок настройки, два регистра общего назначения, блок сдвига, блок адреса поля данных, блок типа и длины поля данных, два блока буферной памяти, блок модификации, блок установки переноса, блок установки типа и длины поля данных, блок пропуска микрокоманды, блок сопряжения, причем первый вход данных регистра микрокоманды .соединен с выходом данных блока памяти микрокоманд, второй управляющий вход - с управляющим выходом блока пропуска микрокоманды, первый выход данных регистра адреса микрокоманды соединен со входом данных блока памяти микрокоманд, первый вход данных - с первым выходом данных блока адресаций,а второй выход данных - с первым входом данных блока адресации, второй вход данных блока адресации соединен с выходом данных блока стековой памяти адресов, а второй выход данных - со входом данных блока стековой памяти адресов, первый вход данных ари метическо-логического блока соединен с выходом данных регистра левого операнда, второй вход данных - с выходом данных регистра правого операнда, второй выход данных - со входом данных блока установки переноса, второй управляющий вход - с первым управляющим выходом блока настройки, первый вход данных блока настройки соединен с выходом данных блока установки переноса, второй вход данных - с первым выходо141 данных блока установки типа и длины поля данных, третий вход данных - со вторим выходом данных блока установки типа и« длины поля данных, первый выход данных - с первым входом данных блока модификации, с первым входом данных блока установки типа и длины поля данных, со вторым входом данных блока сопряжения, первый управляющий выход - со вторым управляющим входом блока сдвига, выход данных второго регистра общего назначения соединен с первым входом данных блока сдвига, первый вход данных блока адреса поля данных соединен с первым данных первого блока буферной памяти, второй вход данных - с первым выходом данных блока модификации, первый выход данных - с первым входом данных первого блока буферной памяти, третьим входом данных блока модификации и третьим входом данных блока сопряжения, первый вход данных блока типа и длины поля данных соединен с первым выходом данных второго блока буферной памяти, второй вход данных - со вторым выходом данных блока модификации, первый выход данных - с первым входом данных второго блока буферной памяти, четвертым входом данных блока модифи кации и вторым входом данных блока установки типа и длины поля данных, третий .вход данных ,блока установки типа и Д7ШНЫ поля данных соединен со вторым выходом данных второго блока буферной памяти, а управляющий выход - со вторым управляющим входом блока пропуска микрокоманды, первый вход данных блока сопряжения соединен с-выходом данных процессора, а первый выход данных - со входом данных процессора,второй вход и першлЯ выход данных регистра микрокоманды, второй вход и третий выход данных ре гистра адреса микрокоманда, первый выход данных арифметическо логического блока, вход и выход данных регистра левого операнда, вход и выход данных регистра правого операнда, четвертый вход и второй выход данных блока настройки, вход и выход данных первого регистра общего назначения, вход и выход данных второго регистра общего назначения, первый выход данных блока сдвига, третий вход и первый выход данны блока адреса поля данных, третий вход и первый выход данных блока тип .и длины поля данных, второй входи второй выход да«ных первого блока буферной памяти, второй вход и третий выход данных второго блока буферной памяти, второй вход данных блока модификации, четвертый вход и второй выход данных блока сопряжения соединены с шиной данных, а первые управлянвдие входы регистра адреса микрокоманды, блока адресации арифметическо-логического блока, регистЕюв левого и правого операнда, блока настройки, регистров общего назначе ния, блока сдвига блока гщреса поля данных, блока типа и длины поля данных, блоков буферной памяти, блока модификации, блока установки переноса, блока установки типа и длины поля данных, блока пропуска микрокоманды, блока сопряжения, а также управляющий выход регистра микрокоманды соединены с шиной управления, введено устройство суековой пгиъ1яти, первый вход данных которого соединен со вторым выходом данных блока сдвига, третий вход данных - с первым выходом данных блока настройки, четвертый вход данных - с первым выходом данных блока типа и длины поля данных, пятый вход данных - с третьим выходом данных первого блока буферной, памяти, первый и второй выхода данных - соответственно со вторым и третьим входами данных блока сдвига/ второй вход и третий выход данных с шиной данных, первый управляющий вход - с шиной управления, первый управляющий выход - с третьим управляющим входом блока сдвига, второй управляющий выход - с третьим управляющим входом блока пропуска микрокоманды ... Устройство стековой памяти содержит блок хранения операндов, блок стековой адресации, блок(стековых операций, причем первый вход данных блока хранения операндов соединен с первым входом данных устройства стековой памяти, второй вход данных с выходом данных блока стековой адресации, выход данных - с первым выходом данных устройства стековой памяти, вход данных блока стековой адресации соединен со вторым входом данных устройства стековой памяти, выход данных - со вторым выходом данных устройства стековой памяти, первый- пятый управляющие входа - соответственно с первым-пятым управляющими выхода ш блока стековых операций, управляклций выход - со вторым управляющим входом блока стековых операций, первый вход дашных блока стековых операций соединен со вторым входом данных устройства стековой памяти, второй вход данных - с третьим входом данных устройства стековой пс№€яти, третий вход данных с четвертым входом данных устройства стековой Псмяти, четвертый вход данных - с пятым входом данных устройства стековой памяти, первый выход данных - со вторым выходом Данных устройства стековой памяти, второй вы- . ход данных - с третьим выходом данных устройства стековой памяти, первый управлякяций вход - с первым управляющим входом устройства сте-. коврй памяти, шестой управлякядий выход - с первым управляющим выходом устройства стековой памяти,седьмой управляющий выход - со вторым управлягадим выходом устройства стековой памяти. Кроме того, блок стековых операций содержит узел настройки стека операндов, узел поля стековых данных, узел установки текущей длины поля стека операндов, узел модификации, распределитель импульсов, первый-восьмой выходы которого соединены соответственнс с первым-пя м управляющими выходами блока и с управляКяцими входами узла- настройки стека операндов, узла поля стековых данных, узла установки текущей длины поля стека операндов и узла модификации , первый и второй управляющие входы распределителя импульсов являются первым и вторам управлякхцими входами блока, первый выход данных узла настройки стека операндов соединен с первым выходом данных блока, першлй выход данных узла .настройки стека операндов и рторой выхо

данных узла поля стековых данных соединены с первым выходом данных: блока, первый вход данных блока соединен с первыми входами данных, узла настройки стека операндов, узла поля стековых данных и узла модификации, третий вход данных блока соединен с первым входом данных узла установки текущей длины поля стека операндов, первый выход данных узла настрой1 и стека операндов соединен со вторыми входами данных узла модификации и узла установки текущей длины поля стека операндов, третий вход данных которого и третий вход дайных узла модификации соединены с третьим выходом данных узла поля стековых данных, первый выход данных которого соединен с четвертым входом данных узла модификации, первый и второй выходы данных которого соединены соответственно со вторым и третьим вхбдами данных узла поля стековых данных, управляющий выход и второй вход узла настройки стека операндов соединены соответственно с шестым управляющим выходом блока и с первым выходом данных узла установки текущей длины поля стека операндов, уп равляющий выход и четвертый, пятый входы данных которого являются соответственно седьмым управляющим выходом блока и вторым, четвертым вхЬдами данных блока.

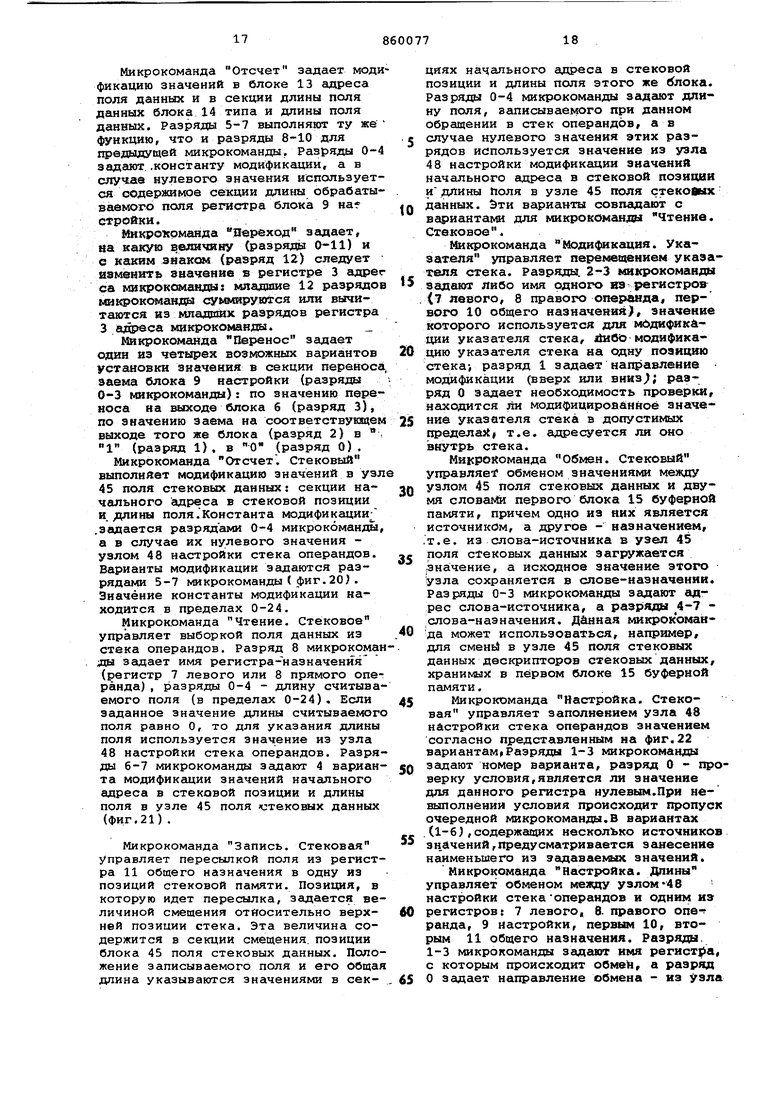

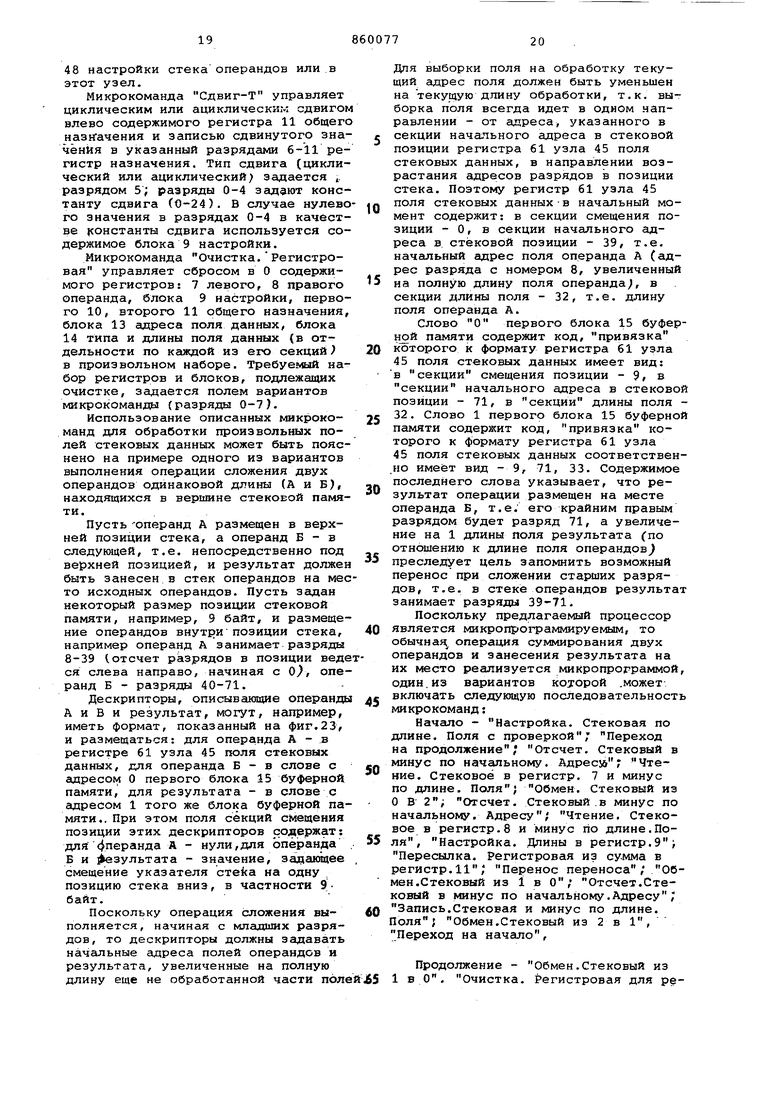

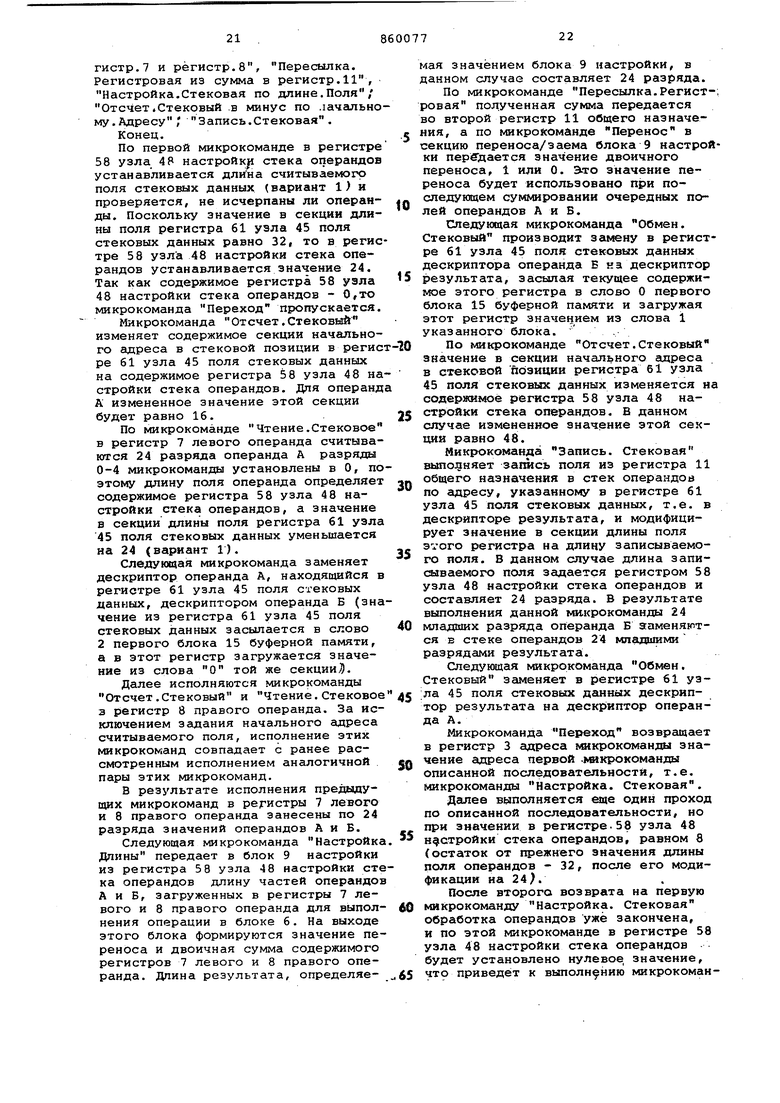

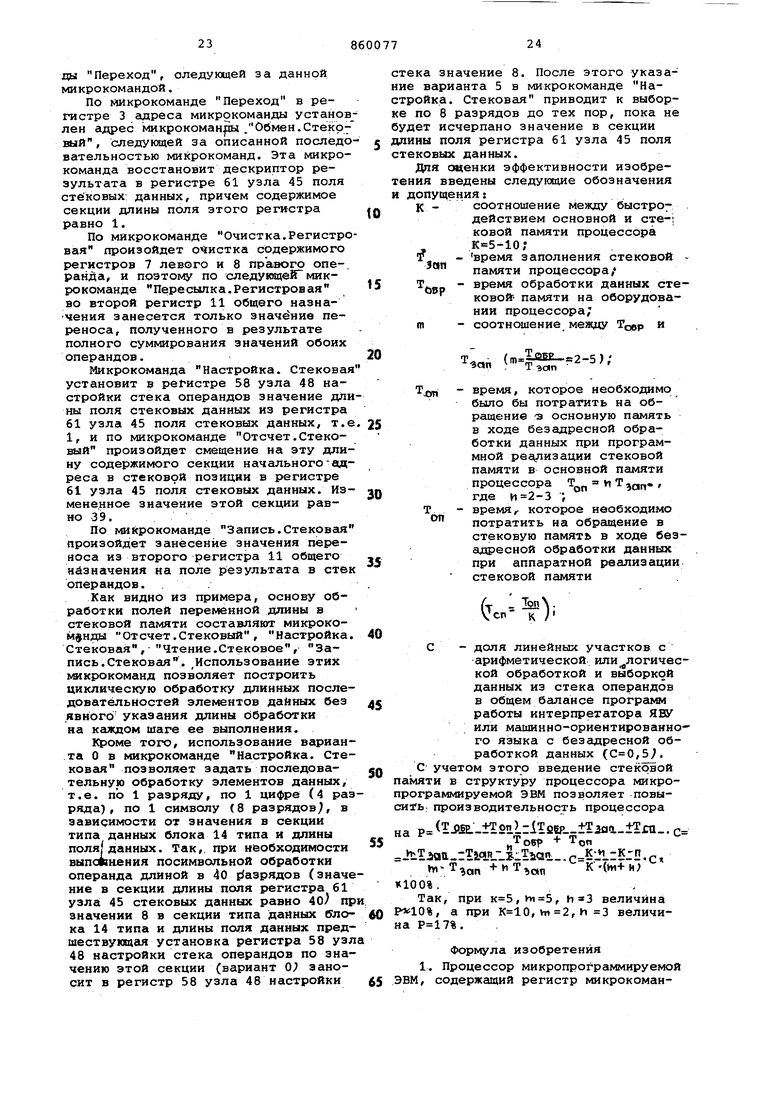

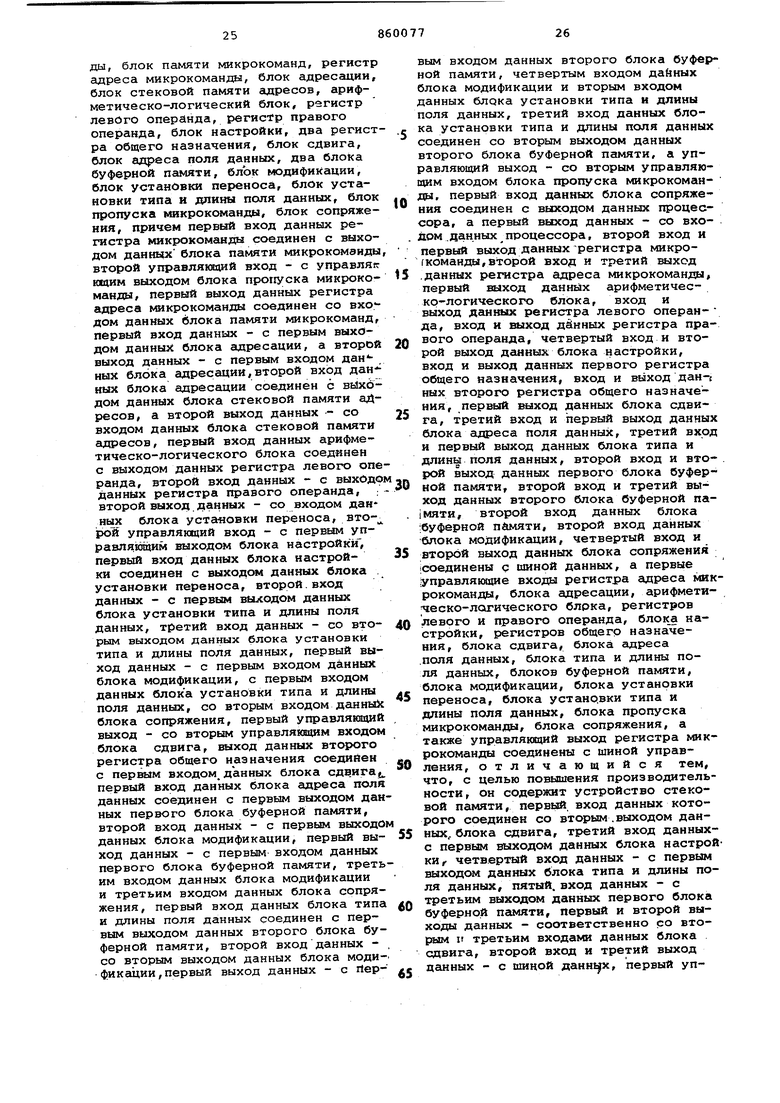

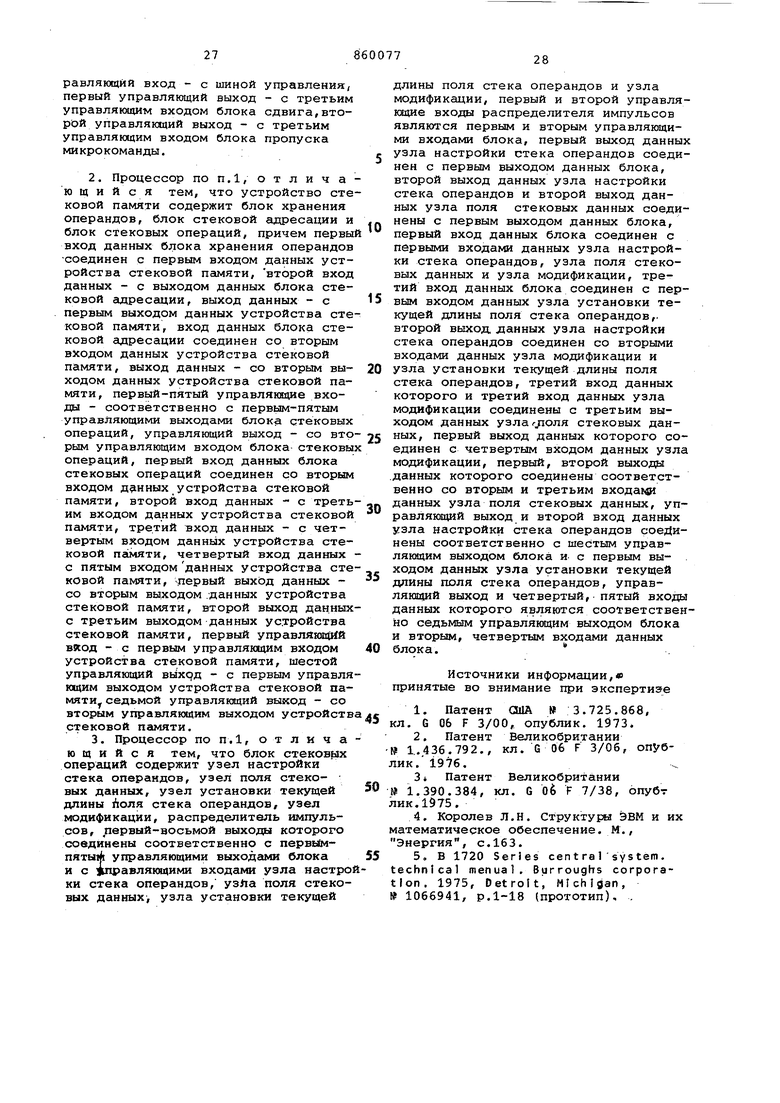

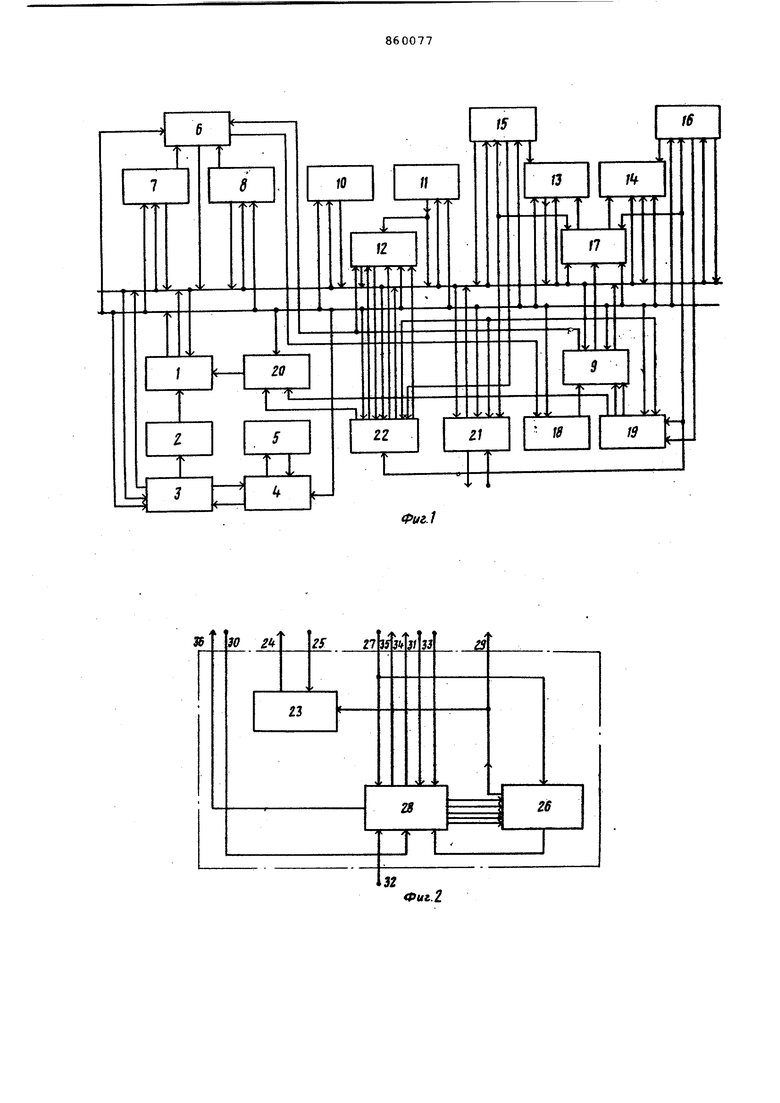

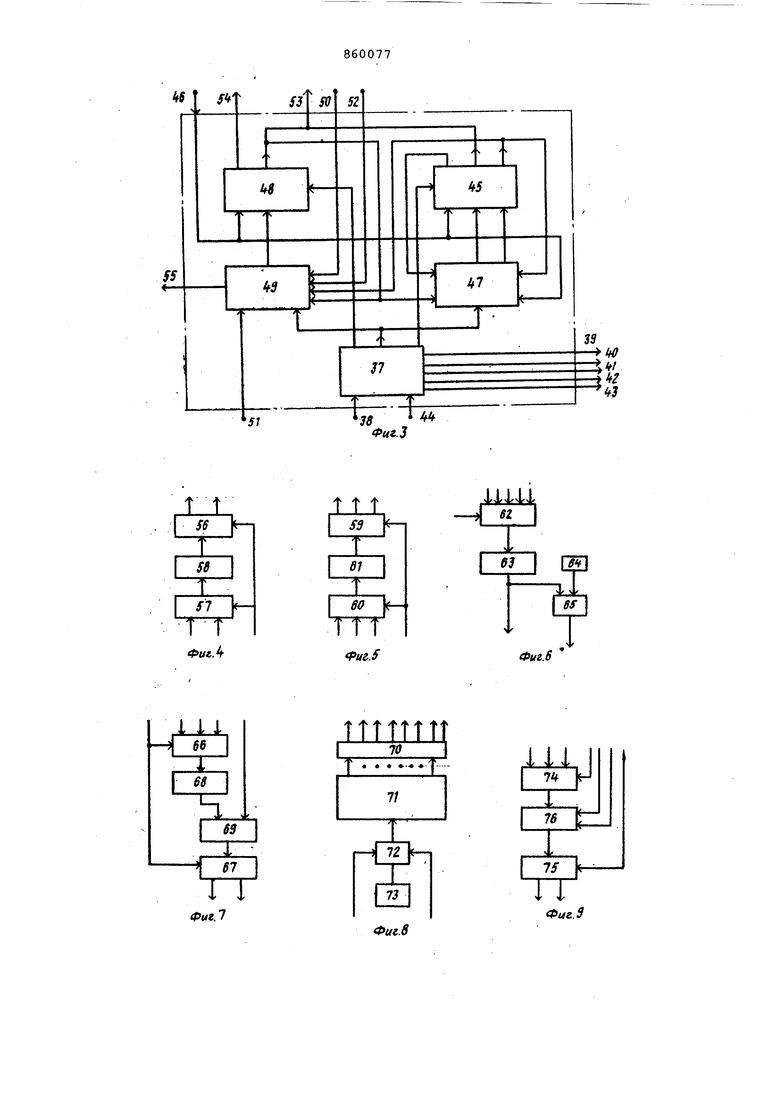

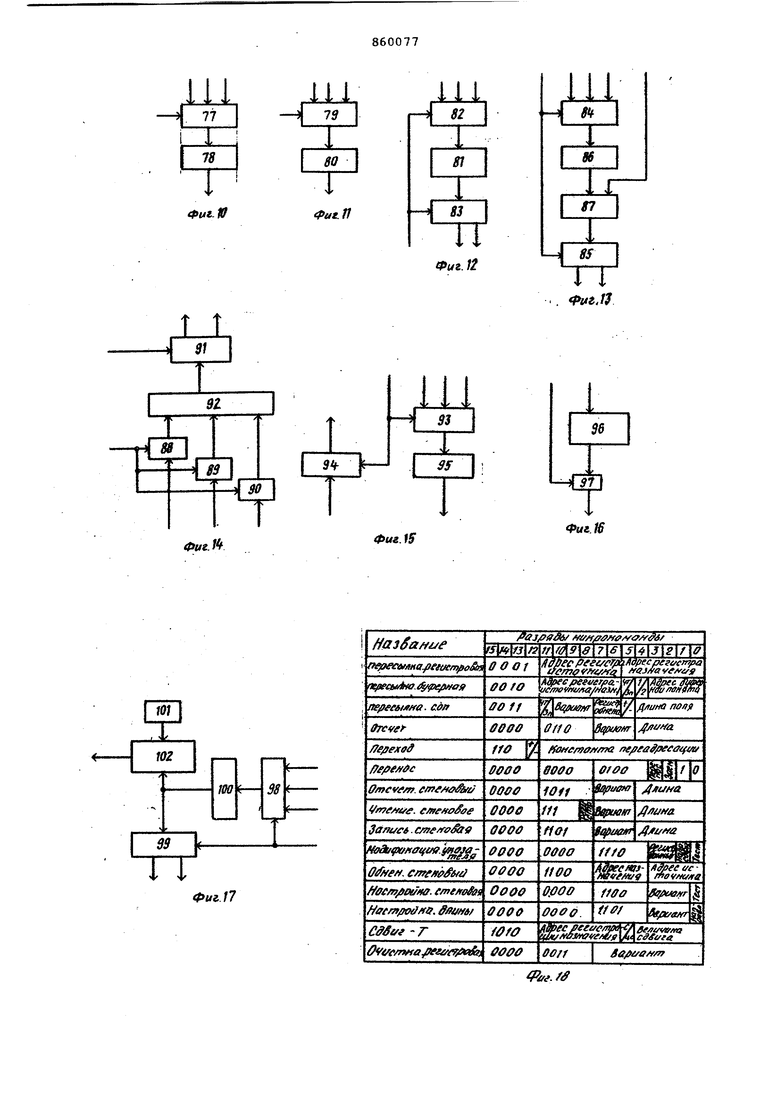

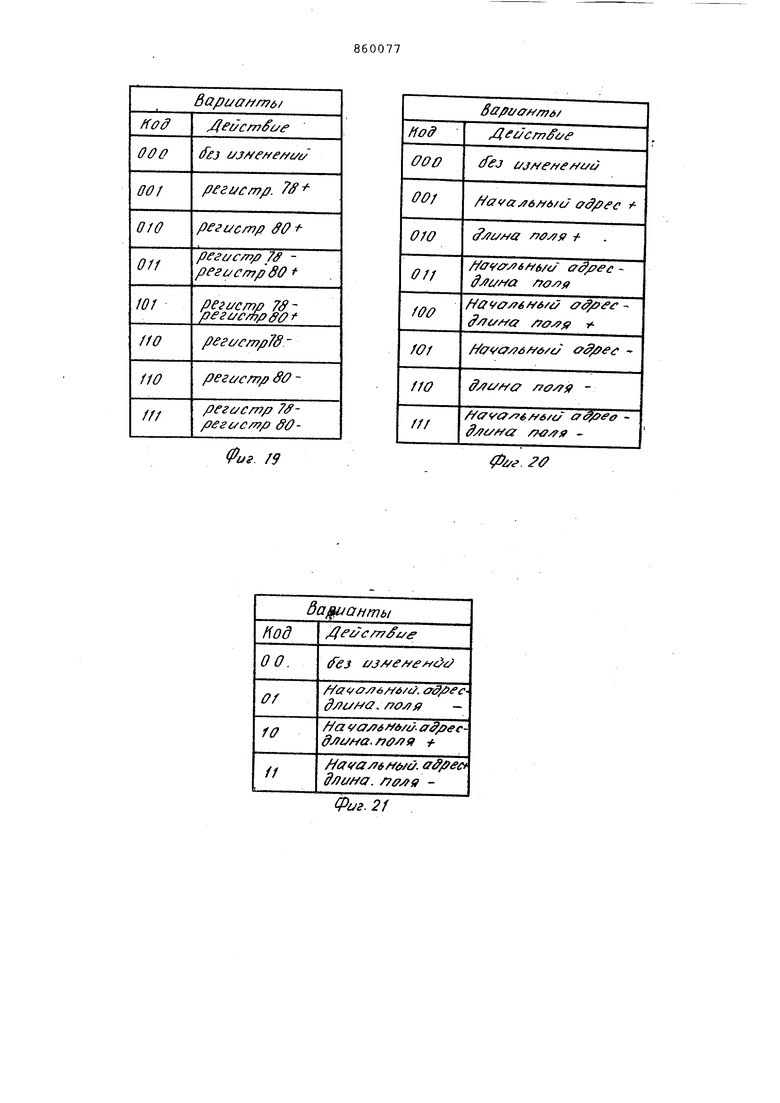

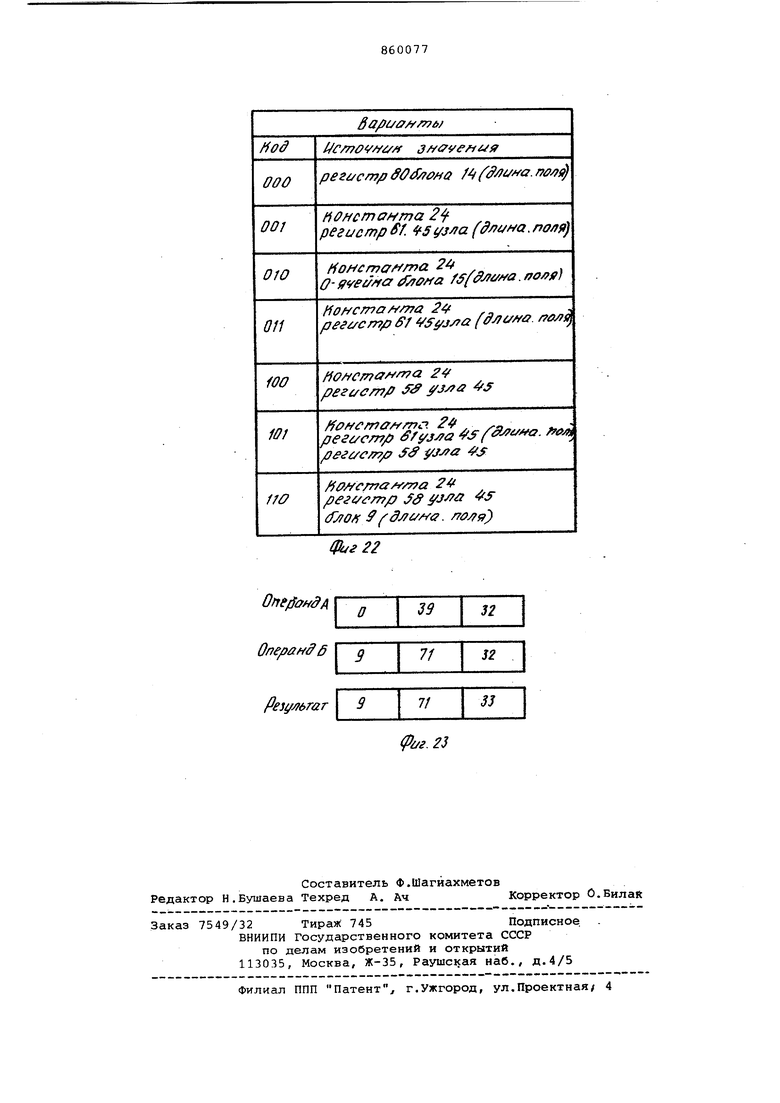

На фиг.1 представлена структурная |схема процессора на фиг.2 - струк1турная схема устройства стековой па|мяти; на фиг.З - структурная схема блока стековых операций; на фиг.4 вариант выполнения узла настройки стека операндов , на фиг.З - вариант выполнения узла поля стековых данHt, на фиг. б - вариант выполнения узла установки текущей длины поля стека операндоЁ на фиг.7 - вариант выполнения узла модификации, на фиг.8 - вариант выполнения распределителя импульсов; на фиг.9 - вариант выполнения блока сдвига; на фиг.10 вариант выполнения блока адреса поля данных; на фиг.11 - вариант выполне.ния блока типа и длины поля данных/ на фиг.12 - вариант выполнения блока буферной памяти; на фиг.13 - вариант выполнения блока модификации; на фиг.14 - вариант выполнения блока 1настр9йки; на фиг.15 - вариант выполнения блока сопряжения; на фиг.1бвариа41т выполнения блока установки перен|рс.а; на фиг. 17 - вариант выполнения блока установки и длины поля данных; на фиг.18 - форматы отдельных микрокоманд процессора; на фиг.19 - варианты модификгщии значений в регистре блока адреса поля данных и регистре блока типа и длины поля данных; .на фиг.2О - варианты. модификации значений в регистре блока типа и длины поля стекойых данных

по микрокоманде Отсчет.Стековый ; на фиг.21 - варианты модификации значений в регистре блока типа и длины поля стековых данных по микрокомандам Чтение.Стековое и Запись.Стег с ковая , на фиг. 22 - варианты формирования значения в регистре блока настройки стека по микрокоманде Настройка. Стековая ; на фиг.23 - форматы дескрипторов операндов и реQ зультата, используемых в демонтируемом примере выполнения операции сложения двух операндов.

Процессор микропрограммируемой ЭВМ содержит (фигЛ) регистр 1 микрокоманды, блок 2 памяти микрокоманд,

5 регистр 3 адреса микрокоманды, блок. 4 адресации,блок 5 стековой памяти . адресов арифметическо-логический блок б, регистр 7 левого и регистр 8 правого операнда, блок 9 настройки,

0 регистры 10 и 11 общего назначения, блок 12 сдвига, блок 13 адреса поля данных, блок 14 типа и длины поля данных, первый 15 и втсчрой 16 блоки буферной памяти, блок 17 модификации,

5 блок 18 установки переноса, блок 19 установки типа и длины поля данных, блок 20 пропуска микрокоманды, блок 21 сопряжения и устройство 22 стековой пошяти операндов.

.j Устройство стековой памяти операндов содержит (фиг.2} блок 23 хранения операндов, выход 24 данных, вход 25 данных, блок 26 стековой адресации, вход 27 данных, блок 28 стековых операций, выход 29, входы 30-33, выходы 34-36.

Блок стековых операций содержит (фиг.6) распределитель импульсов 37, вход 38, выходы 39-43, вход 44, узел 45 поля стековых данных, вход 46,

0 узел 47 модификации, узел 48 настройки стека операндов, узел 49 установки текущей длины поля стека орерандов, входы 50-52, вьйходы 53-55. Узел настройки стека операндов

J может быть выполнен в виде (фиг.4) коммутаторов 56 и 57 и регистра 58.

Узел поля стековых данных (фиг.5) может быть выполнен в виде коммутаторов , и 60 и регистра 61.

Q узел установки текущей длины поля стека операндов может быть выполнен в виде (фиг.6)-коммутатора б2,регист-, ров63 и 64 и схемы 65 сравнения.

Узел модификёщии может быть выполнен в виде (фиг.7) коммутаторов

5 66 к 67, регистра 68 и сумматора 69.

Распределитель импульсов может .быть выполнен в виде (фиг.8) дешифратора 70, счетчика 71, элемента -И 72 и генератора импульсов 73. :

Q Блок сдвига может быть выполнен в виде (фиг.9) коммутаторов 74 и 75 и регистра 76.

Нлок адреса пОля данных может быть выполнен в виде (фиг.10) коммутатора 77 и регистра 78. Аналогичным образом может быть настроен и блок типа и длины поля данных (фиг.11), содержащий и коммутатор 79 и регистр 80,

Блоки буферной памяти могут быть выполнены в виде (фиг.12) узла 81 хранения и двух коммутаторов 82 и 83. ,

Блок модификации может быть выполнен в виде (фиг.13) коммутаторов 84 и 85, регистра 86 и сумматора 87.

БЛОК настройки может быть выполнен в виде (фиг.14) коммутаторов 8891 и регистра 92.

Блок сопряжения (фиг.15) может быть выполнен в виде коммутатора 93 и регистров 94 и 95.

Блок установки переноса (фиг.16) в простейшем виде может представлять собой триггер 96 и элемент И 97.

Блок установки типа и длины .поля .данных может представлять собой совокупность (фиг.17) коммутаторов 98 и 99, регистров 100 и 101 и схемы 102 сравнения.

Блок пропуска микрокоманды в прос тейшем случае может представлять собой элемент ИЛИ на три входа.

На Основании содержимого полей регистра 1 микрокоманды вырабатываются различные управляющие сигналы поступающие по шине управления в блоки процессора и организуквдие его .работу. В частности, эти сигналы управляют связью по данным между различными блоками процессора, реализуемой через общую шину данных и заключающейся в подключении, к ее входам выхода одного из связанных с ней блоков для передачи значения этого блока на выход шины данных и записи этого значения в конкретный блок.

Микрокоманды хранятся в блоке 2 памяти микрокоманд и по одной выбираются в регистр 1 микрокоманды для их выполнения. Блок 2 памяти микрокоманд организован по словам (16-ти разрядным): адрес очередной выполняемой микрокоманды находится в регистре 3 адреса микрокоманда. Обычно значение в регистре 3 адреса микрокоманды увеличивается на единицу после каждой выполняемой микрокоманды, но при нарушении линейного следования микрокоманд новое значение адреса очередной микрокоманды может быть установлено в регистре 3 адреса микрокоманды как прямой заЙАЛкой содержимого некоторого регистра через общую шину данных, так и выполнением микрокоманд перехода и обращения к подпрограмме, вызывающих смещения содержимого регистра 3 адреса микрокоманды на заданную величину. В случае выполнения микрокоманды обращения к подпрограмме исходное значение регистра 3 адреса микрокоманды, заключающее адрес микрокоманды, следующей за микрокомандой обращения к подпрограмме, через блок 4 адресации предварительно запоминается э вершине блока 5, работающего по принципу Первый пришел первый вышел. При выходе из подпрограммы это значение восстанавливается в регистре 3 адреса микрокоманды из блока .5 стековой памяти адресов через блок 4 адресации.

Арифметические и логические операции реализуются в процессоре в арифметическо-логическом блоке б, при Кс1ждом обращении к которому на его первом выходе данных, связанном с общей шиной данных, выраба щвается

значение одной из нескольких арифметических или логических функций над содержимым регистров 7 и 8 левого и правого операнда.

Этими функциями являются Сумма,

Разность, Инверсия левого операнда, Ичверсия правого операнда, Сумма по МОДУЛЮ2, Конъюнкция, Маскирование левого операнда, Маскирование правого операнда,

Дизъюнкция, причем каждая из этих функций может быть указана в микрокомандах в качестве регистра источника данных. Управляквдая информация, необходимая для выполнения

указанных функций и содержащая значение переноса-заема при выполнении арифметических операций, тип обрабатываемой информации (двоичный десятичный) , а также длина обрабатываемого поля данных поступает из

блока 9 настройки через второй управляющий вход арифметическо-логического блока 6.

Первый 10 и второй 11 регистры общего назначения предназначены дЛя

работы в качестве универсальных регистров. Каждый из этих регистров разбит на отдельные 4-разрядные секции, самостоятельно адресуемле в микрокомандах. На .базе второго регистра 11 общего назначения реализован блок 12 сдвига, выполняющий циклический/ациклический сдвиг влево содержимого этого регистра на произвольное число разрядов, а также

выделение поля произвольного размера из этого регистра. Требуемая величина сдвига, а также размер вьвделяемого поля задаются регистром 1 микрокоманды или блоком 9 настройки и поступают в блок 12 сдвига соответственно через ..его первый или второй управляивдие входы, выделяемое поле выдается всегда прижатым вправо.

Адресация к полю оперативной памяти посредством блока. 13 адреса поля данных происходит с точностью до бита, а тип данных (бит, цифра) р полная поля в битгис задгиот- ся соответствукнцими секциями блока:

14 типа и Д.ЛИНЫ поля данных.

Каждый блок буферной памяти хранит до 16 слов, и обращения в буферную память (запись или чтение) может происходить либо в каждый блок раздельно, либо одновременно в оба блока к словам удвоенной длины. Обращение в первый блок 15 буферной памяти может происходить из блока 13 адреса поля данных по первому входу или выходу данных блока 15, а также через кодовую шину данных по второму входу или выходу данных этого блока; обращение во второй блок 16 буферной памяти может происходить из блока 14 типа и длины поля данных по первому входу или выходу данных блока 16, а также через кодовую шину данных по второму входу или выходу данных блока 16; одновремен ное обращение в оба блока буферной памяти происходит из блока 13 адреса поля данных и блока 14 типа и длины поля данных соответственно в первый блок 15 и второй блок 16 буферной памяти по их первым входам или выходам данных.

Модификация значений в блоке 13 адреса поля данных и в блоке 14 типа и длины поля данных выполняется блоком 17 модификации. Параметр модификации этих значений передается и блока 9 настройки или через кодовую шину данных соответственно по первому или второму входу данных блока 17 а исходные значения указанных блоков

13и 14 поступают соответственно по третьему и четвертому входу данных блока 17 модификации.

Значением переноса, формируемым блоком 18 установки переноса, может быть либо значение переноса/заема, вырабатываемое арифметическо-логическим блоком 6 и поступающее через вход данных блок 18 установки переноса, либо значение 1 или О, устанавливаемое в соответствии с управляинцим сигналом, поступающим по шине управления через управляющий вход блока 18 установки переноса.

Исходными данными, поступающими на входы блока 19 установки типа и длины поля данных для формирования указанных величин, являются текущее значение этих величин, содержащееся в блоке 9 настройки, а также значени этих величин, содержащиеся в блоке

14типа и длины поля данных и в фиксированной (нулевой) ячейке второго блок 16 буферной памяти.

Формирование величины длины поля данных в блоке 9 настройки сопровождается анализом этой величины на нулевое значение, что может вызывать, в соответствии с семантикой микрокоманды, блокировку выполнения очередной микрокоманды в регистре 1 :ликрокоманды, ее пропуск и переход к выполнению следующей микрокоманды.

Указанные действия реализуются блоко 20 пропуска микрокоманды; необходимая информация поступает с управляющего выхода блока 19 установки типа и длины поля данных через второй управляющий вход блока 20 пропуска мик рокоманды.

Обращение к полю основной памяти процессора (чтение или запись) реализуется блоком 21 сопряжения через ег первый вход и первый выход данных. Длина поля может быть произвольной, но не должна превышать 24 бита для оного обращения к основной памяти, он поступает на второй вход данных блока 21 из блока 9 настройки; начальны адрес поля данных, задаваемый с точностью до бита, поступает из блока 13 адреса поля данных на третий . вход данных блока 21 сопряжения.

Реализация языков высокого уровня в микропрограммируемой ЭВМ, предусматривающая безадресную обработку данных, либо реализация машинно-ориентированных языков с безадресной обработкой данных предполагают организацию в основной памяти ЭВМ программно-управляемого стека операндов, обращение к которому происходит через его вершину. В ходе безадресной обработки данных происходит чтение требуемого числа операндов из стека операндов в регистры процессора, их соответствукнцая обработка, возможный возврат результата в вершину стека операндов, последующее извлечение из стека операндов очередной группы операндов, включая ранее запомненный результат, обработка этой группы и т.д. Выполнение перечисленных действий приводит к возрастанию числа обращений в основную память, особенно заметному в случае когда формат данных- превышает формат регистров процессора.

Включение в состав процессора устройства 22 стековой памяти, являкнцегося аппаратной реализацией вершины стека операндов и микрокоманд работы с ним, позволяет сократить число обращений в основную память при безадресной-обработке данных и упростить работу со стекой операндов. .

Елок 23 хранения операндов данного блока выполняет функции вершины стека операндов и представляет собой байтовую память, адресуемую с точностью до бита, причем каждое обращение в такую память всегда сопровождается одновременным выделением 4 байтов, включая начальный байт адресуемого поля. Информация, считываемая из стека операндов, через первый выход данных блока 23 и первый выход данных 24 устройства 22 стековой памяти поступает в блок 12 сдвига; занесение информации в стек операндов происходит также из блока

12 сдвига через первый вход данных 25 устройства 22 стековой памяти и первый вход данных блока 23.

Операнд в стековой памяти хранится в позиций стека, представляющей участок байтовой памяти со смежными адресами байтов, по одному операнду в позиции-стека. Максимальная длина операнда зависит от размера позиции стека. Размер позиции стека в блоке 23 не является постоянным и настраивается программным способом. Такая настройка, а также формирование адреса обращения в блоке 23 и контроль за правильностью такого обращения осуществляются блоком 26 стековой адресации.

Исходная информация об адресе обращения в стек операндов поступает на вход данных блока 26 стековой адресации с шины данных через второй вход 27 данных устройства 22 стековой памяти, а управляющая информация, необходимая для формирования адреса обращения в блок 23, поступает на первый-пятый управляющие входы блока 26 стековой адресации из блока 28 стековых операций.

Обращение в стек- операндов может происходить только в пределах одной позиции.стека, что контролируется блоком 26 стековой адресации, и всякое пересечение стековой позиции сопровождается вьщачей соответству.ющего сигнала на управлякнций выход этого блока.

Адрес обращения в стек операндов, сформированный в блоке 26 стековой адресации, через выход данных этого блока поступает на второй вход данных блока 23, при этом пять младших разрядов адреса, задающие в считанных четырех байтах номер начального разряда адресуемого поля, через второй выход 29 данных устройства 22 стековой .памяти одновременно поступают в блок 12 сдвига для формирования константы сдвига поля, выделяемого из cTetca операндов.

Запуск выполнения микрокоманд работы со стеком операндов в устройстве 22 стековой памяти происходит через блок 28 стековых операций. Необходимая информация поступает в это устройство через первый управляющий вход 30, а также третий 31, четвертый 32 и пятый 33 входа данных устройства 22 стековой пемяттл выдача информации из блока 28 стековых операций на шину, данных происходит, через второй выход 34 данных, в блок сдвига 12 - через первый управляюйдай выход 35, а в блок 20 пропуска микрокоманды - через второй управляющий выход 36 устройства 22 стековой памяти .

Работа блока 28 стековых операций происходит под управлением распределителя 37 импульсов, активизируемого

по шине управления через первый управляющий вход 38 данного блока Распределитель 37 импульсов вырабатывает также ряд .управляющих сигналов, выдаваемых через первый 39, второй 40, - третий 41,. четвертый 42 и пятый 43 управляющие выходы блока 28 стековых операций в блок 26 стековой адресации. В свою очередь, из блока 26 стековой адресации в распределитель 37 импульсов через второй управляюtoщий вход 44 блока 28 стековых операций поступает управляющий сигнал, свидетельствукадий о пересечении гра- , ниц позиции стека или всего стека операндов при обращении к нему и блокирующий работу блока 28 стековых операций. . ,

Каждый операнд в стеке описывается дескриптором, указывакщим размещение и длину операнда (поля переменной длины) в позиции стека, а также положение этой позиции относительно вершины стека. Дескриптор текущего операнда стека хранится в узле 45 поля стековых данных, состоящем из

25 трех секций: смещения позиции, начального адреса в стековой позиции, длины поля, Первая секция задает смещение в байтах искомой позиции стека относительно вершины стека операндов, вторая секция - положение

0 начального (левого) бита поля, который отсчитывается в битах от начала позиции стека, третья секция - чиспо битов в поле.

Исходное значение заносится в узел 45 поля стековых данных с шины данных через первый вход 46 данных блока 28 стековых операций и первый вход данных узла 45 . Модификация

0 содержимого узла 45 Поля стековых данных, в частности секций начального адреса в стековой позиции и длины йоля, выполняется узлом 47 модификации стека операндов соответственно по второму и третьему входу данных этого узла. Исходные значения указанных секций поступают в узел 47 модификации стека операндов по ее первому и второму входу данных

0 соответственно, а п эаметр модификаций поступает с шины данных через первый вход 46 данных блока 28 стековых операций и третий вход данных узла 47 модификации стека операндов или из

узла 48 настройки стекаоперандов

через четвертый вход данных узла 47 модификации стека операндов.

Значение текущей длины поля стека операндов заносится в узел 4в настройки стека операндов с шины данных через первый вход. 46 данных блока 28 стековых операций и первый вход данных этого узла, а также может формироваться узлом 49 устанбвки текущей длины поля стека операндов.

Исходные данные поступают в ЭТУ схему из блока 9 настройки Хзначение длины обрабатываемого поля),блока 14 типа и длины поля данных (значение длины поля данных), фиксированной (нулевой) ячейки первого блока 15 буферной памяти (значение длины поля данных) соответственно через второй 50, третий 51,четвертый 52 входы данных блока 28 стековых операций и первый, второй, третий входы данных узла 49 установки тегсущей длины поля стека операндов, а -также из узла 45 поля стековых дан.ньзх (значение длины поля) и узла 48 настройки стека операндов сойтветственно через четвертый и пятый входы данных узла 49.

Содержимое узла 45 поля стековых данных через третий выход данных этого узла, а такж первый выход данных 53 блока 28стековых операций и второй выход данных 34 устройства 22 стековой памяти поступает на шину данных, откуда может подаватся в блок стековой адресации 26 для формирования адреса обращения в блок 23. Содержимое узла 48 настройки стека операндов через первый выход 53 данных блока 28 стековых операций и второй выход 54 данных устройства 22 стековой памяти поступает на шину данных, а через-шестой упразлякяций выход 54 блока 28 стековых операций и первый управлякйций выход 35 устройства 22 стековой памяти поступает в блок 12 сдвига- в качестве возможного размера поля, выделяемого из стака операндов.

Формирование значения в узле 40 настройки стека операндов сопровождается анализом этой величины на нулевое значение, что может вызывать, в соответствии р семантикой микрокоманды, блокировку выполнения очередной микрокоманды в 5егистре 1 микрокоманды, ее пропуск и переход к выполнению следующей микрокоманды. Необходимая для этого информация формируется в узле 49 установки текущей длины поля стека операндов и с ее управляющего выхода через седьмой управлянвдий выход 55 блока 28 стековых операций и второй управляющий выход 36 устройства 22 стековой памяти поступает в блок 20 пропуска микг рокомандн.

Работу отдельных частей процессора мвжно пояснить на примере исполнения отдельных микрокоманд или некоторой типичной последовательности микрокоманд, причем объектом действия будут, в основном, операнды из стековой памяти и дескрипторы, их описывающие.

Каждая микрокоманда состоит из 16 битов (см.фиг.18), Часть зтих битов, от 3 до 12, содержит код

микрокоманды. Оставшиеся биты указы вают конкретные регистры или их адресуемые части, различные выходные функции блока 6, варианты исполнени некоторых микрокоманд или длины полей. Например, первая микрокоманда Пересылка. Регистровая (фиг.18) кодируется 0001 в 4-х старших битовых позициях микрокоманды. Следующи шесть битов указывают источник пересылаемых данных (регистр или его адресуемая часть), а оставшиеся шесть битов - приемник этих данных (регистр или его адресуемая часть).

Выходные функции блока 6 могут быть указаны только в качестве источников данных. Такое указание задает тип выполняемой в блоке 6 операции над содержимым регистров 7 левого и 8 правого операндов с исползованием блока 9 настройки, определякяцего значение п реноса/заема для арифметических операций, а также значение типа обрабатываемых данных и длину операндов.

Микрокоманда Пересылка. Буферная управляет передачей данных между регистром, указанным в 6-11 разрядах микрокоманды, и любым из 16 слов одного из блоков буферной памяти, указанным в разрядах 0-3. Разряд 4 указывает, с каким блоком, первым 15 или вторым 16 буферной памяти проводится обмен; разряд 5 задает направление обмена, из регистра в буферную память или наоборот.

Микрокоманда Пересылка.С.ОП управляет . обменом с основной памятью. Разряд 11 указывает режим обращения в основную память (чтение или запись разрядаг 6 и 7 задают регистр для обА4ена с основной памятью: регистр 7 левого, 8 правого операнда, пер- вый 10, второй 11 регистр общего назначения, разряды 0-4 задают число битов в читаемом (записываемом) поле - от О до 24. Если в разрядах 0-4 задано значение О, то число передаваемых битов задается секцией длны обрабатываемого поля блока 9 наг стройки.

При длине операнда, превышающей 24 бита, извлечение полного операнд происходит за несколько обращений к :основной памяти, причем каждое та:кое обращение должно сопровождаться перемещением начальной точки отсчетаадреса на величину извлеченного поля, т.е. модификацией значений в блоке 13 адреса поля данных и в секции длины поля данных блока 14типа и длины поля данных. Разряды 8-10 микрокоманды зещеиот варианты модификации значений в регистрах 78 и 80 (фиг.19). Символы 1 и - задают направление изменения значений, увеличение или уменьшение соответственно.

Микрокоманда Отсчет задает модификацию значений в блоке 13 адреса поля данных и в секции длины поля данных блока 14 типа и длины поля данных. Разряды 5-7 выполняют ту же функцию, что и разряды 8-10 для предыдущей микрокоманды. Разряды 0-4 задают .константу модификации, а в случае нулевого значения используется содержимое секции длины обрабатываемого поля регистра блока 9 наг стройки.

Микрокоманда Переход задает, на какую вяичину (разряды 0-11) и с каким (разряд 12) следует изменить значение в регистре 3 адрег са микрокссманды: младшие 12 разрядов микрокомаядш суьлдарукггся или вычитаются из младатк разрядов регистра 3 адреса микрокоманда.

Микрокоманда Перенос задает один из четырех возможных вариантов установки значейия в секции переноса заема блока 9 настройки (разряды 0-3 микрокоманды): по значению переноса на выходе блока б (разряд 3), по значению заема на соответствующем выходе того же блока (разряд 2) в , 1 (разряд 1), в О (разряд О) . Микрокоманда Отсчет. Стековый выполняет модификацию значений в узл 45 поля стековых данных: секции начального адреса в стековой позиции и, длины поля. Констант а модификации.задается разрядами 0-4 микрокоманда, а в случае их нулевого значения узлом 48 настройки стека операндов. Варианты модификации задаются разрядами 5-7 микрокоманды ( фиг.20) . Значение константы модификации находится в пределах 0-24.

Микрокоманда Чтение. Стековое управляет выборкой поля данных из стека операндов. Разряд В микрокоман yjfa задает имя регистра- назначенйя (регистр 7 левого или 8 прямого операнда) , разряды 0-4 - длину считываемого поля (в пределах 0-24) . Если заданное значение длины считываемого поля равно О, то для указания длины поля используется значение из узла 48 настройки стека операндов. Разряды 6-7 микрокоманды задают 4 варианта модификсщии значений начального адреса в стековой позиции и длины поля в узле 45 поля «стековых данных (фиг.21).

Микрокоманда Запись. Стековая управляет пересылкой поля из регистра 11 общего назначения в одну из позиций стековой памяти. Позиция, в которую идет пересылка, задается величиной смещения отйосительно верхней позиции стека. Эта величина содержится в секции смещения, позиции блока 45 поля стековых данных. Положение записываемого поля и его Общая длина указываются значениями в секцйях начального адреса в стековой позиции и длины поля этого же лока. Разряды 0-4 микрокоманды задают длину поля, записываемого при данном обращении в стек операндов, а в случае нулевого значения этих разрядов используется значение из узла 48 настройки модификации значений начального адреса в стековой позиции идлины толя в узле 45 поля стековых данных. Зти варианш совпадают с вгфиантами для микрокоманда Чтение. Стековое.

Микрокоманда Модификация. Указателя управляет перемещением указателя стека. Разряды. 2-3 микрокоманды задают либо имя одного вэ регистров .(7 левого, 8 правого операнда, первого 10 общего назначения), значение которого используется для мбдификАдни указателя стека, 1&бО модификацию указателя стека на одну позицию стека-, разряд 1 задает направление модификации (вверх или разряд О задает необходимость проверки, находится ли модифицированное значение указателя стека в допустимых Яределай, т.е. ли оно 1знутрь стека.

Микрокоманда Обмен. Стековый управляет обменом значениями между узлом 45 поля стековых данных и двумя слова первого блока 15 буферной памяти, причем одно из них является источником, а другое - назначением, .т.е. из слова-источника в узел 45 поля стековых данных загружается зна:чение, а исходное значение этого узла сохраняется в слове-назначении. Разряды 0-3 микрокоманды задают адрес слова-источника, а 4-7 .слова-назначения. Данная микрокомавда может использоваться, например, для сменЕ:) в узле 45 поля стековых данных дескрипторов стековых данных, хранимых в первом блоке 15 буферной памяти.

Микрокоманда Настройка. Стековая управляет заполнением узла 48 настройки стека операндов значением согласно представленным на фиг.22 вариантам Разряды 1-3 микрокоманды задают номер варианта, разряд О - проверку условия,является ли значение для данного регистра нулевым.При невыполнении условия происходит пропуск очередной микрокоманды.В вариантах . (1-6) ,содержеацих несколько источников зн.ачений,предусматривается занесение наименьшего из задаваемых значений.

Микрокоманда Настройка. Длины управляет обменом между узлом48 настройки стекаоперандов и одним из регистров; 7 левого, 8. правого one- ранда, 9 настройки, первым 10, вторым 11 общего назначения. Разряды. 1-3 микрокоманды задают имя регистра, с которым происходит обме, а разряд О задает направление обмена - из узла 48 настройки стека операндов или в этот узел. Микрокоманда Сдвиг-Т управляет циклическим или ациклически:-: сдвигом влево содержимого регистра 11 общего назначения и записью сдвинутого зна чёния в указанный разрядами 6-11 регистр назначения. Тип сдвига (циклический или ациклический) задается разрядом 5; разряды 0-4 задают константу сдвига (0-24). В случае нулево го значения в разрядах 0-4 в качестве | онстанты сдвига используется содержимое блока 9 настройки. Микрокоманда Очистка.Регистровая управляет сбросом в О содержимого регистров: 7 левого, 8 правого операнда, блока 9 настройки, первого 10, второго 11 общего назначения, блока 13 адреса поля данных, блока 14 типа и длины поля данных (в отдельности по каждой из его секций) в произвольном наборе. Требуемый набор регистров и блоков, подлежащих очистке, задается полем вариантов микрокоманды (разряды 0-7). Использование описанных микрокоманд для обработки произвольных полей стековых данных может быть пояснено на примере одного из вариантов выполнения операции сложения двух операндов одинаковой длины {А и Б), находящихся в вершине стековой памяти. Пусть операнд А размещен в верхней позиции стека, а операнд Б - в следующей, т.е. непосредственно под верхней позицией, и результат должен быть занесен в стек операндов на мес то исходных операндов. Пусть задан некоторый размер позиции стековой памяти, например, 9 байт, и размещение операндов внутрипозиции стека, например операнд А занимает разряды 8-39 (отсчет разрядов в позиции веде ся слева направо, начиная с 0 операнд Б - разряды 40-71. Дескрипторы, описывающие операнды А и В и результат, могут, например, иметь формат, показанный на фиг.23, и размещаться: для операнда А - в регистре 61 узла 45 поля стековых данных, для операнда Б - в слове с адресом О первого блока 15 буферной памяти, для результата - в слове с адресом 1 того же блока буферной памяти.. При этом поля секций смещения позиции этих дескрипторов содержат: для «Операнда А - нули,для операнда Б и зультата - значение, задаклцее смещение указателя на одну позицию стека вниз, в частности 9байт. Поскольку операция сложения выполняется, начиная с младших разрядов, то дескрипторы должны задавать начальные адреса полей операндов и результата, увеличенные на полную длину еще не обработанной части п6ле Для выборки ПОЛЯ на обработку текущий адрес поля должен быть уменьшен на текущую длину обработки, т.к. выборка поля всегда идет в одном направлении - от адреса, указанного в секции начального адреса в стековой позиции регистра 61 узла 45 поля стековых данных, в направлении возрастания адресов разрядов в позиции стека. Поэтому регистр 61 узла 45 поля стековых данных-в начальный момент содержит: в секции смещения позиции - О, в секции начального адреса в. стековой позиции - 39, т.е. начальный адрес поля операнда А (адрес разряда с номером 8, увеличенный на полную длину поля операнда), в секции длины поля - 32, т.е. длину поля операнда А. Слово О первого блока 15 буферн й памяти содержит код, привязка которого к формату регистра 61 узла 45 поля стековых данных имеет вид: в секции смещения позиции - 9, в секции начального адреса в стековой позиции - 71, в секции длины поля 32. Слово 1 первого блока 15 буферной памяти содержит код, привязка которого к формату регистра 61 узла 45 поля стековых данных соответственно имеет вид - 9, 71, 33. Содержимое последнего слова указывает, что результат операции размещен на месте операнда Б, т.е. его крайним правым разрядом будет разряд 71, а увеличение на 1 длины поля результата fno отношению к длине поля операндов преследует цель запомнить возможный перенос при сложении старших разрядов, т.е. в стеке операндов результат занимает разряды 39-71. Поскольку предлагаемый процессор является микропрограммируемым, то обычнад операция суммирования двух операндов и занесения результата на их место реализуется микропрограммой, один.из вариантов которой .может включать следующую последовательность микрокоманд: Начсшо - Настройка. Стековая по длине. Поля с проверкой, Переход на продолжение ; Отсчет. Стековый в минус по начальному. Адрес Чтение. Стековое в регистр. 7 и минус по длине. Обмен. Стековый из 0В Отсчет. Стековый .в минус по начальному. Адресу ; Чтение. Стековое в регистр.8 и минус по длине.Поля , Настройка. Длины в регистр. Пересылка. Регистровая из сумма в регистр. Перенос переноса ; Обмен.Стековый из i в Отсчет.Стековый в минус по начальному .Адресу , Запись.Стековая и минус по длине. Обмен.Стековый из 2 в 1, Переход на начало. Продолжение - Обмен.Стековый из 1в О. Очистка. Регистровая для регистр,7 и регистр.8, Пересылка, Регистровая из сумма в регистр.11, Настройка.Стековая по длине, Отсчет.Стековый .в минус по лачально му. Адресу, Запись.Стековая . Конец. По первой микрокоманде в регистре 58 узла 4Р настройк|1 стека операндов устанавливается длина считываемого поля стековых данных (вариант 1) и проверяется, не исчерпаны ли операнды. Поскольку значение в секции длины поля регистра 61 узла 45 поля стековых данных равно 32, то в регис тре 58 узла 48 настройки стека операндов устанавливается значение 24. Так как содержимое регистра 58 узла 48 настройки стека операндов - микрокоманда Переход пропускается Микрокоманда Отсчет.Стековый изменяет содержимое секции начального адреса в стековой позиции в регис ре 61 узла 45 поля стековых данных на содержимое регистра 58 узла 48 на стройки стека операндов. Для операнд А измененное значение этой секции будет равно 16. По микрокоманде Чтение.Стековое в регистр 7 левого операнда считываются 24 разряда операнда А разряды 0-4 микрокоманды установлены в О, по этому длину поля операнда определяет содержимое регистра 58 узла 48 настройки стека операндов, а значение в секции длины поля регистра 61 узла 45 поля стековых данных уменьшается на 24 (вариант 1). Следующая микрокоманда заменяет дескриптор операнда А, находящийся в регистре 61 узла 45 поля стековых данных, дескриптором операнда Б (зна чение из регистра 61 узла 45 поля стековых данных засылается в слово 2первого блока 15 буферной памяти, а в этот регистр загружается значение из слова О той же секции). Далее исполняются микрокоманды Отсчет.Стековый и Чтение.Стековое 3регистр 8 правого операнда. За исключением задания начального адреса считываемого поля, исполнение этих микрокоманд совпадает с ранее рассмотренным исполнением аналогичной пары этих микрокоманд. В результате исполнения предыдущих микрокоманд в регистры 7 левого и 8 правого операнда занесены по 24 разряда значений операндов А и Б. Следующая микрокоманда Настройка Длины передает в блок 9 настройки из регистра 58 узла 48 настройки сте ка операндов длину частей операндов А и Б, загруженных в регистры 7 левого и 8 правого операнда для выполнения операции в блоке 6. На выходе этого блока формируются значение переноса и двоичная сумма содержимого регистров 7 левого и 8 правого операнда. Длина результата, определяемая значением блока 9 настройки, в данном случае составляет 24 разряда. По микрокоманде Пересылка.Регист-, ровая полученная сумма передается во второй регистр 11 общего назначения, а по микрокоманде Перенос в секцию переноса/заема блока 9 настройки передается значение двоичного переноса, 1 или 0. Это значение переноса будет использовано при последунвдем суммировании очередных полей операндов А и Б. Следующая микрокоманда Обмен. Стековый производит замену в регистре 61 узла 45 поля стековых данных дескриптора операнда Б на дескриптор результата, засылая текущее содержимое этого регистра в слово О первого блока 15 буферной памяти и загружая этот регистр значением из слова i указанного блока. По микрокоманде Отсчет.Стековый значение в секции начального адреса в стековой позиции регистра 61 узла 45 поля стековых данных изменяется на содержимое регистра 58 узла 48 настройки стека операндов. В данном случае измененное значение этой секции равно 48. Микрокоманда Запись. Стековая выполняет заююь поля из регистра 11 общего назначения в стек операндов по адресу, указанному в регистре 61 узла 45 поля стековых данных, т.е. в дескрипторе результата, и модифицирует значение в секции длины поля этого регистра на длину записываемого поля. В данном случае длина записиваемого поля задается регистром 58 узла 48 настройки стека операндов и составляет 24 разряда. В результате выполнения данной микрокоманды 24 младших разряда операнда Б згаменяются Е стеке операндов 24 младишми разрядами результата. Следующая QIкpoкoмaндa Обмен. Стековый заменяет в регистре 61 уз;ла 45 поля стековых дгшных дескриптор результата на дескр иптор операнда А. Микрокоманда Переход возвращает в регистр 3 адреса микрокоманды значение адреса первой -кткрокоманды описанной последовательности, т.е. микрокоманда Настройка. Стековая. Далее восполняется еще один проход по описанной последовательности, но при значении в регистре.58 узла 48 настройки стека операндов, равном 8 (остаток от прежнего значения длины поля операндов - 32, после его модификации на 24. После второго возврата на первую микрокоманду Настройка. Стековая обработка операндов уже закончена, и по этой микрокоманде в регистре 58 узла 48 настройки стека операндов будет установлено нулевое, значение, что приведёт к выполнению микрокоманды Переход, следующей за данной микрокомандой.

По микрокоманде Переход в регистре 3 адреса микрокоманды установ лен адрес микрокоманд .Обмен.Стековый , следукяцей за описанной последовательностью микрокоманд. Эта микрокоманда восстановит дескриптор результата в регистре 61 узла 45 поля стековых данных, причем содержимое секции длины поля этого регистра равно 1.

По микрокоманде Очистка.Регистровая произойдет очистка содержимого

регистров 7 левого и 8 правого операнда, и поэ-гому по следуквдей микрокоманде Пересыпка.Регистровая во второй регистр 11 общего назначения занесется только значение переноса, полученного в результате полного суммирования значений обоих операндов.

Микрокоманда Настройка. Стековая установит в регистре 58 узла 48 настройки стека операндов значение длины поля стековых данных из регистра 61 узла 45 поля стековых данных, т.е 1, и по микрокоманде Отсчет.Стековый произойдет смещение на эту длину содержимого секции начального-адреса в стековрй позиции в регистре 61 узла 45 поля стековых данных. Измененное значение этой секции равно 39.

По микрокоманде Запись.Стековая произойдет занесение значения переноса из второго регистра 11 общего назначения на поле результата в стек операндов. .

Как видно из примера, основу обработки полей переменной длины в стековой памяти составляют микроком§нда Отсчет.Стековый, Настройка. Стековая, Чтение.Стековое, Запись. Стековая. ,Использование этих кшкрокоманд позволяет построить циклическую обработку длинных последовательностей элементов данных без ЯВНОГО указания длины обработки на к 1ждом шаге ее выполнения.

того, использование варианта О в микрокоманде Настройка. Стековгл позволяет задать последовательную обработку элементов данных, т.е. по 1 разряду, по 1 цифрег (4 разряда), по 1 символу (8 разрядов, в зависимости от значения в секции типа данных блока 14 типа и длины поля| данных. Так, при необходимости выпсжнения посимвольной обработки операнда длиной в 40 Разрядов (значение в секции длины поля регистра 61 узла 45 стековых данных равио 40) пр значении 8 в секции типа данных блока 14 типа и длины поля данных предшествующая установка регистра 58 узл 48 настройки стека операндов по значению этой секции (вариант о; заносит в регистр 58 узла 48 настройки

стека значение 8. После этого указание варианта 5 в микрокоманде Настройка. Стековая приводит к выборке по 8 разрядов до тех пор, пока не будет исчерпано значение в секции длины поля регистра 61 узла 45 поля стековых данных.

оценки эффективности изобретения введены следующие обозначения и допущения:

соотношение между быстро

К действием основной и ста-: ковой пгиляти процессора К- 5-10;

-время заполнения стековой

Зет памяти процессора, tvp

-время обработки данных стековоЯ памяти на оборудовании процессора;

-соотнсииение между ТОВР и

(-Ж- 2-5Ь

-время, которое необходимо

m было бы потратить на обращение 3 основную память в ходе безадресной обработки данных при программной ре изации стековой памяти в основной памяти процессора ч Т д., где ;

-время,- которое необходимо

оп потратить на обращение в стековую память в ходе безадресной обработки данных при аппаратной реализации стековой памяти

Т S V

(

Чл- к )

с - доля линейных участков с

арифметической.или логической обработкой и выборкой данных из стека операндов в общем балансе программ работы интерпретатора ЯВУ ; или машинно-ориентированного языка с безёщресной обработкой данных (,5. С учетом этого введение стекоБой памяти в структуру процессора микропрограммируемой ЭВМ позволяет -повысить производительность процессора

(Tj)jE.+Ton).-iT2gp +T5aa ±Tra.

на Р

Т ОВР

+ Т

on

и

JlT ail-lTiqn.liiTM.r , ,,K-- llKlI. с X

tvi-T an ,о,„ К. К100%.

Так, при ,, hs3 величина , а при , , h 3 величина .

Формула изобретения

длины ПОЛЯ стека операндов и узла модификации, первый и второй управлякадие входы распределителя импульсов являются первым и вторым управляющими входами блока, первый выход данны узла настройки стека операндов соединен с первым выходом данных блока, второй выход данных узла настройки стека операндов и второй выход данных узла поля стековых данных соединены с первым выходом данных блока, первый вход данных блока соединен с первыми входами данных узла настройки стека операндов, узла поля стековых данных и узла модификации, третий вход данных блока соединен с первым входом данных узла установки текущей длины поля стека операндов,, второй выход данных узла настройки стека операндов соединен со вторыми входами данных узла модификации и узла установки текущей длины поля стека операндов, третий вход данных которого и третий вход данных узла модификации соединены с третьим выходом данных узла /юля стековых данных, первый выход данных которого соединен с четвертым входом данных узл модификации, первый, второй выходы .данных которого соединены соответственно со вторым и третьим вxoдa вн данных узла поля стековых данных, управляющий выход и второй вход данных узла настройки стека операндов соединены соответственно с шестым управляющим выходом блока и- с первым выходом данных узла установки текущей длины поля стека операндов, управляющий выход и четвертый, пятый вход данных которого являются соответствено седьмым управляющим выходом блока и вторым, четвертым входами данных блока..

Источники информации, принятые во внимание при экспертизе

№ 1.436.792., кл. G 06 F 3/06, опублик. 1976.

3 i Патент Великобритании 1.390.384, кл. G об F 7/38, опубт ЛИК.1975.

4,Королев Л.Н. Структуры ЭВМ и их математическое обеспечение. М., Энергия, с.163.

1066941, p.1-18 (прототип), .

Т Т

fJ

I

I 3

Фаг. W

ill

HZjj

/T

c

Фиг. fjT

H

Фиг. 17

аг./ff

Фиг. f9

0г/г 2ff

Фиг. 21

фиг 22

(. 23

Авторы

Даты

1981-08-30—Публикация

1979-12-14—Подача