Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровых вычислительных машин.

Известны "Устройство для аппаратурной трансляции" [1], "Устройство управления цифровой вычислительной машины" [2], как и другие [3], направленные на схемное обеспечение использования в вычислительной системе языка программирования высокого уровня за счет электронного преобразования программы, написанной на этом языке, в рабочие программы, представленные в кодах внутреннего машинного языка, и/или более или менее непосредственного выполнения кода, близкого по структуре к языку высокого уровня.

К недостаткам известных устройств относится то, что они значительно усложняют вычислительную систему. При этом, в известных устройствах со структурно реализованным языком программирования, этот язык выбирается единственным образом, и такие устройства не могут считаться в полной мере универсальными, поскольку не обеспечивают равноценности качества исполнения программ, записанных на различных языках, а существующие языки часто содержат особенности, которые могут трактоваться как произвольные или ограничительные и создавать препятствия для схемной реализации. Окончательным же исполнительным элементом в известных устройствах всегда выступает обычный процессор или командный блок, так что сохраняется этап интерпретации операторов языка командными программами, как и при использовании чисто программных методов.

Наиболее близким по технической сущности к предлагаемому изобретению "Формульный процессор с расширенным словом состояния" является процессор, содержащий арифметико-логическое устройство, устройство управления, регистры и блоки регистров различного назначения, работающий под управлением программы, хранящейся в оперативном запоминающем устройстве [4]. Однако, использование обычного ("командного") процессора [4, 5] представляет определенные трудности. Недостатком прототипа предлагаемого изобретения является то, что системы команд, которыми управляется процессор, требуют разложения алгоритма на элементарные операции, реализуемые отдельными, изолированными в исполнении командами. Командное представление алгоритма заставляет подробно описывать последовательность изменения содержимого оперативной памяти и организовывать сложные структуры для сохранения в конечном счете ненужных, но необходимых в процессе реализации алгоритма промежуточных результатов элементарных вычислительных операций. Обычным путем преодоления этих трудностей является использование программ-трансляторов, интерпретаторов или иных программных средств, автоматизирующих построение исполняемого кода. Но наличие программы-посредника сопряжено с затратами вычислительных ресурсов и создает заметный барьер между машиной и управляющим ей человеком, тем более значительный, что командный машинный код является трудно воспринимаемым объектом, в связи с чем фактическое содержание памяти компьютера, как правило, остается "непрозрачным".

Задача изобретения - повышение эффективности человеко-машинного взаимодействия. Поставленная задача решается посредством изменения систем трансляции или интерпретации внешних входных языков программирования на основе приближения внутреннего языка (системы командных кодов процессора) к языку программирования высокого уровня, что обеспечивает высвобождение ресурсов для повышения оснащенности и интеллектуальности интерпретирующих, транслирующих и иных программных систем [6], а также упрощает контроль исполняемого кода. В предлагаемом изобретении указанные изменения основаны на реорганизации схемы центрального процессора под управление системой команд или командоподобных кодов, замещающей либо дополняющей обычную систему команд и обеспечивающей формульное внутреннее представление программы или ее частей. Изменение схемы центрального процессора направлено на обеспечение большей, чем между командами известных процессоров, зависимости между элементами исполняемого кода, соответствующей связям между элементами формульного выражения. В результате установления этой зависимости целостным элементом программы может являться не только отдельная команда, как в обычных процессорах, но и целая совокупность кодов, адекватная вычислительной формуле, причем допустимая сложность строения этой формулы ограничена лишь ресурсами оперативной памяти.

Сущность заявленного изобретения заключается в обеспечении вышеуказанной зависимости посредством схемного обуславливания процесса выполнения команд формульной программы состоянием загрузки регистров местной (внутрипроцессорной) памяти. Для этого в известное слово состояния программы (ССП) дополнительно введены сопоставленные тем или иным регистрам местной памяти разряды (флаги загрузки), состояние которых отвечает декларируемому состоянию загрузки этих регистров, т.е. показывает, может ли данный регистр быть использован для сохранения текущих данных или он уже занят той или иной информацией. Подобно тому, как известные флаги ССП влияют на выполнение команд и устанавливаются в зависимости от результатов этого выполнения, флаги загрузки имеют адекватное участие в процессе управления местной памятью. Это участие включает автоматическую переустановку этих флагов как результат отработки очередной псевдокоманды, что подготавливает условия выполнения следующей (здесь и далее под псевдокомандой мы понимаем команду, выполнение которой существенно зависит от состояния флагов загрузки и/или переустанавливает эти флаги). Включение флагов загрузки в качестве дополнительных условий в выполнение псевдокоманд позволяет поставить отработку очередного символа формульной программы в зависимость от предшествующей части программы, выполнение которой создало данное состояние загрузки регистров. Это обеспечивает автоматический процесс сохранения откладываемых операций в местной и стековой памяти и адекватную последовательность выполнения операций с данными, которые могут быть как непосредственно представлены псевдокомандами формульной программы, так и являться результатами предыдущих вычислений. Функционирование расширенного слова состояния обеспечивается органическим составом системы регистров местной памяти и схемой выработки устройством управления управляющих сигналов.

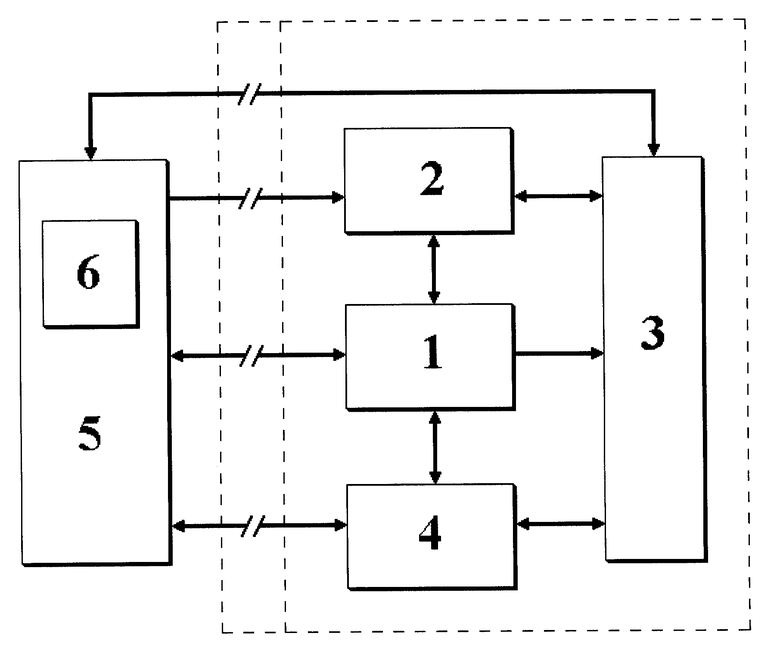

На чертеже представлена блок-схема предлагаемого изобретения "Формульный процессор с расширенным словом состояния". Устройство содержит арифметико-логическое устройство 1 (АЛУ), блок местной (регистровой) памяти 2 (МП), устройство управления 3 (УУ), блок управляющих регистров 4 (БУР).

Регистр (регистры) слова состояния программы (РСП) или регистр флагов содержится в БУР 4, который также включает регистр адреса очередной команды (счетчик команд - СК) и регистр (регистры), обслуживающие стек.

Подсоединение процессора к оперативному запоминающему устройству 5 (ОЗУ) может быть организовано через различные промежуточные устройства (общая шина, устройство управления памятью и т.п.) и обеспечивает работу процессора под управлением хранящейся в ОЗУ 5 программы.

Стековая область 6 (СО) может составлять часть ОЗУ 5, как показано на чертеже, либо представлять собой вид встроенной внутрипроцессорной памяти достаточной емкости с малым временем выборки.

Предлагаемый процессор функционирует следующим образом. Отработка формульной программы осуществляется на основе собирания в МП 2 и СО 6 кодов операций и операндов, представляемых различными псевдокомандами этой программы. Соответствующие вычисления реализуются, как только выполняются условия наличия в МП 2 одновременно всех необходимых кодов и операндов и приоритетное соответствие выполняемой и последующей операций. Обеспечивающие этот процесс действия производятся в цикле отработки очередной псевдокоманды адекватно логике вычисления формулы и складываются из различного набора и последовательности операций сохранения формульного символа, представленного отрабатываемой псевдокомандой, в подходящем регистре МП 2, освобождения регистров МП 2, занятых отработанными операндами и кодами операций, либо такими, которые не могут в настоящий момент составить вычислительное действие в силу приоритета очередной операции, сохранения в определенным образом организуемой записи в СО 6 операндов и кодов откладываемых операций, очередного восстановления регистров из снимаемой с верхушки стека записи, а также выдачи управляющих сигналов, инициирующих выполнение операции, код и операнды которой одновременно находятся в соответствующих регистрах МП 2. Все перечисленные действия с содержимым регистров МП 2 сопровождаются адекватным изменением декларируемого состояния их загрузки, отмечаемым переустановкой соответствующих флагов в регистре РСП.

УУ 3 обеспечивает выработку распределенных в пространстве и во времени сигналов, управляющих информационными и вычислительными процессами. Подсоединение УУ 3 к блокам процессора и ОЗУ 5 обеспечивает это управление. АЛУ 1 обеспечивает выполнение арифметико-логических операций. Подсоединение АЛУ 1 к блокам МП 2, БУР 4 и ОЗУ 5 обеспечивает обмен данными и другими необходимыми информационными сигналами между АЛУ 1 и этими блоками. Подсоединения блоков МП 2 и БУР 4 к ОЗУ 5 обеспечивают обмен данными между регистрами и ОЗУ 5.

Код каждой отдельно выполняемой арифметической или логической операции и ее операнды, как правило, не содержатся вместе в одной общей псевдокоманде, а собираются в процессе выполнения программы в регистрах МП 2 из нескольких отдельных псевдокоманд и, возможно, результата выполнения предыдущей части программы. Последовательность расположения псевдокоманд в оперативной памяти соответствует порядку отвечающих им символов в формульном представлении вычислительного алгоритма. Соединение кода операции и ее операндов обеспечивается генерацией УУ 3 управляющих сигналов в соответствии с кодом очередной отрабатываемой псевдокоманды и состоянием флагов декларируемой загрузки регистров МП 2 в слове состояния программы ССП, находящемся в регистре (регистрах) РСП, а также специальным составом и подключениями регистров местной памяти. Для этого МП 2 содержит соответствующие регистры для хранения кодов операций и операндов. Подключения этих регистров обеспечивают для УУ 3 возможность организовать выполнение соответствующих этим кодам вычислительных действий. Блок управляющих регистров 4 включает регистр слова состояния программы (РСП), а также регистр, содержащий адресную ссылку на текущий элемент выполняемой программы (счетчик команд СК), и регистр или регистры, обеспечивающие использование стека. В процессор могут входить и иные схемы, поддерживающие, например, систему прерываний, адресацию расширенной памяти, обмен с внешними устройствами и т.п.

Предлагаемое изобретение "Формульный процессор с расширенным словом состояния" обеспечивает прямое выполнение формульных структур, описываемых псевдокомандами внутреннего программного кода, последовательность которых адекватна символьному представлению теми или иными вычислительными формулами результатов выполнения этих структур.

ЛИТЕРАТУРА

1. Авторское свидетельство СССР N 1144108.

2. Авторское свидетельство СССР N 209040.

3. Э.Органик. Организация системы ИНТЕЛ 432 М.: Мир, 1987, 446 с.

4. В.А.Семененко, Ю.В. Ступин. Справочник по электронной вычислительной технике. М.: Машиностроение, 1993, 224 с.

5. Компьютеры. Справочное руководство в трех томах. Под ред. Г.Хелмса. М.: Мир, 1986, T.1, 416 с.; Т.3, 403 с.

6. Вычислительные машины с развитыми системами интерпретации. Под ред. В.М.Глушкова. Киев, Наукова Думка, 1970. 259 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С КОМАНДОПОДОБНЫМИ ЛОГИЧЕСКИМИ УПРАВЛЯЮЩИМИ ЭЛЕМЕНТАМИ | 1997 |

|

RU2143726C1 |

| ОТОБРАЖЕНИЕ С ПОМОЩЬЮ МУЛЬТИНАБОРОВ КОМАНД | 1995 |

|

RU2137184C1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| УСТРОЙСТВО И СПОСОБ ОБРАБОТКИ ДАННЫХ С ИСПОЛЬЗОВАНИЕМ НАБОРОВ КОМАНД | 1995 |

|

RU2137183C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| МОДУЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С РАЗДЕЛЬНЫМ МИКРОПРОГРАММНЫМ УПРАВЛЕНИЕМ АРИФМЕТИКО-ЛОГИЧЕСКИМИ СЕКЦИЯМИ И ЧЕРЕДУЮЩИМСЯ ОБСЛУЖИВАНИЕМ НЕСКОЛЬКИХ КОМАНДНЫХ ПОТОКОВ | 1995 |

|

RU2099780C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С ЧЕРЕДУЮЩИМСЯ ОБСЛУЖИВАНИЕМ НЕСКОЛЬКИХ КОМАНДНЫХ ПОТОКОВ | 1995 |

|

RU2101759C1 |

| ОПРЕДЕЛЕНИЕ ДЛИНЫ ГРУППЫ СИМВОЛЬНЫХ ДАННЫХ, СОДЕРЖАЩЕЙ СИМВОЛ ОКОНЧАНИЯ | 2013 |

|

RU2621000C2 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровых вычислительных машин. Техническим результатом является повышение эффективности человеко-машинного взаимодействия за счет изменения систем трансляции или интерпретации внешних входных языков. Для этого в заявленном устройстве регистр слова состояния программы дополнительно включает флаги декларируемого состояния загрузки регистров блока местной памяти, а блок местной памяти включает в себя регистры, соответствующие этим флагам. 1 ил.

Формульный процессор с расширенным словом состояния, содержащий устройство управления, арифметико-логическое устройство, блок местной (регистровой) памяти, блок управляющих регистров, который содержит регистр слова состояния программы, причем устройство управления связано с арифметико-логическим устройством, блоком управляющих регистров, блоком местной памяти и оперативным запоминающим устройством, арифметико-логическое устройство связано с блоком местной памяти, блоком управляющих регистров и оперативным запоминающим устройством, которое связано с блоком местной памяти и блоком управляющих регистров, отличающийся тем, что регистр слова состояния программы дополнительно включает флаги декларируемого состояния загрузки регистров блока местной памяти, а блок местной памяти включает в себя регистры, соответствующие упомянутым флагам и выполненные с возможностью содержания в разных фазах функционирования упомянутого процессора кодов выполняемых операций и их операндов.

| СЕМЕНЕНКО В.А | |||

| и др | |||

| Справочник по электронной вычислительной технике | |||

| - М.: Машиностроение, 1993, с.58-63 | |||

| УСТРОЙСТВО УПРАВЛЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙМАШИНЫ | 0 |

|

SU209040A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Компьютеры | |||

| Справочное руководство в трех томах./Под ред | |||

| Хелмса Г | |||

| - М.: Мир, 1986, т.1, с | |||

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| Процессор | 1976 |

|

SU602949A1 |

| DE 3202757 A1, 04.08.1983 | |||

| US 4084233 A, 11.04.1978 | |||

| US 4562538 A, 31.12.1985 | |||

| US 4554629 A, 19.11.1985 | |||

| Процессор микропрограмируемой ЭВМ | 1989 |

|

SU1697082A1 |

Авторы

Даты

2000-05-20—Публикация

1999-02-17—Подача