Известны анализаторы с переменной шириной канала, имеющие запоминающее устройство параллельного типа на ферритовых сердечниках.

Описываемый многоканальный, временной анализатор позволяет получить регулируемую ширину временного канала при значительном упрощении аппаратуры. Достигается это тем, что выход усилителя записи основного запоминающего устройства соединен со входом ключа стирания информации через последовательно включенные первую схему совпадения, подсоединенную своим вторым входом к генератору канальных импульсов, линию задержки, триггер управления и вторую схему совпадения, второй вход которой соединен с выходом первой схемы совпадения. Ко второму входу триггера управления подключено таймерное устройство, задающее ширину временного канала, а выход второй схемы совпадения соединен с устройством записи через дополнительную линию задержки.

Кроме того, с целью повышения помехоустойчивости, линия задержки на выходе первой схемы совпадения соединена с ее третьим входом через дополнительный управляющий триггер, ко второму входу которого подключена схема выделения стартового импульса основного запоминающего устройства.

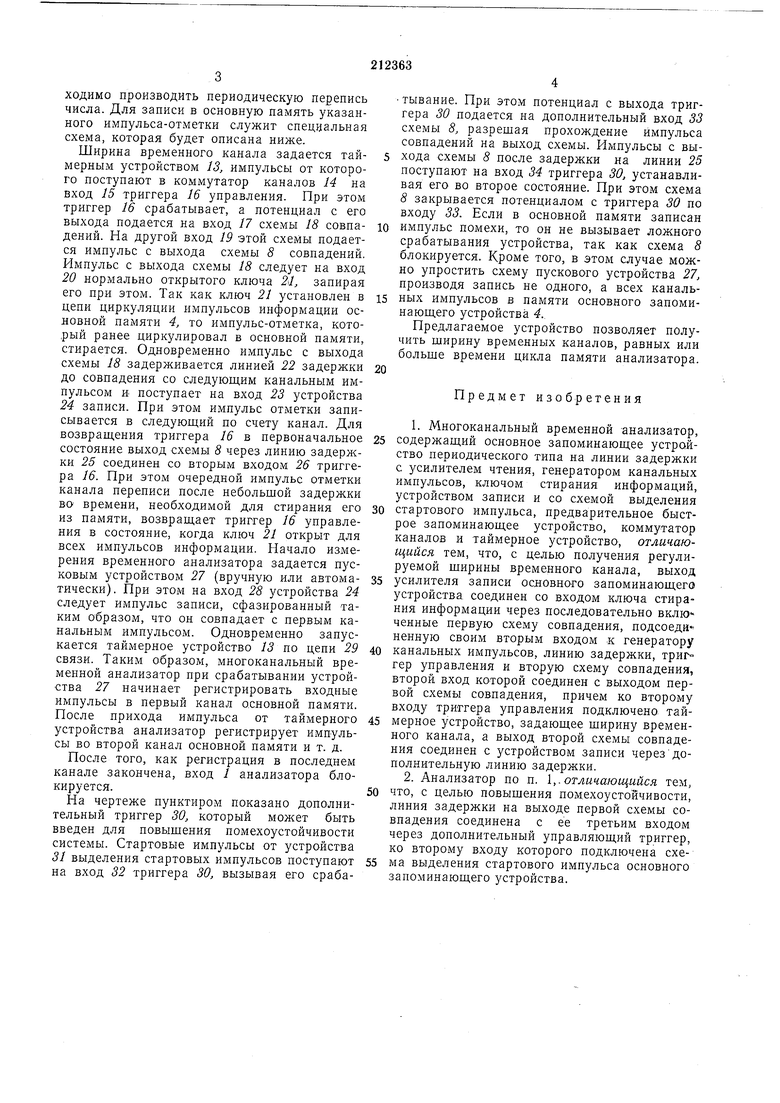

На чертеже представлена схема описываемого многоканального временного анализатора.

Импульсы от измерительного объекта поступают на вход / анализатора и запоминаются в виде цифрового кода в памяти предварительного запоминающего устройства 2. Перепись данных производится по цепи 3 связи в основное запоминающее устройство

с памятью на линии 5 задержки следующим образом. Импульсы информации, циркулирующей в памяти основного запоминающего устройства, с выхода усилителя 6 чтения следуют на вход 7 схемы 8 совпадений. На другой вход 9 этой схемы поданы канальные импульсы от генератора 10 канальных импульсов. Выделенный импульс совпадений по цепи 11 связи дает команду переписи данных из предварительного запоминающего устройства 2 в основное запоминающее устройство 4. При этом кодовые импульсы числа по цепи 3 следуют на вход последовательного арифметического устройства 12. Такое совпадение импульсов и перепись числа происходит

во время каждого цикла памяти. Для правильной работы схемы необходимо, чтобы в основной памяти циркулировал импульс, который каждый раз совпадал бы с одним из канальных импульсов. Этот импульс может 3 ходимо производить периодическую перепись чнсла. Для записи в основную память указанкого импульса-отметки служит специальная схема, которая будет описана ниже. Ширина временного канала задается тай-5 мерным устройством 13, импульсы от которого поступают в коммутатор каналов 14 на вход 15 триггера 16 управления. При этом триггер 16 срабатывает, а потенциал с его выхода подается на вход 17 схемы 18 совпа-ю дений. На другой вход 19 этой схемы подается импульс с выхода схемы 8 совпадений. Импульс с выхода схемы 18 следует на вход 20 нормально открытого ключа , запирая его при этом. Так как ключ 21 установлен вis цепи циркуляции импульсов информации основной памяти 4, то импульс-отметка, который ранее циркулировал в основной памяти, стирается. Одновременно импульс с выхода схемы 18 задерживается линией 22 задержки20 до совпадения со следующим канальным импульсом и поступает на вход 23 устройства 24 записи. При этом импульс отметки записывается в следующий по счету канал. Для возвраш,ения триггера 16 в первоначальное25 состояние выход схемы 8 через линию задержки 25 соединен со вторым входом 26 триггера 16. При этом очередной импульс отметки канала переписи после небольшой задержки во времени, необходимой для стирания егозо из памяти, возвращает триггер 16 управления в состояние, когда ключ 21 открыт для всех импульсов информации. Пачало измерения временного анализатора задается п)сковым устройством 27 (вручную или автома-35 тически). При этом на вход 28 устройства 24 следует импульс записи, сфазированный таКИМ образом, что он совпадает с первым канальным импульсом. Одновременно запускается таймерное устройство 13 по цепи 2940 связи. Таким образом, многоканальный временной анализатор при срабатывании устройства 27 начинает регистрировать входные импульсы в первый канал основной памяти. После прихода импульса от таймерного45 устройства анализатор регистрирует импульсы во второй канал основной памяти и т. д. После того, как регистрация в последнем канале закончена, вход 1 анализатора блокируется.50 На чертеже пунктиром показано дополнительный триггер 30, который может быть введен для повышения помехоустойчивости системы. Стартовые импульсы от устройства 31 выделения стартовых импульсов поступают55 на вход 32 триггера 30, вызывая его сраба4тывание. При этом потепциал с выхода триггера 30 подается на дополнительный вход 33 схемы 8, разрешая прохождение импульса совпадений на выход схемы. Импульсы с выхода схемы 8 после задержки на линии 25 поступают на вход 34 триггера 30, устанавливая его во второе состояние. При этом схема 8 закрывается потенциалом с триггера 30 по входу 33. Если в основной памяти записан импульс помехи, то он не вызывает ложного срабатывания устройства, так как схема 8 блокируется. Кроме того, в этом случае можно упростить схему пускового устройства 27, производя запись не одного, а всех канальных импульсов в памяти основного запоминающего устройства 4. Предлагаемое устройство позволяет получить ширину временных каналов, равных или больше времени цикла памяти анализатора, Предмет изобретения 1. Многоканальный временной анализатор, содержащий основное запоминающее устрайство периодического типа на линии задержки с усилителем чтения, генератором канальных импульсов, ключом стирания информации, устройством записи и со схемой выделения стартового импульса, предварительное быстрое запоминающее устройство, коммутатор каналов и таймерное устройство , отличающийся тем, что, с целью получения регулируемой ширины временного канала, выход усилителя записи основного запоминающего устройства соединен со входом ключа стирания информации через последовательно включенные первую схему совпадения, подсоеди пенную своим вторым входом к генератору канальных импульсов, линию задержки, триггер управления и вторую схему совпадения, второй вход которой соединен с выходом первой схемы совпадения, причем ко второму входу триггера управления подключено таймерное устройство, задающее ширину временного канала, а выход второй схемы совпадения соединен с устройством записи черездополнительную линию задержки, 2. Анализатор по п. I,.отличающийся тем, что, с целью повышения пом,ехоустойчивости, линия задержки на выходе первой схемы совпадения соединена с ее третьим входом через дополнительный управляющий триггер, ко второму входу которого подключена схема выделения стартового импульса основного запоминающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛИЗАТОР ИМПУЛЬСОВ | 1972 |

|

SU330455A1 |

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1968 |

|

SU211156A1 |

| Многоканальное устройство для передачи и приема дискретной информации | 1987 |

|

SU1517141A2 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1979 |

|

SU1840444A1 |

| ЦИФРОВОЙ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU297071A1 |

| Многоканальное устройство для передачи дискретной информации | 1983 |

|

SU1159170A1 |

| СПЕКТРОМЕТРИЧЕСКИЙ СПОСОБ ИЗМЕРЕНИЯ ЯДЕРНЫХ ИЗЛУЧЕНИЙ И РЕАЛИЗУЮЩАЯ ЕГО СПЕКТРОМЕТРИЧЕСКАЯ СИСТЕМА | 2002 |

|

RU2269798C2 |

| УСТРОЙСТВО ДЛЯ ВРЕМЕННОГО СЖАТИЯ ВХОДНОГО СИГНАЛА | 1971 |

|

SU428544A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИГНАЛОВ В ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКЕ | 1983 |

|

RU2035097C1 |

| Многоканальный автономный прибор для исследования скважин в процессе бурения | 1981 |

|

SU983261A1 |

Даты

1968-01-01—Публикация