Изобретение относится к области технических средств, применяемых для исследования в ядерной физике.

Известны анализаторы импульсов, применяемые для многоканального накопления импульсов входной информации с детектора ионизирующего излучения в последовательных временных интервалах после начального момента, задаваемого стартовым импульсом, синхронным с запуском импульсного источнИКа излучения. Анализатор импульсов содержит запускаемый стартовым импульсом таймер, многоканальное запоминающее устройство с числовым и адресным регистром, ключ в цепи поступления импульсов с детектора на числовой регистр запоминающего устройства (ЗУ), а также устройство формирования импульсов для остановки таймера. Накопление имеющих статистическое распределение и поступающих с детектора импульсов информации в числовом регистре ЗУ производится в течение временного интервала между импульсами серии, вырабатываемой таймером на каждый стартовый запуск. По окончании каждого временного интервала таймерный импульс вызывает операцию переписи содержимого числового регистра в выбранный канал ЗУ анализатора и изменяет адрес ЗУ на следующий.

писи необходимо блокировать ключом поступление входной информации в числовой регистр ЗУ. Необходимость измерения в малых временных интервалах из-за конечного времени обращения к ЗУ приводит к значительным просчетам входной информация и искажению реально существующего во времени распределения импульсов на выходе детектора.

С целью исключения просчетов входных импульсов в течение времени переписи данных из числового регистра в многоканальное запоминающее устройство и повыщения его надежности в предлагаемом анализаторе вход таймера подключен к счетному входу коммутационного триггера, один выход которого соединен со входами управления ключа регистра числа ЗУ и ключа устройства управления дополнительного ЗУ, а второй выход коммутационного триггера соединен со входами управления ключа регистра числа дополнительного ЗУ и ключа устройства управления ЗУ, причем сигнальные входы ключей регистров числа обоих ЗУ соединены с источником импульсов входной информации, а сигнальные входы ключей устройства управления обоих ЗУ соединены через элемент задержки с выходом таймера, при этом вход остаиовки таймера соединен с выходом логического элемента «ИЛИ, входы которого

подключены к выходам переполнения адресных регистров обоих ЗУ.

Оба запоминающих устройства в анализаторе работают поочередно: одно в качестве ЗУ нечетных каналов, а второе - в качестве ЗУ четных каналов, при этом количество каналов каждого из ЗУ в предлагаемом анализаторе импульсов при одинаковых условиях измерения требуется в два раза меньше. Поскольку информация, накопленная в одном ЗУ анализатора, последовательно, поканально дополняет информацию в другом, выход из строя в процессе одного из ЗУ (как самого сложного, содержащего наибольшее количество оборудования и «ненадежного ycTpoficTва анализатора импульсов) не приводит к общему отказу анализатора. Надежность запоминающего устройства подобной дублированной системы при семичасовой работе анализатора с реальной расчетной интенсивностью отказов ЗУ я 440 10 1.шс должна повыситься примерло в тридцать раз.

Дублированная остановка таймера обеспечивается подачей на его вход импульсов переполнения адресных регистров обоих ЗУ через логический элемент «Р1ЛР1.

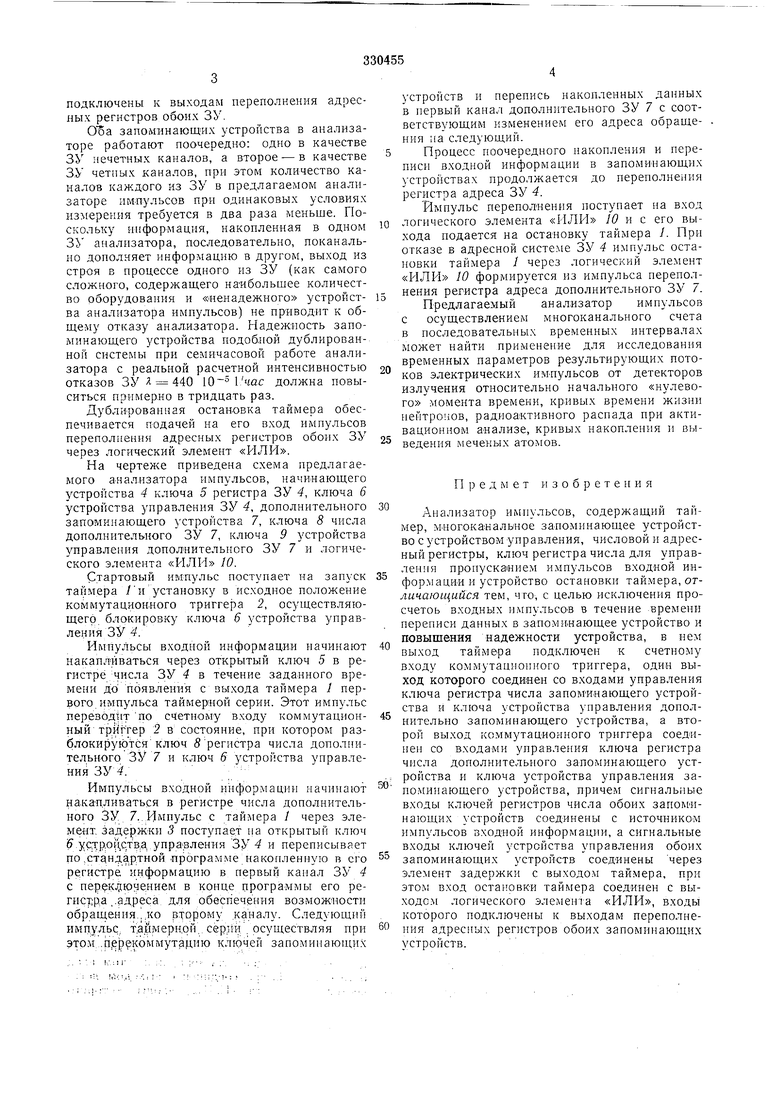

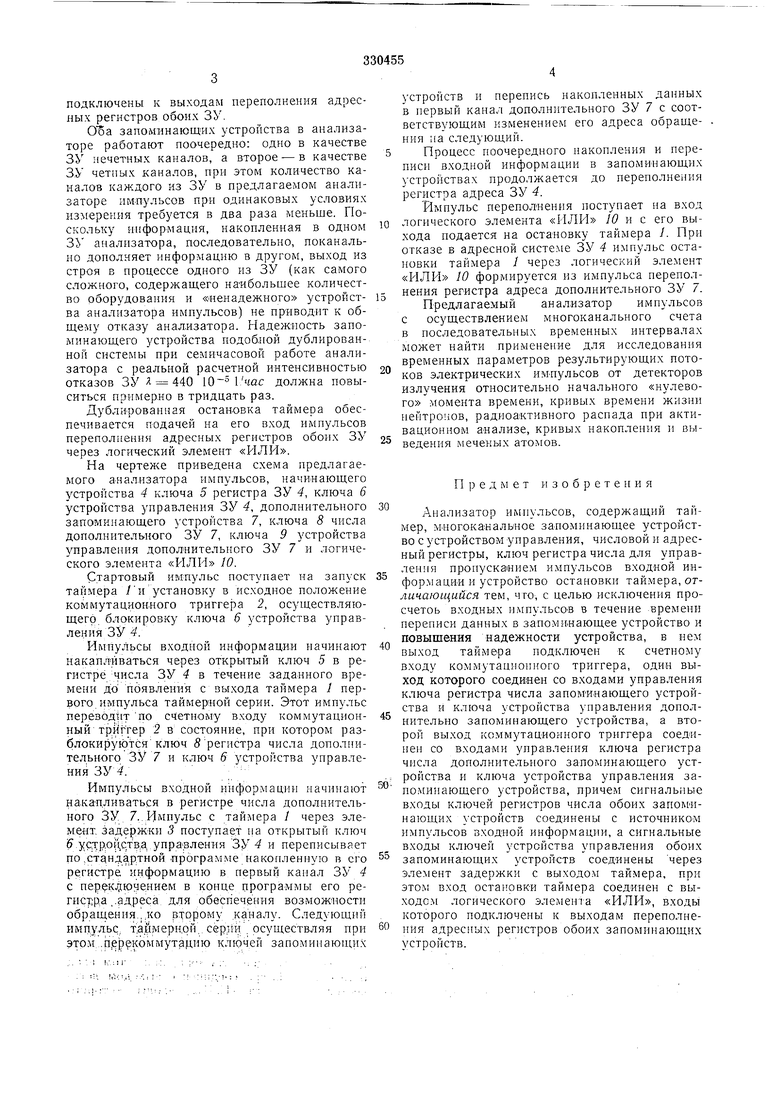

На чертеже приведена схема предлагаемого анализатора импульсов, начинающего устройства 4 ключа 5 регистра ЗУ 4, ключа 6 устройства управления ЗУ 4, дополнительного запоминающего устройства 7, ключа 8 числа дополнительного ЗУ 7, ключа 9 устройства управления дополнительного ЗУ 7 и логического элемента «ИЛИ 10.

Стартовый импульс поступает на запуск таймера /и установку в исходное положение коммутационного триггера 2, осуществляющего блокировку ключа 6 устройства управления ЗУ 4.

Импульсы входной информации начинают накапливаться через открытый ключ 5 в регистре числа ЗУ 4 в течение заданного времени до появления с выхода таймера / первого импульса таймер .ной серии. Этот импульс переводитпо счетному входу коммутационный триггер 2 в состояние, при котором разблокируются ключ Sрегистра числа дополнительного ЗУ 7 и ключ 6 устройства управления ЗУ.

Импульсы входной информации начинают накапливаться в регистре числа дополнительного ЗУ 7..Импульс с таймера / через элемент, задержки 5 поступает на открытый ключ 5,ХС,.ойствд упра-вления Зу 4 и переписывает по .стандартной программе накопленную в его регистре информацию в первый канал ЗУ 4 с переключением в конце программы его реFHCjipa ..адреса для обеспечения возможности обрац|,ения.,,ко второму каналу. Следующий импульс, т.аймерн.ой,. серди . осуществляя при этом .перркоммутацию ключей запоминающих

устройств и перепись накопленных данных Б первый канал дополнительного ЗУ 7 с соответствующим изменением его адреса обращения на следующий.

5 Процесс поочередного накопления и переписи входной информации в запоминающих устройствах продолжается до переполнения регистра адреса ЗУ 4.

Импульс переполнения поступает на вход 0 логического элемента «ИЛИ 10 и с его выхода подается на остановку таймера У. При отказе в адресной системе ЗУ 4 импульс остановки таймера / через логический элемент «Р1ЛИ 10 формируется из импульса переполнения регистра адреса дополнительного ЗУ 7.

Предлагаемый анализатор импульсов с осуществлением многоканального счета в последовательных временных интервалах может найти применение для исследования временных параметров результирующих потоков электрических импульсов от детекторов излучения относительно начального «нулевого момента времени, кривых времени жизни нейтронов, радиоактивного распада при активационном анализе, кривых накопления и выведения меченых атомов.

Предмет изобретения

Анализатор имиульсов, содержащий таймер, Многока«альное запомииающее устройство с устройством управления, числовой и адресный регистры, ключ регистра числа для управления пропусканием импульсов входной информации и устройство остановки таймера, огличающийся тем, что, с целью исключения просчетоь входных импульсов в течение времени переписи данных в запоминающее устройство и повышения надежности устройства, в нем выход таймера подключен к счетному входу коммутационного триггера, один выход которого соединен со входами управления ключа регистра числа запоминающего устройства и ключа устройства управления дополнительно запоминающего устройства, а второй выход коммутационного триггера соединен со входами управления ключа регистра числа дополнительного запоминающего уст. ройства и ключа устройства управления за иоминающего устройства, причем сигнальные входы ключей регистров числа обоих запоминающих устройств соединены с источником импульсов входной информации, а сигнальные входы ключей устройства управления обоих запоминающих устройств соединены через элемент задержки с выходом таймера, при этом вход остановки таймера соединен с выходом логического элемента «ИЛИ, входы которого подключены к выходам переполненИя адресных регистров оооих запоминающих устройств.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР | 1972 |

|

SU415676A1 |

| Анализатор амплитудных распре-дЕлЕНий | 1979 |

|

SU798868A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| Многоканальное устройство для регистрации сигналов | 1988 |

|

SU1543232A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249591A1 |

| Статистический анализатор условной функции распределения размахов колебаний напряжения | 1982 |

|

SU1092423A1 |

| Многоканальное устройство для регистрации сигналов | 1987 |

|

SU1439675A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛИЗАТОР | 1970 |

|

SU259153A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛИЗАТОР | 1972 |

|

SU424156A1 |

| Запоминающее устройство с коррекцией программы | 1986 |

|

SU1347097A1 |

Даты

1972-01-01—Публикация