МногокаНальныё счетчики ймпульсой йспользуются в качестве регистратора в аппаратуре, Предназначенной для измерения плотМости яотока ионизирующих излучений счетМым методом. Такие измерения часто проводятся В ядерной физике И при решении технических задач, связанных с использованием радиоактивных изотопов я ядерных излучений, особенно при гамма-дефектоскопии различных изделий методом просвечивания с непрерывным сканированием.

Известен многоканальный счетчик импульсов, содержащий предварительные пересчетные устройства с триггерами переполнения, блок памяти на ферритовых сердечниках с приводом, Коммутатор, регистр памяти, программный блок, блок вывода накопленной информации, логические схемы и таймерное устройство, включающее генератор импульсов, делитель частоты И узел «пуск - стоп с временным селектором.

Цикл работы этого счетчика состоит из одновременного накопления информации по всем каналам и поочередного вывода информации, накопленной в каналах, причем во время вывода информация не накапливается и часть ее теряется. В результате такой счетчик не может быть использован при контроле процессов, где требуется непрерывное накопление информации с одновременным ее выводом.

Предложенный многоканальный счетчик от-личается от известного тем, что он содержит в таймерном устройстве схему «НЕ-И и статический триггер, причем схема «НЕ-И

соединена по входу с временным селектором, а по выходу - с делителем частоты, управляющие входы статического триггера соединены с выходОМ делителя, выходом Временного селектора и узлом «пуск - стоп, а выход -

с управляющим входом схемы «НЕ-И привода блока памяти и через линию задержки с управляющим входом схемы «НЕ-И таймерного устройства и входом блока .выхода информации. Кроме того, счетчик содержит

узел блокировки команд, состоящий из счетчика импульсов, статического триггера блокировки и двух схем «НЕ-И блокировки команд «стирание информации и «вывод информации, причем счетчик импульсов соедииен по входу со схемой «НЕ-И таймерного устройства, по выходу со входом статического триггера блокировки, второй вход которого связан с управляющим входом статического триггера таймерного устройства, а выходы

подключены к схемам «НЕ-И блокирОВки команд, входы которых соединены со входом счетчика импульсов и с блоком вывода информации. Устройство обеспечивает непрерывное наформации в промежуток времени с мамента пуска до мо.мента достижения выбранного в-ремени набора.

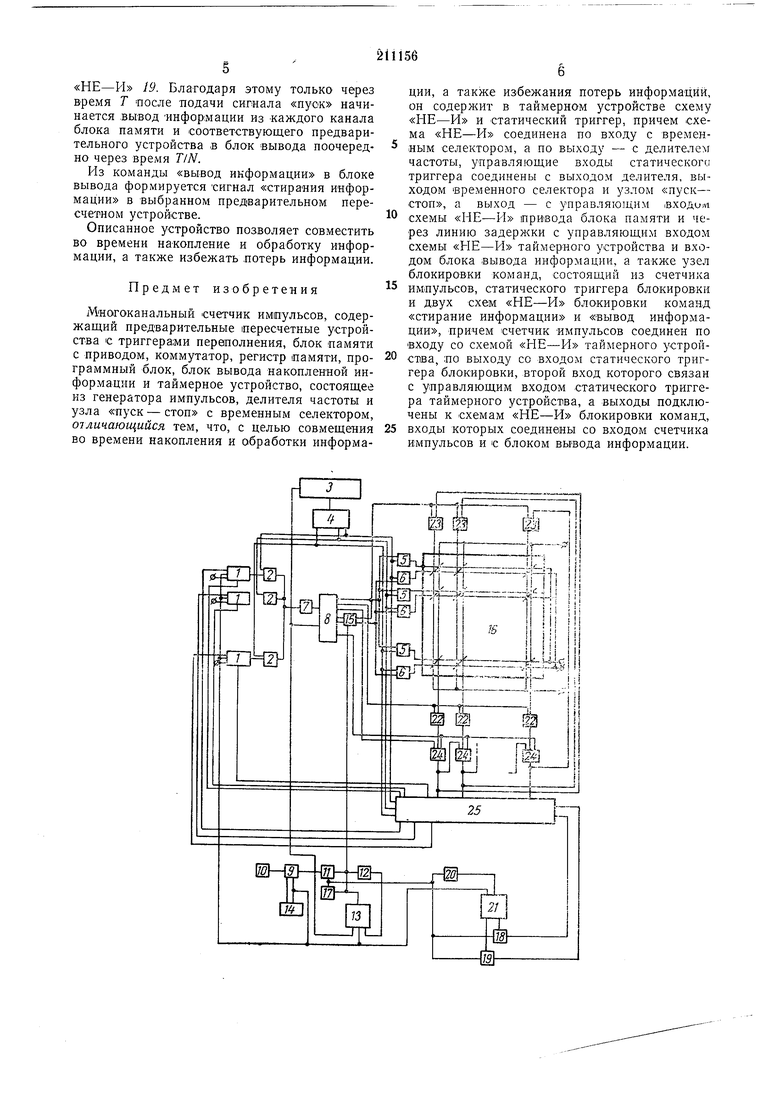

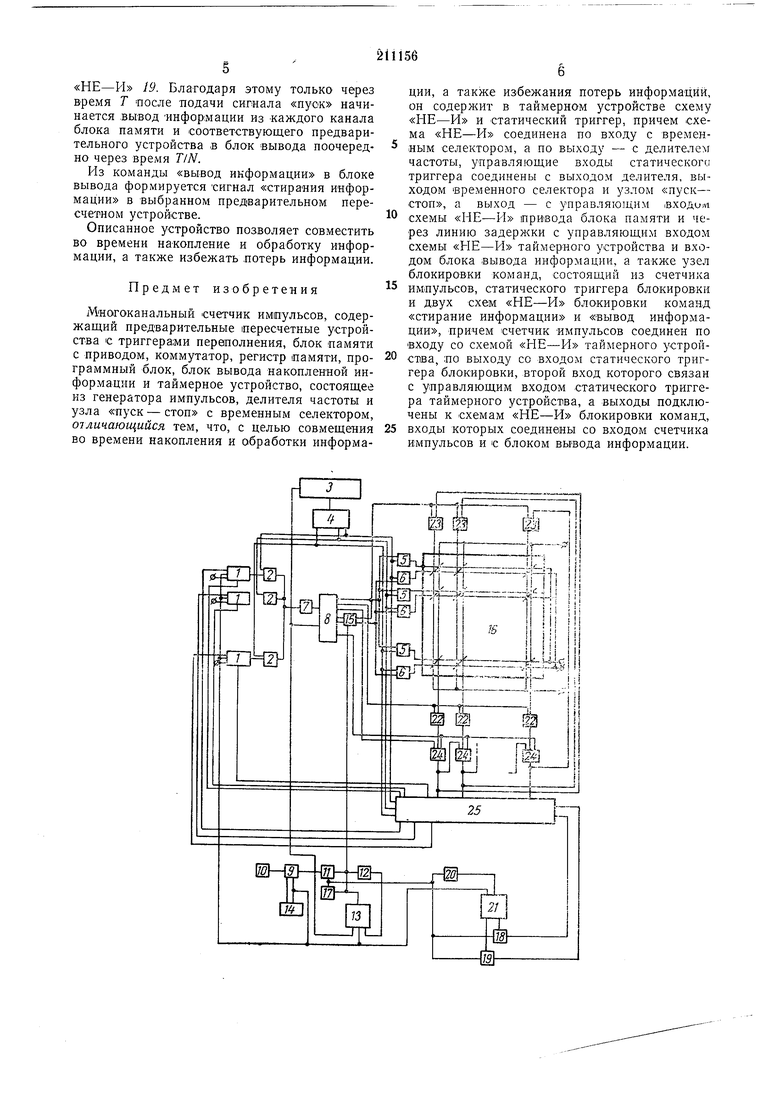

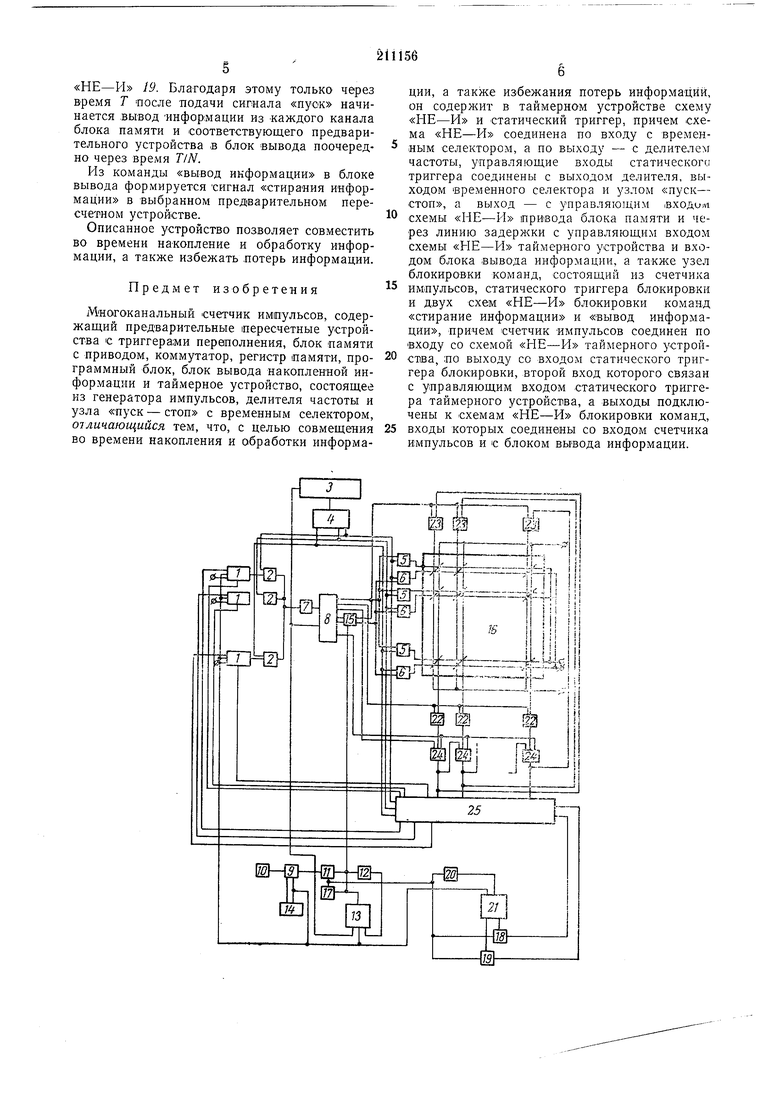

На чертеже дана блок-схема многоканального счетчика.

Он содержит -предварительные переочетные устройства 1, триггеры 2 оереполнения, регистр 3 адреса коммутатора, дешифратор 4 коммутатора, формирователи 5 тока считывания, формирователи 6 тока записи, схему «ИЛИ 7, программный блок 8, временной селектор 9, генератор 10 импульсов, схему «НЕ-И 11 таймериого устройства, делитель частоты 12, статический триггер 13, узел «пуск - стоп 14, схему «НЕ-И 15, блок памяти 16, Линию задержки 17, схемы «НЕ-И /5 и 19, счетчик 20 импульсов, статический триггер 21, усилители 22 чтения, генераторы 23 токов запрета, триггеры 24 регистра памяти, блок 25 вывода. Схема работает следующим образом. При подаче сигнала «пуск с узла «пуск - стоп 14 происходит разблокировка входа предварительных пересчегных устройств и начинается набор информации в ка«алы счетчика. Одновременно сигнал «пуск устанавливает триггеры 13 21 и состояние, поддерживающее схемы «НЕ-И 11, /5 и 18 закрытыми, а схему «НЕ-И 19 открытой, и открывает временной селектор 9, через который импульсы частотой f с генератора имлульсоз/О попадают на вход схемы «НЕ-И 11, на вход регистра адреса 3 коммутатора, в программный блок 5 и на вход установки «О триггера 13.

Коммутатор 3, 4 с приходом сигнала частотой / начинает поочередный опрос /V триггеров 2 переполнения, одновременно выбирая соответствующий формирователь 5 тока считывания и формирователь 6 тока записи. Частота генератора импульсов рассчитывается, исходя из требования, чтобы время переключения коммутатора было больше или

/1

равно времени обращения к блоку 16 памяти. За каждый промежуток времени 5 программный блок 8 выдает серию управляющих импульсов, следующих в определенной последовательности: импульс считывания, на который формирователь 5 тока считывания вырабатывает импульс тока считывания, достаточный для перемагничивания соответствующей строки ферритовой матрицы в нулевое состояние; импульс разблокировки усилителей 22 чтения; импульс добавления «1 )3 регистр па-мяти 24, возникающий при поступлении на вход программного блока 8 импульса с соответствующего триггера переполнения через схему «ИЛИ 7, импульс запрета, поступающий через схему «НЕ-И 15 и запускающий qгенераторов 23 тока запрета, сигнал блокировки на каждый из которых -подается с соответствующего триггера 24 регистра памяти, импульс записи на фор.мирователь тока записи, вырабатывающий импульс тока записи в выбранную строку матрицы, и импульс установки «О в регистре памяти.

Под действием импульсов считывания и разблокировки происходит считывание информации, накопленной в опрашиваемом канале матрицы, в регистр памяти.

Если триггер переполнения опращиваемого канала счетчика зафиксировал состояние переполнения предварительного пересчетного устройства, то под действием импульса добавленпя «1 к информации, выведенной в рэгистр памяти, добавляется единица. Нод действием импульсов запрета и записи осуществляется регенерация числа в опрашиваемый канал матрицы, после чего импульсом установки «О регистр памяти очищается.

С приходом очередного сигнала с генератора программа повторяется, но уже для следующего канала.

1

По истечении времени T/N, равного KN -,

/1

где К - целое число, сигнал с выхода делителя частоты 12 переводит триггер 13 в состояние, запрещающее схеме «НЕ-И 15 пропускать сигналы, служащие для регенерации числа в выбранном (первом) канале блока памяти. При этом происходит сброс информации, накопленной в опрашиваемом канале матрицы.

Длительность сигнала с выхода триггера 13 равна S, поскольку триггер 13 устанавливается в состояние «О каждым .входным импульсом с генератора 10. Сигнал, формируемый триггером 13, задержанный на время линией задержки 17 и поданный на входы схем «НЕ-И 18, 19, 11 и счетчика 20 используется в качестве команды вывода информации из канала счетчика, команды установки в состояние «О предварительных переечетны.ч

устройств, а также для управления схемой «НЕ-И 11. Импульсы с генератора 10, переводящие триггер 13 в состояние «О из состояния «1, на вход делителя частоты 12 не поступают, поскольку IB момент их прохождения на управляющем входе схемы «НЕ-И 11 присутствует запрещающий сигнал, подаваемый через линию задержки 17 с выхода триггера 13. Благодаря этому формирование триггером 13 перечисленных выще команд для

соседних каналов осуществляется с интервалом T/N, а для любого отдельного канала - с интервалом Т.

Открытая схема «НЕ-И 19 пропускает команду установки «О предварительного пересчетного устройства в блок вывода, где этот сигнал фор:мируется и подается в опращиваемое предварительное пересчетное устройство. Схема «НЕ-И 18, служащая для пропускания команды «вывод информации, остается

закрытой до тех пор, пока на счетчик 20 с коэффициентом пересчета N, управляющий триггером 21, не поступит Л импульсов с выхода линии задержки 17. Нри этом триггер 21 изменяет состояние на противоположное, от

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации (его варианты) | 1981 |

|

SU1092487A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| Логический анализатор | 1985 |

|

SU1283771A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1972 |

|

SU331383A1 |

| УСТРОЙСТВО ВВОДА И ХРАНЕНИЯ КЛЮЧЕВОЙ ИНФОРМАЦИИ | 2000 |

|

RU2175775C1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1987 |

|

SU1437870A2 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1986 |

|

SU1381523A2 |

Даты

1968-01-01—Публикация