1

Изобретение относится к области автоматики и Г5ычислителы ой техлики и предназначено для анализа сигналов в реальном масштабе времени, согласования полосы сигнала с нолосой пропускания анализирующей аппаратуры и так далее.

Известное устройство ио авт. св. № 253456 имеет пло.хую темиературиую стабильность.

Цель изобретения - новышение темнературной стабильности устройства.

Для этого в цеиь обратной связи каждой мaгf итocтpикциoннoй линии задержки дополнительно введеи одноразрядный буферный регистр, управляющие входы которого подключены к выходу дополнительно введенного распределителя импульсов, вход которого подключен к выходу генератора тактовых имнульсов.

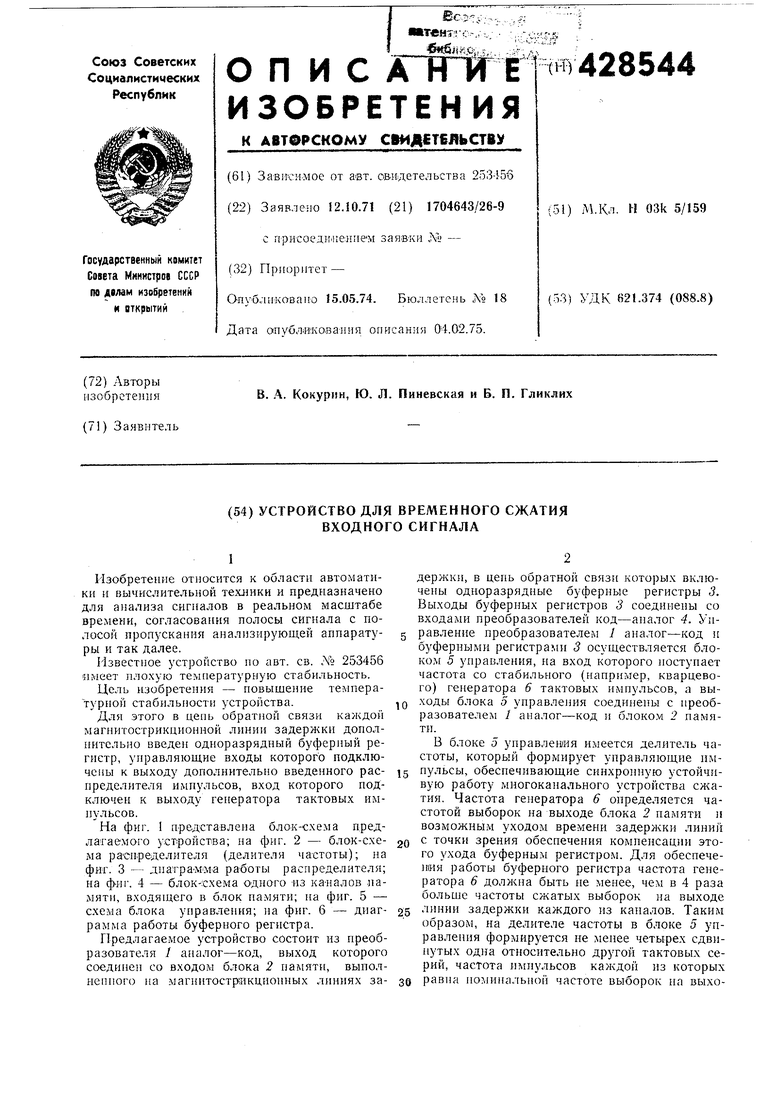

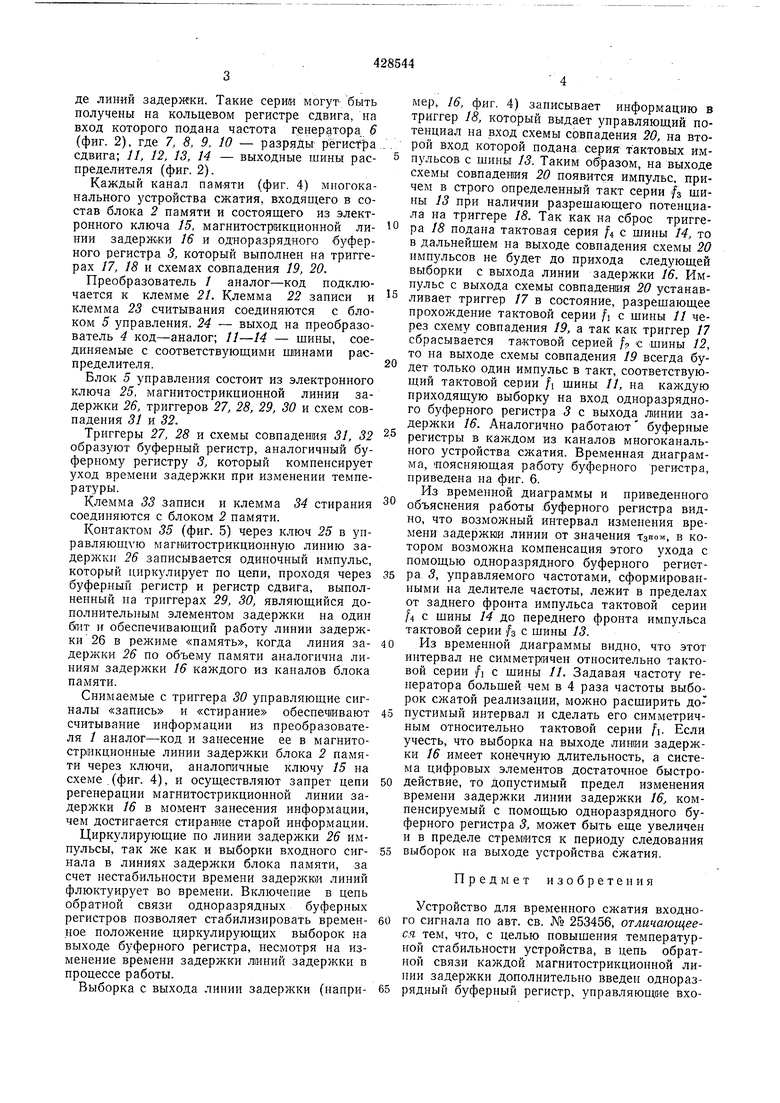

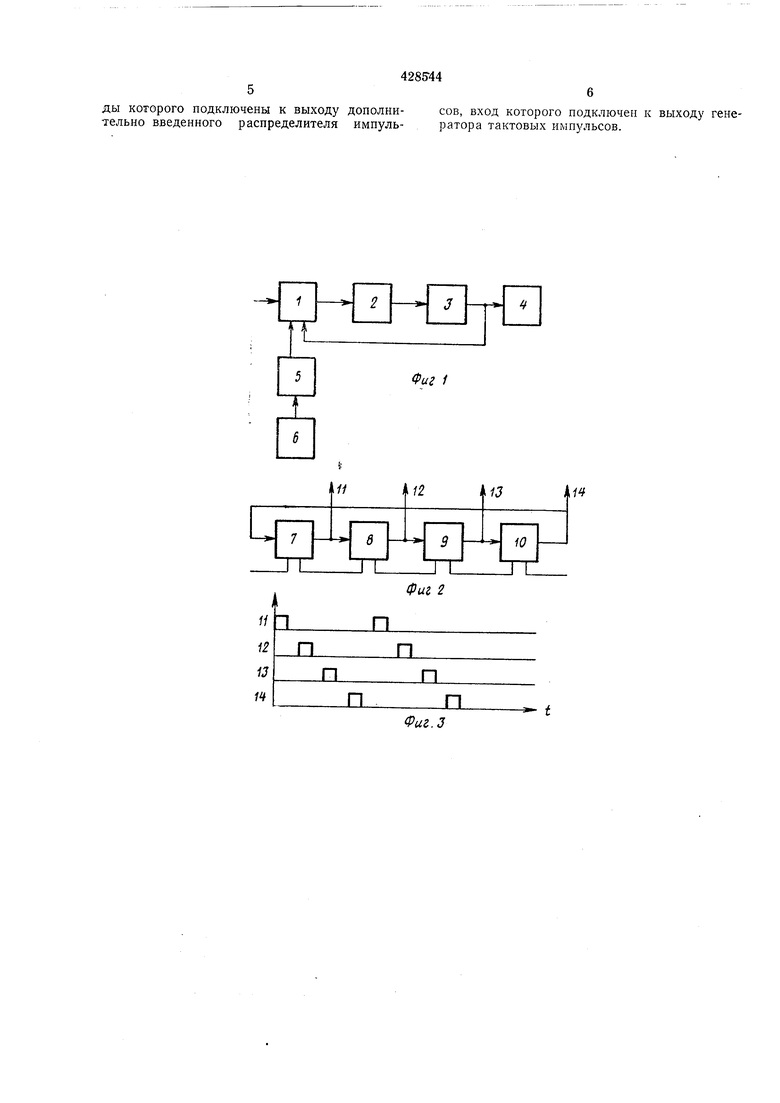

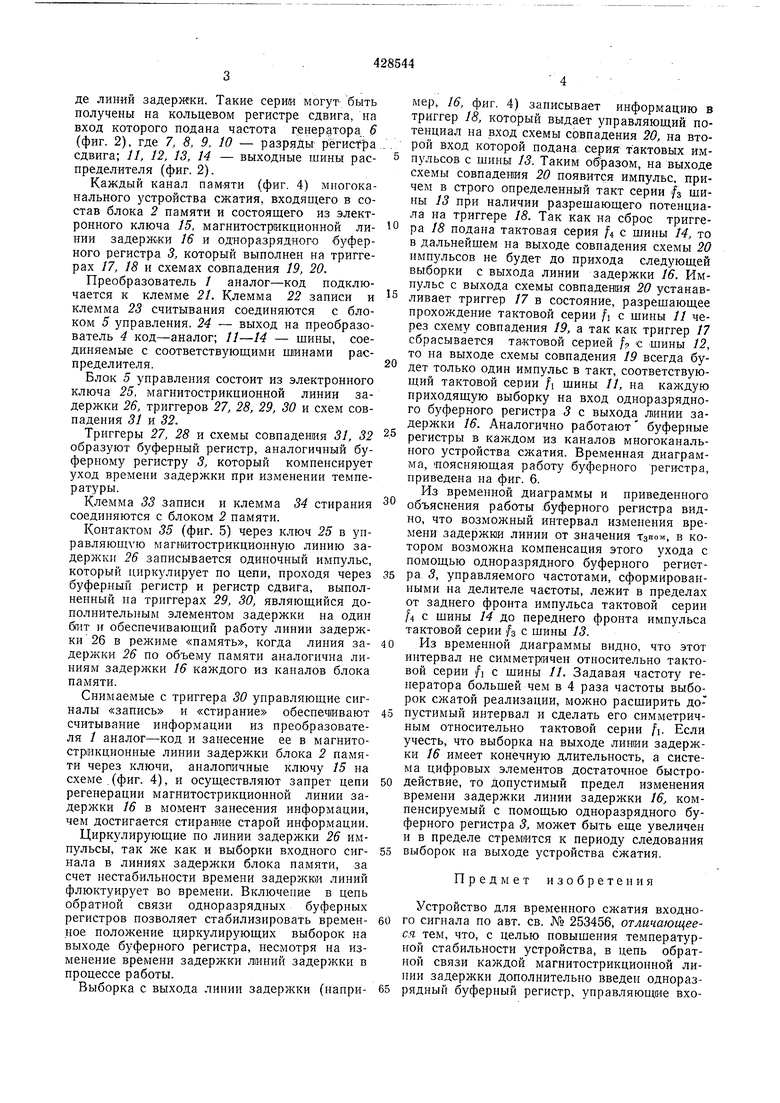

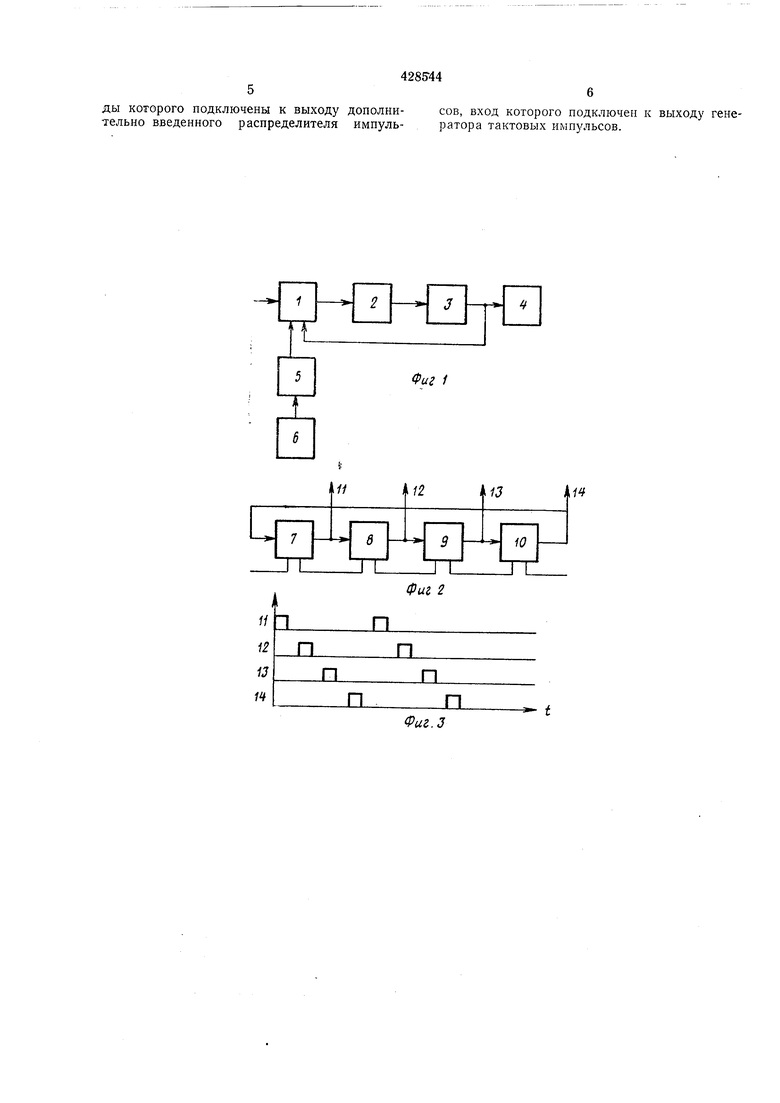

На фиг. 1 иредставлена блок-схема предлагаемого устройства; на фиг. 2 - блок-схе.ма распределителя (делителя частоты); на фиг. 3 - диаграММа работы распределителя; на фИг. 4 - блок-схема одного нз каналов ламяти, входящего в блок памяти; на фиг. 5 - схема блока унравлеиия; на фиг. 6 - диаграмма работы буферного регистра.

Предлагаемое устройство состоит из преобразователя / аиалог-код, выход которого соединен со входом блока 2 памяти, выполненного на магннтострнкционных линиях задержки, в цепь обратной связи которых включены одноразрядные буферные регистры 3. Выходы буферных регистров 3 соединены со входами преобразователей код-аналог 4. Унравление преобразователем 1 аналог-код и буферными регистрами 3 осуществляется блоком 5 управления, на вход которого иостуиает частота со стабильного (например, кварцевого) геиератора 6 тактовых импульсов, а выходы блока 5 уиравления соединены с преобразователем / аналог-код и блоком 2 памяти.

В блоке 5 унравлеиия имеется делитель частоты, который формирует управляющие нмпульсы, обеспечивающие синхронную устойчивую работу многоканального устройства сжатия. Частота генератора 6 определяется частотой выборок на выходе блока 2 намяти н возможным уходом времени задержки линий

с точки зрения обеспечения компенсации этого ухода буферным регистром. Для обеспече шя работы буферного регистра частота генератора 6 должна быть не менее, чем в 4 раза больще частоты сжатых выборок на выходе

линии задержки каждого из каналов. Таким образом, на делителе частоты в блоке 5 управления формируется не менее четырех сдвинутых одна относительно другой тактовых серий, частота импульсов каждой из которых

равна номинальной частоте выборок па выходе линий задержки. Такие серии могут- быть получены на кольцевом регистре сдвига, на вход которого подана частота генератора 6 (фиг. 2), где 7, 8, 9, 10 - разряды рёгист ра сдвига; //, 12, 13, 14 - выходные шины распределителя (фиг. 2).

Каждый канал пам-яти (фиг. 4) многоканального устройства сжатия, входящего в состав блока 2 памяти и состоящего из электронного ключа 15, магнитострикционной линии задержки 16 и одноразрядного буферного регистра 3, который выполнен на триггерах 17, 18 и схемах совпадения 19, 20.

Преобразователь / аналог-код подключается к клемме 21. Клемма 22 записи и клемма 23 считывания соединяются с блоком 5 управления. 24 - выход на преобразователь 4 код-аналог; //-14 - шины, соединяемые с соответствующими щинами распределителя.

BvioK 5 управления состоит из электронного ключа 25, магнитострикционной линии задержки 26, триггеров 27, 28, 29, 30 и схем совпадения 31 и 32.

Триггеры 27, 28 и схемы совпадения 31, 32 образуЕОт буферный регистр, аналогичный буферному регистру 3, который компенсирует уход времени задержки при изменении температуры.

Клемма 33 записи и клемма 34 стирания соединяются с блоком 2 памяти.

Контактом 35 (фиг. 5) через ключ 25 в управляющую магвитострикционную линию задержки 26 записывается одиночный импульс, который циркулирует по цепи, проходя через буферный регистр и регистр сдвига, выполненный на триггерах 29, 30, являющийся дополнительным элементом задержки на один бит и обеспечивающий работу линии задержки 26 в режиме «намять, когда линия задержки 26 по объему памяти аналогична линиям задержки 16 каждого из каналов блока памяти.

Снимаемые с триггера 30 управляющие сигналы «запись и «стирание обеспечивают считывание информации из преобразователя / аналог-код и занесение ее в магнитострикционные линии задержки блока 2 памяти через ключи, аналогичные ключу 15 на схеме (фиг. 4), и осуществляют запрет цепи регенерации магнитострикционной линии задержки 16 в момент занесения информации, чем достигается стирание старой информации.

Циркулирующие по линии задержки 26 импульсы, так же как и выборки входного сигнала в линиях задержки блока памяти, за счет нестабильности времени задержки линий флюктуирует во времени. Включение в цепь обратной связи одноразрядных буферных регистров позволяет стабилизировать временное положение циркулирующих выборок на выходе буферного регистра, несмотря на изменение времени задержки линий задержки в процессе работы.

Выборка с выхода линии задержки (например, 16, фиг. 4) записывает информацию в триггер 18, который выдает управляющий потенциал на вход схемы совпадения 20, на второй вход которой подана серия тактовых импульсов с шины 13. Таким образом, на выходе схемы совпадения 20 появится импульс, причем в строго определенный такт серии fs шины 13 при наличии разрешающего потенциала на триггере 18. Так как на сброс триггера /5 подана тактовая серия /4 с щины 14, то в дальнейшем на выходе совпадения схемы 20 импульсов не будет до прихода следующей выборки с выхода линии задержки 16. Импульс с выхода схемы совпадения 20 устанавливает триггер 17 в состояние, разрешающее прохождение тактовой серии fi с шины // через схему совпадения 19, а так как триггер 17 сбрасывается тактовой серией / с шины 12, то на выходе схемы совпадения 19 всегда будет только один импульс в такт, соответствующий тактовой серии f шины 11, на каждую приходящую выборку на вход одноразрядного буферного регистра 3 с выхода Л1инии задержки 16. Аналогично работают буферные регистры в каждом из каналов многоканального устройства сжатия. Временная диаграмма, «поясняющая работу буферного регистра, приведена на фиг. 6.

Из временной диаграммы и приведенного

объяснения работы .буферного регистра видно, что возможный интервал изменения времени задержки линии от значения Гзпом, в котором возможна компенсация этого ухода с помощью одноразрядного буферного регис-т5 ра 3, управляемого частотами, сформированными на делителе частоты, лежит в пределах от заднего фронта импульса тактовой серии /4 с шины 14 до переднего фронта импульса тактовой серии fs с шины 13.

0 Из временной диаграммы видно, что этот интервал не симметричен относительно тактовой серии f с щины //. Задавая частоту генератора больщей чем в 4 раза частоты выборок слсатой реализации, можно расширить допустимый интервал и сделать его симметричным относительно тактовой серии fi. Если учесть, что выборка на выходе линии задержки 16 имеет конечную длительность, а система цифровых элементов достаточное быстродействие, то допустимый предел изменения времени задержки линии задержки 16, компенсируемый с помощью одноразрядного буферного регистра 3, может быть еще увеличен и в пределе стремится к периоду следования

5 выборок на выходе устройства сжатия.

Предмет изобретения

Устройство для временного сжатия входно0 го сигнала по авт. св. № 253456, отличающееся тем, что, с целью повышения температурной стабильности устройства, в цепь обратной связи каждой магнитострикционной линии задержки дополнительно введен однораз5 рядный буферный регистр, управляющие входы которого подключены к выходу дополнительно введенного распределителя импульсов, вход которого подключен к выходу генератора тактовых иыпзльсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сбора данных для цифрового анализатора сигналов | 1990 |

|

SU1751683A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| ЦИФРОВОЙ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU297071A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2109399C1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1223248A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сжатия информации | 1986 |

|

SU1336080A1 |

| ИНТЕРПОЛЯТОР | 1991 |

|

RU2006938C1 |

Даты

1974-05-15—Публикация

1971-10-12—Подача