Известны преобразователи двоичного кода в частоту, содержащие генератор тактирующих импульсов, соединенный через схему совпадения со счетчиком, линию задержки, вход которой соединен с генератором, а выходы - со схемами совпадения, и регистр преобразуемого кода.

Предлагаемый преобразователь отличается тем, что он содержит выходную схему совпадения, дешифратор, сумматор, регистры управления, причем вход дешифратора соединен с сумматором младших разрядов преобразуемого кода, выход дешифратора соединен со схемами совпадения, вход одного регистра управления через схему совпадения подключен к счетчику, выход этого регистра через схему совпадения связан с другим регистром, а последний соединен с выходной схемой совпадения.

Это позволяет повысить точность преобразования.

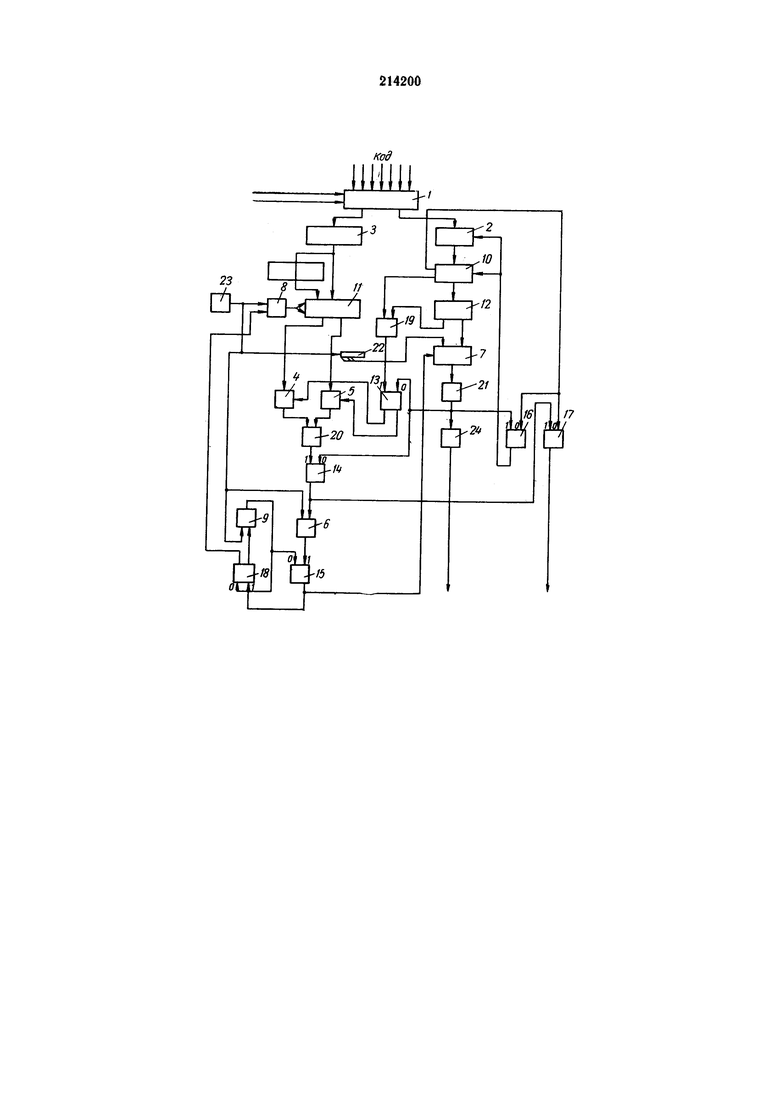

На чертеже показана блок-схема предлагаемого устройства.

Устройство содержит приемный регистр 1, схемы совпадения 2-9, сумматор 10, счетчик 11, дешифратор 12, регистры 13-18, схемы 19-21 «ИЛИ», линию задержки 22, генератор 23 эталонной частоты и усилитель 24.

На приемный регистр 1 преобразователя поступает n-разрядный двоичный код. Через схемы совпадения 2 с регистра 1 на сумматор 10 поступают n1 разряды (младшие), где они складываются с содержимым сумматора от предыдущего преобразования, и (n-n1) разряды кода (старшие) через схемы совпадения записываются на счетчик 11.

Если в результате суммирования выработается сигнал переполнения φ-1 или с дешифратора 12 поступит сигнал «О», то, пройдя через схему 19 «ИЛИ», эти сигналы установят в «1» регистр 13, который подключит к разрядам счетчика 11 схему совпадения 4. Если сигналы переполнения φ-1 и «О» выработаны не будут, то к разрядам счетчика 11 останется подключенной схема совпадения 5, что разрешает счетчику 11 просчитать на единицу больше, чем при подключении схемы совпадения 4.

Сигнал φ-1 показывает, что время, соответствующее коду на сумматоре 10, больше одного периода Тэ. Счетчик 11 просчитывает импульсы эталонной частоты с периодом Тэ.

При заполнении счетчика 11 через схемы совпадения 4 или 5 и схему 20 «ИЛИ» устанавливается в «1» регистр 14, который разрешает прохождение через схему совпадения 6 следующего импульса периода Тэ. Сигнал на выходе схемы совпадения 6 устанавливает в «1» регистр 15, который подготавливает всю группу схем совпадения 7, подсоединенных к дешифратору 12. Кроме того, каждая из этих схем совпадения связана с соответствующим выводом линии задержки 22, на вход которой поступают импульсы. При совладении всех трех сигналов на входе какой-либо схемы совпадения на ее выходе появляется сигнал, который, пройдя через схему 21 «ИЛИ», определяет конец временного интервала, соответствующего коду.

По указанному сигналу происходит установка в «0» регистров 13 и 14, установка в «1» регистра 16 и перепись «старших» разрядов с регистра 1 на счетчик 11, причем к этому моменту времени на счетчике может находиться как новый, так и старый код. Регистр 16 разрешает перепись «младших» разрядов кода с регистра 1 на сумматор 10 и дает сигнал «начало суммирования». По сигналу «конец суммирования» регистры 16 и 17 устанавливаются в «0». Регистр 17 устанавливается в «1» по сигналу «1» регистра 14 для запрещения выдачи на время окончания преобразования на регистр 1 преобразователя нового кода.

Кроме управления схемой совпадения 7 регистр 15 устанавливает в «1» регистр 18, который своим нулевым плечом разрешает прохождение от генератора 23 эталонных импульсов через схему совпадения 9 на вход счетчика 11 импульсов Тэ. Установка в «0» регистра 18 производится первым, после установки его в «1», импульсом Тэ, проходящим через схему совпадения 9, причем этот импульс на вход счетчика 11 не поступает. Таким образом, счетчик 11 просчитывает количество периодов Тэ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь кода во временной интервал | 1980 |

|

SU928635A1 |

| Преобразователь перемещения в код | 1990 |

|

SU1783608A1 |

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1990 |

|

SU1725399A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU744546A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД С СИСТЕМОЙ САМОКОНТРОЛЯ | 1972 |

|

SU358779A1 |

| Устройство для сортировки | 1989 |

|

SU1633428A1 |

Преобразователь двоичного кода в частоту, содержащий генератор тактирующих импульсов, соединенный через схему совпадения со счетчиком, линию задержки, вход которой соединен с генератором, а выходы - со схемами совпадения, и регистр преобразуемого кода, отличающийся тем, что, с целью повышения точности, он содержит выходную схему совпадения, дешифратор, сумматор, регистры управления, причем вход дешифратора соединен с сумматором младших разрядов регистра преобразуемого кода, выход дешифратора соединен со схемами совпадения, вход одного регистра управления через схему совпадения подключен к счетчику, выход этого регистра через схему совпадения соединен с другим регистром, а последний соединен с выходной схемой совпадения.

Авторы

Даты

1968-06-07—Публикация

1967-02-04—Подача