2. Преобразователь по п.1/ отличающийся тем, что блок десятичной коррекции содержит четырехразрядный сумматор, элемент И. и элемент НЕ, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом третьего разряда четырехразрядного csMMaTopa, выход четвертого разряда которого соединен с входом элемента НЕ, а выход переноса четырехразрядного сумматора является выходом переноса блока десятичной коррекции и соединен с входом переноса четырехразрядного сумматора, выход первого разряда которого, выход элемента И и выход четвертого разряда четырехразрядного сумматора являются разрядными выходами блока десятичной коррекции, входы трех младших разрядов которого являются первыми в ходами,, второго, третьего и четвертого разрядов четырехразрядного сумматора соответственно, второй вход четвертого разряда четырехразрядного сум|матора является входом четвертого разряда блока десятичной коррекции. Первый вход первого разряда четырехразрядного сумматора соединен d входе первого разряда блока десятичной коррекции, вход четвертого разряда которого соединен с вторыми входами второго и третьего разрядов четырехразрядного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU881730A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU744546A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

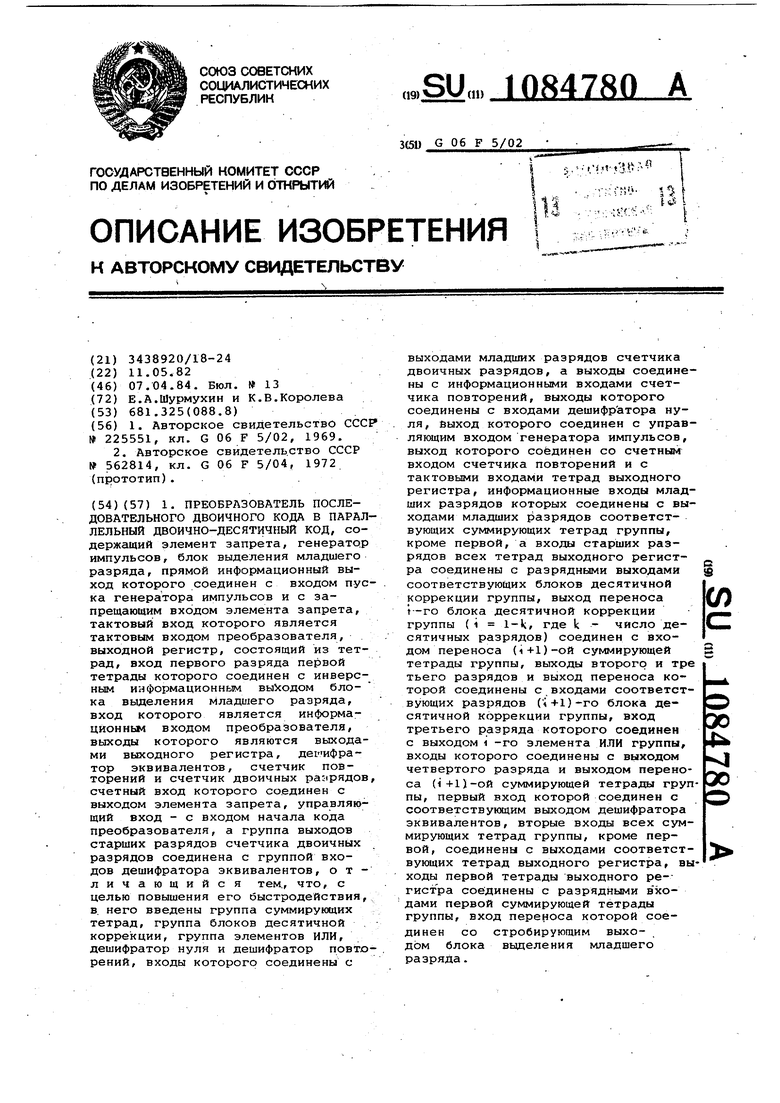

1. ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД, содержащий элемент запрета, генератор импульсов, блок выделения младшего разряда, прямой информационный выход которого соединен с входом пуска генератора импульсов и с запрещающим входом элемента запрета, тактовый вход которого является тактовым входом преобразователя, выходной регистр, состоящий из тетрад, вход первого разряда первой тетрады которого соединен с инверсным информационным выходом блока выделения младшего разряда, вход которого является информацйонньм входом преобразователя, выходы которого являются выходами выходного регистра, дегифратор эквивалентов, счетчик повторений и счетчик двоичных ра;фядов, счетный вход которого соединен с выходом элемента запрета, управляк щий вход - с входом начала кода преобразователя, а группа выходов старших разрядов счетчика двоичных разрядов соединена с группой входов дешифратора эквивалентов, отличающийся тем., что, с целью повышения его быстродействия, в. него введены группа суммирующих тетрад, группа блоков десятичной . коррекции, группа элементов ИЛИ, дешифратор нуля и дешифратор повто- . рений, входы которого соединены с выходами младших разрядов счетчика двоичных разрядов, а выходы соединены с информационными входами счетчика повторений, выходы которого соединены с входами дешифратора нуля, Выход которого соединен с управлякмдим входом генератора импульсов, выход которого соединен со счетным входом счетчика повторений и с тактовыми входами тетрад выходного регистра, информационные входы младших разрядов которых соединены с выходами младших разрядов соответствующих суммирующих тетрад группы, кроме первой, а входы старших разрядов всех тетрад выходного регистра соединены с разрядными выходами соответствующих блоков десятичной (Л коррекции группы, выход переноса t-го блока десятичной коррекции группы (i 1-k, где k - число десятичных разрядов) соединен с входом переноса (ч +1)-ой суммирующей тетрады группы, выходы второго и тре тьего разрядов и выход переноса которой соединены с входами соответствующих разрядов (;+)-го блока десятичной коррекции группы, вход 00 4 третьего разряда которого соединен с выходом 1 -го элемента ИЛИ группы, входы которого соединены с выходом четвертого разряда и выходом перено00 са

Изобретение относится к вычислительной технике и предназначено для преобразования последовательного .двоичного кода, поступающего младши ми разрядами вперед, в параллельный двоично-десятичный. Известен преобразователь последювательного двоичного кода в двоич но-десятичный, содержащий счетчик двоичных разрядов последовательного кода, старшие два разряда которого соединены с одним из входов дешифратора, генератор тактов.ых импульсо выход которого соединен с входами счетчика весовых эквивалентов, выходы разрядов которого соединены с другими входами дешифратора,, а его выходы подключены к соответствующим входам тетрад выходного регистра l Недостатки этого преобразователя заключаются в отсутствии возможности одновременного получения на выходе устройства всего преобразованного числа, многократном повторении поступления на вход устройства последовательного двоичного кода наличии схем сравнения десятков и схем вычитания, для управления ксвторыми требуется дополнительная ап паратура. Наиболее близким к предлаг мому по технической сущности и схемному построению является преобразо.ватель последовательного двоичного кода в параллельный двоично-десятичный, содержащий блок выделения младшего разряда, выход которого со динен с входом генератора импульсов с входом первого разряда младшей тетрады выходного регистра, с вхо;JOMэлемента запрета,выход кото- рого соединен с входом счетчика двоичных разрядов последовательного кода, выходной регистр и дешифратор эквивалентов. В известном устройстве суммирование десятичных эквивалентов преобразуемого двоичного кода ocjmiecTBляется методом накопления десятичных эквивалентов двоичного кода на тетрадах выходного регистра, т.е. путем пересчета разнесенных во времени десятичных эквивалентов двоичного числа выходным регистром, который является двоично-десятичным счетчиком. Для этого в устройство введен счетчик эквивалентов, а дешифратор эквивалентов кроме функции формирования десятичных, эквивалентов выполняет функцию разнесения их во времени 2 . Недостаток известного преобразователя состоит в относительно низком быстродёйствии.. Целью изобретения является повышение быстродействия преобразователя. Поставленная цель достигается тем, что в преобразователь послеловательного двоичного кода в параллельный двоично-десятичный код, содержащий элемент запрета, генератор импульсов, блок выделения младшего разряда, прямой информационный выход которого соединен с входом пуска генератора импульсов и с запрещающим входом элемента запрета, тактовый вход которого является тактовым входом преобразователя, выходной регистр, состоящий из тетрад, вход первого разряда первой тетрады которого соединен с инверсным информационным выходом блока деления младшего разряда, вход которого является информационным вхо дом преобразователя, выходы которого, являются выходами выходного регистра, дешифратор эквивалентов, счетчик повторений и счетчик двоич разрядов, счетный вход которого со динен с выходом элемента запрета, управляющий вход - с входом начала кода преобразователя, а группа выходов старших разрядов счетчика двоичных разрядов соединена с груп пой входов дешифратора эквивалентов, дополнительно введены группа суммирующих тетрад, группа блоков десятичной коррекции, группа элементов ИЛИ, дешифратор нуля и дешифратор повторений, входы которого соединены с выходами Младших разрядов, а выходы соединены с информационными входами счетчика повторе ний, выходы которого соеди{| ны с входами дешифратора нуля, выход ко торого соединен с управляющим входо генератора импульсов, выход которог соединен со счетным входом счетчика повторений и с тактовыми входами тетрад выходного регистра, информационные входы младших разрядов которых соединены с выходами младших разрядов соответствующих суммирующи тетрад группы, кроме первой, а входы старших разрядов всех тетрад выходного регистра соединены с разрядными выходами соответствующих блоков десятичной коррекции группы выход переноса t-го блока десятичной коррекции группы , где V - число десятичных разрядов) соед нен с входом переноса (+1)-ой сум мирующей тетрады группы, выходы второго и третьего разрядов и выход переноса которой соединены с в.ходами соответствующих разрядов (i+l)-ro блока десятичной коррекции группы, вход третьего разряда которого соединен с выходом i -го элемента ИЛИ группы, входы которого соединены с выходом четвертого разряда и выходом переноса (+1)-ой суммирующей тетрады группы, первый вход которой соединен с соответствующим выходом дешифратора эквивалентов, вторые входы всех сум мирующих тетрад группы, кроме перво соединены с выходами соответствующи тетрад.выходного регистра, выходы первой тетрады выходного регистра соединены с разрядными входами первой суммирующей тетрады группы, вхо переноса которой соединен со стробирующим выходом блока вьщеленйя младшего разряда. Блок десятичной коррекции содержит четырехразрядный сумматор, элемент И и элемент НЕ, выход которого соединен с первым входом эле мента И, второй вход которого соединен с выходом третьего разряда четырехразрядного сумматора, выход четвертого разряда которого соединен с входом элемента НЕ, а выход переноса четырехразрядного сумматора является выходомопереноса блока десятичной коррекции и соединен с входом переноса четырехразрядного сумматора, выход первого разряда которого,.выход элемента и и выход четвертого разряда четырехразрядного сумматора являются разрядными выходами блока десятичной коррекции, входы трех младших разрядов которого являются первыми входами второго, третьего и четвертого-разрядов четырехразрядного сумматора соответственно, второй вход четвертого разряда четырехразрядного сумматора является входом четвертого разряда блока десятичной коррекции, первый вход первого разряда четырехразрядного сумматора соединен с входом первого разряда блока десятичной коррекции, вход четвертого разряда которого соединен с вторыми входами второго и третьего разрядов четырехразрядного сумматора. На фиг.1 представлена блок-схема предлагаемого преобразователя; на фиг.2 - функциональная схема двух тетрад преобразователя; на фиг.З функциональная схема дешифратора эквивалентов. Преобразователь содержит блок 1 выделения младшего разряда, выход которого соединен с входом элемента 2 запрета и входом генератора 3 импульсов, счетчик 4 двоичных разрядов, предназначенный для подсчета тактовых импульсов, сопровождающих разряды двоичного кода. Выходы двух младших разрядов счетчика 4 соединены с входами дешифратора 5 повторений, а выходы-тарших разрядов - с входами дешифратора б эквивалентов. Выходы дешифратора 5 повторений соединены с входами счетчика 7 повторений, работающего на вычитание, выходы которого соединены с входами дешифратора 8 нуля, выход генератора 3 импульсов соединен со счетным входом счетчика 7 и тактовыми входами выходного регистра 9, состоящего из тетрад 10. Регистр 9 является регистром памяти промежуточных сумм и конечного результата преобразования. Выходы тетрад 10 регистра 9 являются выходами преобразователя. Преобразователь содержит суммирующие тетрады 11 и 12, в совокупности образующие группу суммирукнцих тетрад, а также труппу .элементов ИЛИ 13 и группу блоков 14 десятичной коррекции.

Блок 14 десятичной коррекции (фиг.2} содержит четырехразрядный qy vMgiTop 15, элемемт И 16 и элемент НЕ 17,причемвход первого,третьего и

четвертого разрядов сумматора являются входами блока деся.тичной, коррекции с весом(2, 22, 2) соответственно. Выход первого разряда сумматора является выходом блока 14 с весом , выход четвертого разряда сумматора 15 является вы,ходом блока 14 с весом 2. .

Выход элемента И является, выходом блока 14с весом 2,- , выход переноса сумматора 15 является выходом переноса блока 14 десятичной коррекции с весом 1 О, где wi - номер тетрады -преобразователя.

Дешифратор 6 эквивалентов (фиг.З) содержит два элемента ИЛИ 18. и 19 и элементы И 20-22.

Рассмотрим работу преобразователя при условии, что количество разрядов преобразуемого двоичного числа равно п 17.

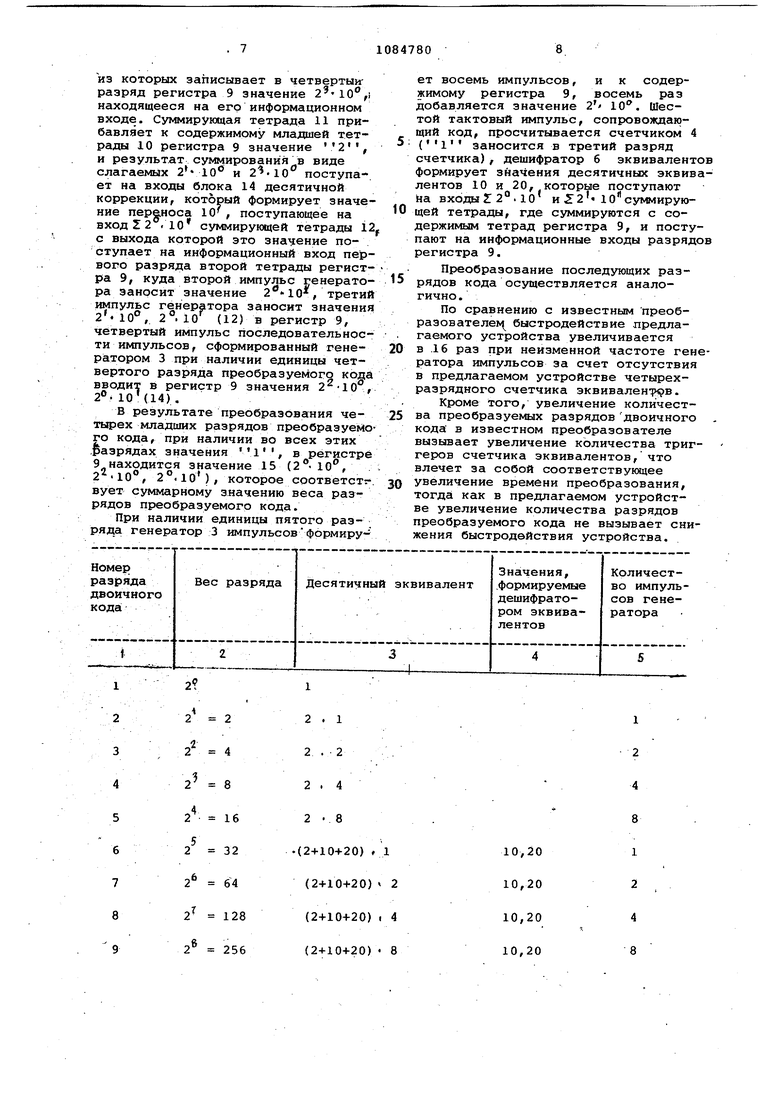

Вес 16 двоичных разрядов (2 -2 ) и разложение их fea десятичные экви- ; валенты приведены в таблице.

Максимальное преобразуемое число в данном случае, равное 131071, со держит 7 знаков, т.е. устройство дол жно содержать шесть тетрад преобразования (единицы, десятки, сотни синицы тысяч, йесятки тысяч, ..сотни тысяч).

Преобразование осуществляется еле дующим образом.

Импульс начала кода устанавливает счетчик 4 в нулевое состояние и подготавливает блок 1 для выделения младшего разряда последовательного двоичного кода. Поступивший на вход блока 1 первый разряд двоичного с весом 2 кода выделяется этим блоком и подается на вход первого разряда младшей тетрады 10 выходного регистра 9, кроме того, сигнал с блока 1 запрещает прохождение через элемент 2 запрета импульса тактовой частоты, сопровождающего разряд (младший) последовательного двоичного кода, на вход счетчика 4 двоичных разрядов. Тактовые импульсы, сопровождающие второй и последующие разряды двоичного Кода, просчитываются счетчиком Дешифратор 5 анализирует состояние двух младших разрядов счетчика 4 и заносит одно из Значени дешифратора(1,2,4 или 8) в счетчрк 7. Кроме того, блок 1 формирует по второму тактовому импульсу строб кода, который в качестве .эквивалента 2 поступает на входZ210° суммирукщей тетрады 11, с его выходи - на вход 10 блока 14 де сятичной коррекции ис выхода

10 последней на информационный вход второго разряда младшей тетрады 10 выходного регистра 9. Второй тактовый импульс, сопровождав щий код, с выхода элемента 2 запрета поступает в счетчик 4, состояние которого анализируется дешифрат.ором 5 и отрабатывается счетчиком 7 повторений.

При наличии в преобразуемом двоичном коде единицы второго разряда с весом 2 блок 1 выделяется импульс второго разряда кода, который запускает генератор 3, импульсы которого просчитываются счетчиком 7 работающим на вычитание.

Дешифратор 5 устанавливает счетчик 7 -в . состояние . После первого импульса генератора на счетчике 7 устанавливается значение, равное О, и дешифратор 8 нуля запрещает работу генератора 3 импульсов. Этот же импульс генератора заносит значение 2--.10 во второй разряд младшей тетрады 10 регистра 9. Это значение поступает на второй вход ю суммирующей тетрады 11 на первый вход которой поступает значение 2 с блока 1. С выхода сукмирующей тетрады 11 значение 22.10° поступает на блок 14 десятичной коррекции, с выхода которого.поступает на информационный вход тетрады 10 регистра 9.

Третий тактовый импульс, сопровождающий код, просчитывается счетчиком 7, состояние которого анализируется дешифратором 5, который в свою очередь заносит в счетчик 7 значение 2 .

При наличии единицы третьего разряда (2) преобразуемого кода генратор 3 формирует два импульса.

Первый импульс генератора заносит в третий разряд тетрады 10 значение 2 -10 , которое поступает на. вход Г 2.1 о суш4ирую1цей тетрады 11, где суммируется со значением 2 с блока 1. ,

Результат суммирования поступает на блок 14 десятичной коррекции, с выхода которого значения 2 10 и 10 поступают на информационные входы второго и третьего разрядов регистра 9, и вторым импульсом с генератора 3 за носятся в регистр..

Содержимое регистра снова поступает на суммйрукийую тетраду 11 где вновь суммируется со значением 2 с блока 1 и через блок 14 десятичной коррекции значение поступает на информационный вход четвертого разряда регистра 9.

При наличии единицы четвертого разряда кода с весом 2 генератор формирует четыре шипульса, первый

из которых записывает в четвертыиразряд регистра 9 значение 210 , находящееся на его информационном входе. Суммирующая тетрада 11 прибавляет к содержимому младшей тетрады 10 регистра 9 значение 2, и результат суммирования в виде слагаемых и 210 поступает на входы блока 14 десятичной коррекции, который формирует значение переноса 10 , поступающее на вход Z2 .10 суммирующей тетрады 12 с выхода которой это значение поступает на информационный вход первого разряда второй тетрады регистра 9, куда второй импульс генератора заносит значение , третий импульс генератора заносит значения 2« 10°, 2 . 10 (12) в регистр 9, четвертый импульс последовательности импульсов, сформированный генератором 3 при наличии единицы четвертого разряда преобразуемого кода вводит в регистр 9 значения 2 10, 2°.10(14).

В результате преобразования четырех младших разрядов преобразуемого кода, при наличии во всех этих .разрядах значения 1, в регистре 9 находится значение 15 ( ю, 2 -Ю, 2°. 10 ), которое соответст: вует суммарному значению веса разрядов преобразуемого кода.

При наличии единицы пятого разряда генератор 3 импульсовформиру2

1

2 4

2 8

2 8

.(24-10+20) 1 2 32 2 64 (2+10+20) 2 2 128 (2+10+20) . 4 2 256 (2+10+20) 8

ет восемь импульсов, и к содержимому регистра 9, восемь раз добавляется значение 2 10. Шестой тактовый импульс, сопровождающий код, просчитывается счетчиком 4

С

заносится в третий разряд

счетчика), дешифратор б эквивалентов формирует зйачения десятичных эквивалентов 10 и 20, которые поступают на входа12;2°.10 и 10суммирую0 щей тетрады, где суммируются с содержимым тетрад регистра 9, и поступают на информационные входы разрядов регистра 9.

Преобразование последующих разрядов кода осуществляется аналогично.

По сравнению с известным преобразователе быстродействие предлагаемого устройства увеличивается в .16 раз при неизменной частоте генератора импульсов за счет отсутствия в предлагаемом устройстве четырехразрядного счетчика эквиваленр9в. Кроме того, увеличение количест5 ва преобразуемых разрядов двоичного кода в известном преобразователе вызывает увеличение количества триггеров счетчика эквивалентов, что влечет за собой соответствующее увеличение времени преобразования, тогда как в предлагаемом устройстве увеличение количества разрядов преобразуемого кода не вызывает снижения быстродействия устройства.

1

2 4 8 1 2 4 8

(24-100+400) 1

512

. .

2 - 1024

(2-«-100 f400) 2 .Л

2 2048 (2+100+400). 4 2 « 4096 (2+100+400) 8 . 2 8192

(2+10+8 04-100+8T) 2 16384

(2+10+8b+100+8T) 2

2 32768

(2+10+80+100+8T) 4

2 65536

(2+10+80+100+81) 8

100,400

100,400 100,400

10,80,100,Вт

10,80,100,Вт

10,80,100,8т

V 10,80,100,8т

1 1 1 I I 1 I

(2.2}-W (2:. (г.. ..2 }-/ff .. ..2}-rO г-2}-Г&

фиг. f

SHSuS. 20

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 225551, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 562814, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-07—Публикация

1982-05-11—Подача