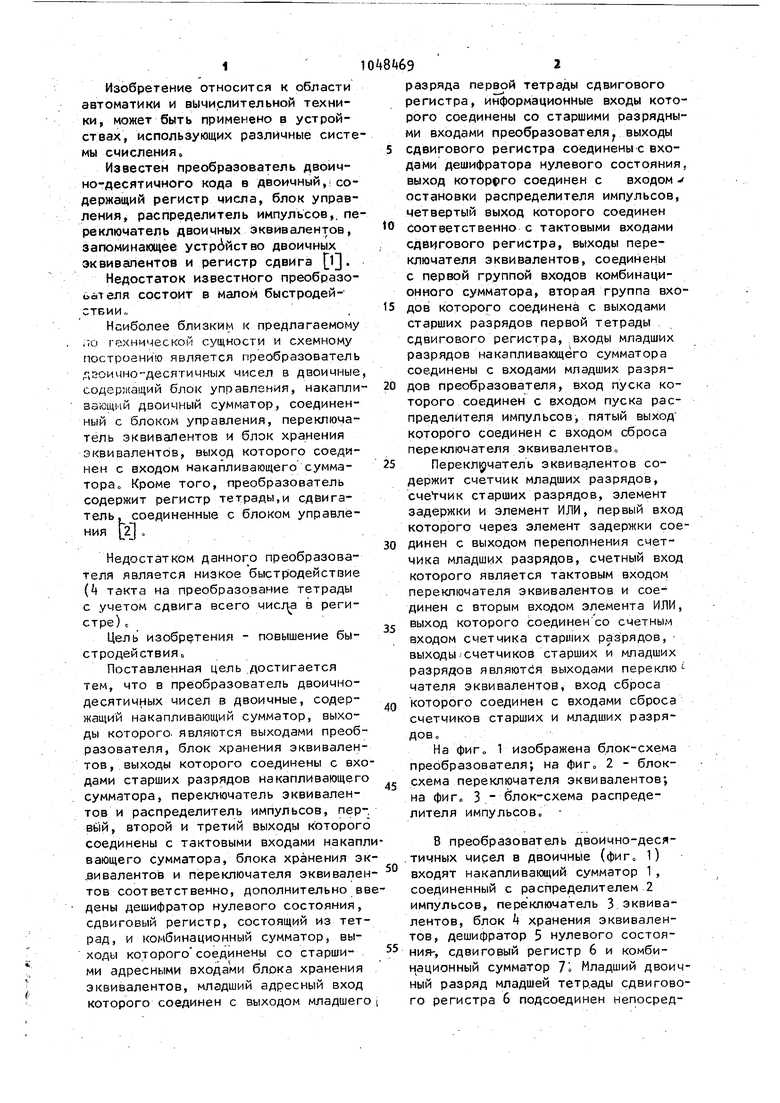

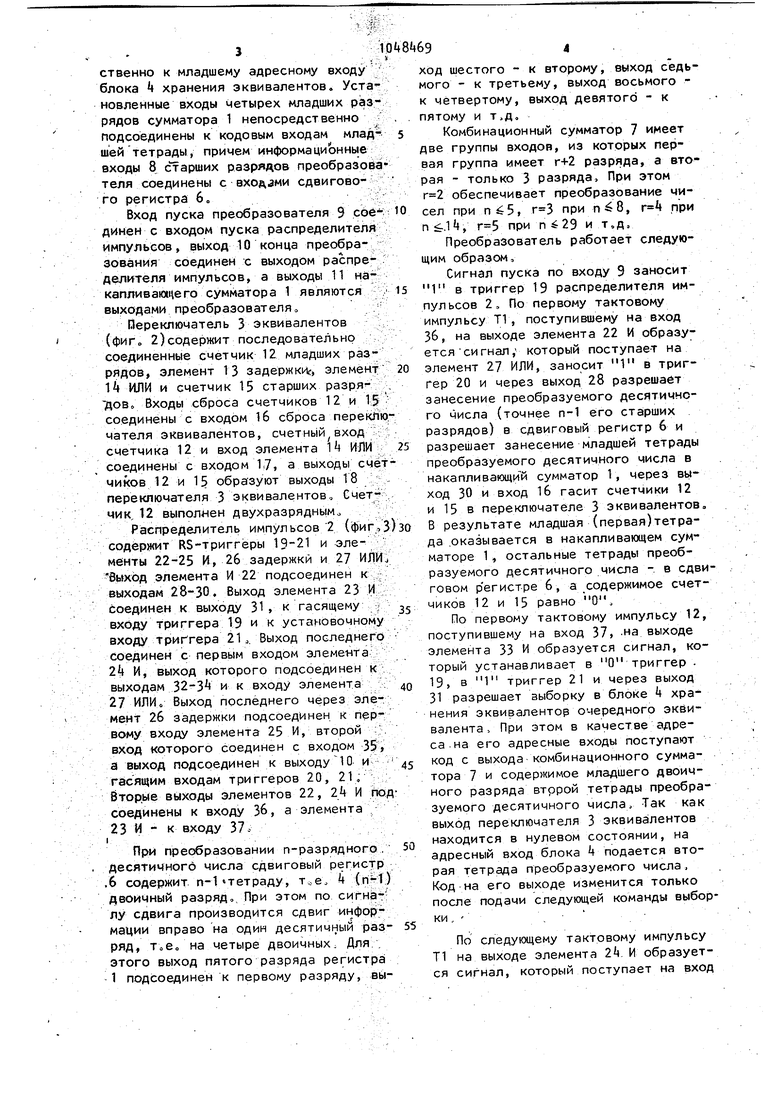

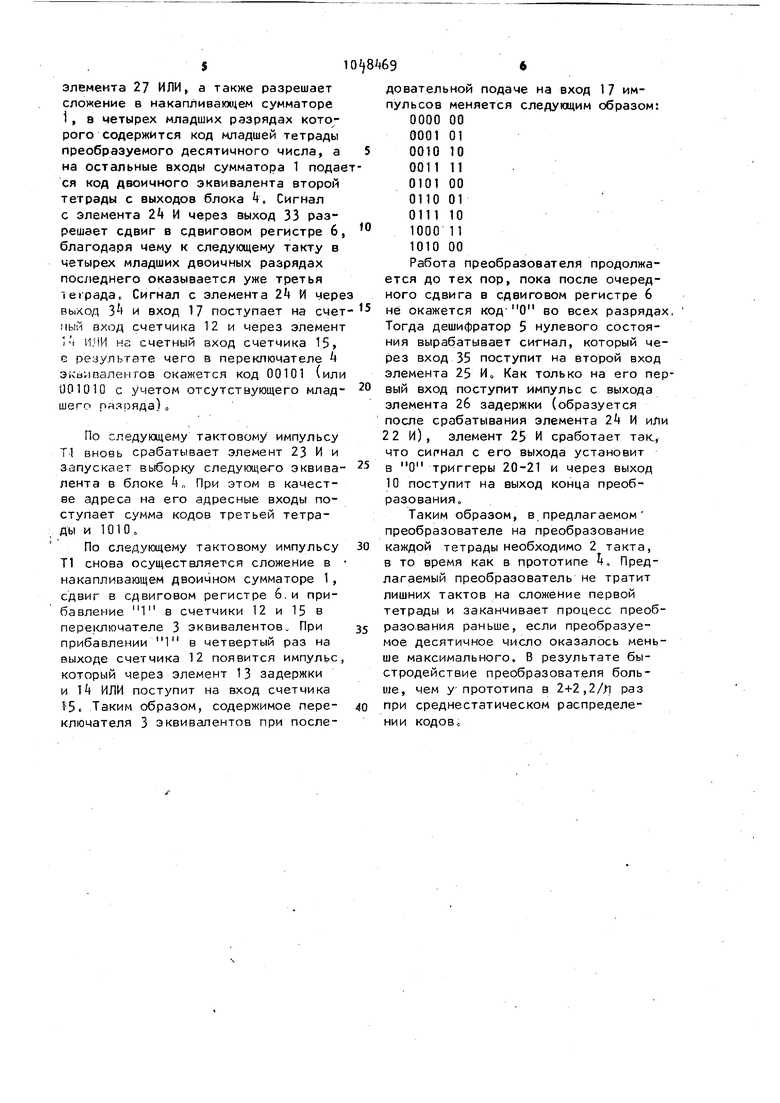

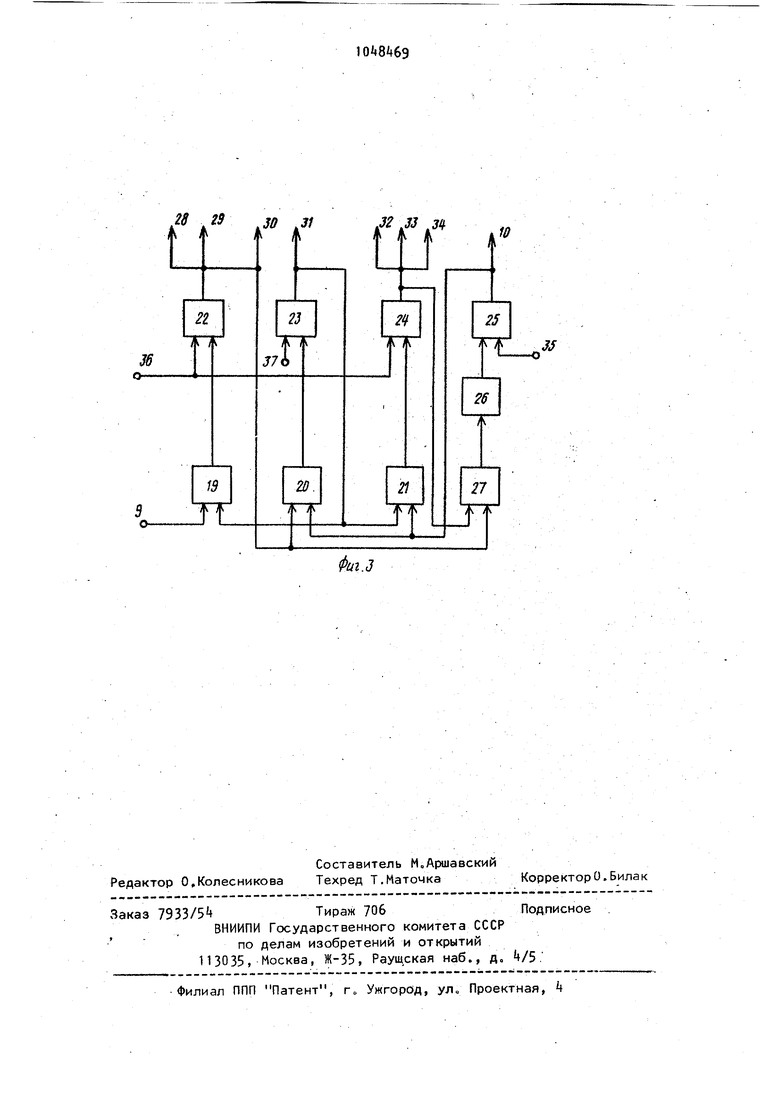

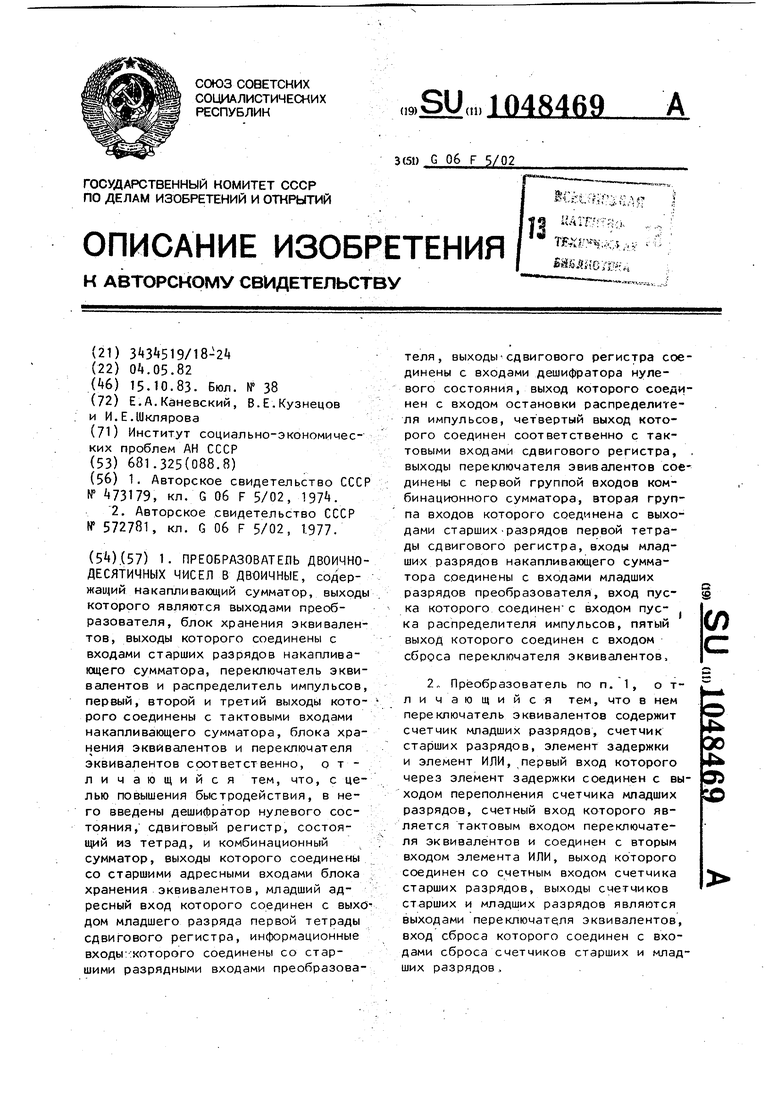

Изобретение относится к области автоматики и вычислительной техники, может быть применено в устройствах, Использующих различные систе мы счисления о Известен преобразователь двоично-десятичного кода в двоичный,; содержащий регистр числа, блок управления, распределитель импульсов,, пе реключатель двоичных эквивалентов, запоминающее устройство двоичных эквивалентов и регистр сдвига ij. Недостаток известного преобразоиателя состоит в малом быстродействии,, Наиболее близким к предлагаемому i7O технической сущности и схемному построению ЯЕзляется преобразователь дйоично десятичных чисел в двоичные содержащий блок управления, накапли вающий двоичный сумматор, соединенный с блоком управления, переключа тель эквивалентов и блок хранения эквивалентЬв, выход которого соединен с входом накапливающего сумматора о Кроме того, преобразователь содержит регистр тетрады,и сдвигатель, соединенные с блоком управления 2 о Недостатком данног о преобразователя является низкое быстродействие ( такта на преобразование тетрады с учетом сдвига всего числа в регистре) о Цель изобретения - повышение быстродействиЯс, Поставленная цель достигается тем, что в преобразователь двоичнодесятичных чисел в двоичные, содержащий накапливающий сумматор, выходы которого, являются выходами преобразователя, блок хранения эквивалентов , выходы которого соединены с вхо дами старших разрядов накапливающего сумматора, переключатель эквивалентов и распределитель импульсов, первь1й, второй и третий выходы которог соединены с тактовыми входами накапл вающего сумматора, блока хранения э .вивалентов и переключателя эквивале тов соответственно, дополнительно в дены дешифратор нулевого состояния, сдвиговый регистр, состоящий из тет рад, и комбинационный сумматор, выходы которогосоединены со старшими адресными входами блока хранения эквивалентов, младший адресный вход которого соединен с выходом младшего 92 разряда первой тетрады сдвигового регистра, информационные входы которого соединены со старшими разрядными входами преобразователя выходы сдвигового регистра соединены с входами дешифратора нулевого состояния, выход котор| го соединен с входом остановки распределителя импульсов, четвертый выход которого соединен соответственно с тактовыми входами сдвигового регистра, выходы переключателя эквивалентов, соединены с первой группой входов комбинационного сумматора, вторая труппа входов которого соединена с выходами старших разрядов первой тетрады сдвигового регистра, входы младших разрядов накапливающего сумматора соединены с входами младших разрядов преобразователя, вход пуска которого соединен с входом пуска распределителя импульсов, пятый выход которого соединен с входом сброса переключателя эквивалентов Перекл 5 чатель эквивалентов содержит счетчик младших разрядов, cчeYчик старших разрядов, элемент задержки и элемент ИЛИ, первый вход которого через элемент задержки соединен с выходом переполнения счетчика младших разрядов, счетный вход которого является тактовым входом переключателя эквивалентов и соединен с вторым входом элемента ИЛИ, выход которого соединенсо счетным входом счетчика стармшх разрядов, выходысчетчикоб старших и младших разрядов являются выходами переклю чателя эквивалентов, вход сброса которого соединен с входами сброса счетчиков старших и младших разрядов. На фиГо 1 изображена блок-схема преобразователя; на фиг 2 - блоксхема переключателя эквивалентов; на фиг 3 - блок-схема распределителя импульсов о В преобразователь двоично-десятичных чисел в двоичные (фиг. 1) входят накапливающий сумматор 1, соединенный с распределителем 2 импульсов, переключатель 3. эквивалентов, блок хранения эквивалентов, дешифратор 5 нулевого состояНИЯ-, сдвиговый регистр 6 и комбицационный сумматор 1 Младший двоичный разряд младшей тетрады сдвигового регистра 6 подсоединен непосредственно к младшему адресному входу блока k хранения эквивалентов. Уста новленные входы четырех младших раз рядов сумматора 1 непосредственно подсоединены к кодовым входам млад шей тетрады, причем информационные входы 8 старших разрядов преобразов теля соединены с вход|3ми сдвигового регистра 6 Вход пуска преобразователя 9 сое динен с входом пуска распределителя импульсов, выход 10 конца преобразования соединен с выходом распределителя импульсов, а выходы 11 накапливающего сумматора 1 являются выходами преобразователя Переключатель 3 эквивалентов (фиг. 2)содержит последовательно соединенные счетчик 12 младших разрядов, элемент 13 задержки, элемент k или и счетчик 15 старших разря TioBo Входы сброса счетчиков 12 и 15 соединены с входом 1б сброса перекл чателя эквивалентов, счетный вход счетчика 12 и вход элемента ИЛИ соединены с входом 1J, а выходы сче чиков 12 и 15 образуют выходы 18 переключателя 3 эквивалентов о Счетчик, 12 выполнен двухразрядным Распределитель импульсов2 (фиг, содержит RS-триггеры и элементы 22-25 И, 26 задержки и 27 ИЛИ выход элемента И 22 подсоединен к выходам 28-30. Выход элемента 23 И соединен к выходу 31, к гасящему входу триггера 19 и к установочному входу триггера 2},, Выход последнего соединен с первым входом элемента 2k И, выход которого подсоединен к выходам 32-3 и к входу элемента 27 ИЛИ. Выход последнего через элемент 26 задержки подсоединен к первому входу элемента 25 И, второй вход которого соединен с входом 35, а выход подсоединен к выходу 1О и гасящим входам триггеров 20, 21, Вторые выходы элементов 22, 2/4 И по соединены к входу 36, а элемента 23 И - к входу 37. I, , .. ,, При преобразовании п-разрядного . Десятичного числа сдвиговый регистр .6 содержит п-1«тетраду, Тое (п-1) двоичный разряд о. При этом по сигналу сдвига производится сдвиг информации вправо на один десятичный разряд, Таео на четыре двоичных. Для этого выход пятого разряда регистра 1 подсоединен к первому разряду, выход шестого - к второму, выход седьмого - к третьему, выход восьмого к четвертому, выход девятого - к пятому и т.д. Комбинационный сумматор 7 имеет две группы входов, из которых первая группа имеет г+2 разряда, а вторая - только 3 разряда. При этом обеспечивает преобразование чисел при , при , г при .Т4, при п 629 и т,д. Преобразователь работает следующим образом о Сигнал пуска по входу 9 заносит 1 в триггер 19 распределителя импульсов 2, По первому тактовому импульсу Т1, поступившему на вход 36, на выходе элемента 22 И образуется сигнал; который поступает на элемент 27 ИЛИ, заносит 1 в триггер 20 и через выход 28 разрешает занесение преобразуемого десятичного числа (точнее п-1 его старших разрядов) в сдвиговый регистр 6 и разрешает занесение младшей тетрады преобразуемого десятичного числа в накапливающий сумматор 1, через выход 30 и вход 16 гасит счетчики 12 и 15 в переключателе 3 эквивалентов, В результате младшая (первая)тетрада .оказывается в накапливающем сумматоре 1, остальные тетрады преобразуемого десятичного числа - в сдвиговом регистре 6, а содержимое счетчиков 12 и 15 равно О, По первому тактовому импульсу 12, поступившему на вход 37, -на выходе элемента 33 И образуется сигнал, который устанавливает в О триггер . 19, в 1 триггер 21 и через выход 31 разрешает выборку в блоке k хранения эквивалентор очередного экёивалента, При этом в качестве адреса, на его адресные входы поступают код с выхода комбинационного сумматора 7 и содержимое младшего двоичного разряда втррой тетрады преобразуемого десятичного числа. Так как выход переключателя 3 эквивалентов находится в нулевом состоянии, на адресный вход блока 4 подается вторая тетрада преобразуемого числа. Код на его выходе изменится только после подачи следующей команды выборки, По следующему тактовому импульсу Т1 на выходе элемента 2k. И образуется сигнал, который поступает на вход S10j8469 элемента 27 ИЛИ, a также разрешает сложение в накапливающем сумматоре 1, в четырех младших разрядах которого содержится код младшей тетрады преобразуемого десятичного числа, а на остальные входы сумматора 1 подается код двоичного эквивалента второй тетрады с выходов блока k. Сигнал с элемента 2 И через выход 33 разрешает сдвиг в сдвиговом регистре 6, благодаря чему к следующему такту в четырех младших двоичных разрядах последнего оказывается уже третья 16)рада. Сигнал с элемента 2k И через выход 3( и вход 17 поступает на счет- не

1ый ВХОД счетчика 12 и через элемент ИЛИ на счетный вход счетчика 15, е результате чего в переключателе экаиваленгов окажется код 00101 (или 001010 с учетом отсутствующего младшего разряда)а

По следующему тактовому импульсу Т1 вновь срабатывает элемент 23 И и запускает выборку следующего эквивалента в блоке А„ При этом в качестве адреса на его адресные входы поступает сумма кодов третьей тетрады и 1010.

По следуюдему тактовому импульсу Т1 снова осуществляется сложение в накапливающем двоичном сумматоре 1, сдвиг в сдвиговом регистре 6.и прибавление 1 в счетчики 12 и 15 в переключателе 3 эквивалентов. При прибавлении 1 в четвертый раз на выходе счетчика 12 появится импульс, который через элемент 13 задержки и 1 ИЛИ поступит на вход счетчика 15. Таким образом, содержимое переключателя 3 эквивалентов при последопул етс ног

Тогда дешифратор 5 нулевого состояния вырабатывает сигнал, который че|эез вход 35 поступит на второй вход элемента 25 И Как только на его первый вход поступит импульс с выхода элемента 26 задержки (образуется после срабатывания элемента 2 И или 22 и), элемент 25 И сработает так, что силнал с его выхода установит

в О триггеры 20-21 и через выход 10 поступит на выход конца преобразования.

Таким образом, в,предлагаемом преобразователе на преобразование

каждой тетрады необходимо 2 такта, в то время как в прототипе , Предлагаемый преобразователь не тратит лишних тактов на сложение первой тетрады и заканчивает процесс преобразо.вания раньше, если преобразуемое десятичное число оказалось меньше максимального, В результате быстродействие преобразователя больше, чем у-прототипа в 2+2,2/Л раз

при среднестатическом распределении кодов о ательной подаче на вход 17 имьсов меняется следующим образом: 000000 000101 001010 001111 0101 00 011001 011110 1000 11 1010 00 Работа преобразователя продолжая до тех пор, пока после очередо сдвига в сдвиговом регистре 6 окажется во всех разрядах,

Ж

31

Ш

ft

Kn

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU744546A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичнодесятичного кода в двоичный | 1977 |

|

SU656052A1 |

18

It

т

5 г.7

18

U

//2.2

Авторы

Даты

1983-10-15—Публикация

1982-05-04—Подача