(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД Изобретение относится к области .автоматики и вычислительной.техники и может быть использовано для преобразования информации при вводе и выводе из ЭЦВМ.; , Известен преобразователь двоичного кода в двоично-десятичный код, со держащий к.аскады регистров, управляю щие триггеры и вентили. Сущность работы этого преобразователя состоит в том, что исходный код поступает последовательно, начиная со старших ра рядов. Содержимое в отдельных тетрарадах сдвигается влево или вправо в зависимости от наличия или отсутстви переноса из ближайшей тетрады. Напра ление сдвига тетрады единиц зависит от значения .очередного двоичного разряда 1. Недостатком преобразователя является невысокое быстродействие, которое может быть оценено неравенством где tnp - время преобразования; п - разрядность преобразуемого кода; Т - период следования тактбвых импульсов.

. Найбр,лее близким по технической сущности к предложенному является преобразователь двоичного кода в двоично-десятичный код, содержащий дешифратор, двоично-десятичный накапливающий сумматор, входы которого соединены с выходами дииифратора, блок управления, выходы которого соединены с управляющим вхрдом двоично-десятичного йакапливающего сумматора и входом дешифрат(ра {2 . Кроме того, известное устройство .содержит коммутатор и элементы ИЛИ. Сущность работы известного преобразователя состоит в том, что последовательный двоичный код поступает на дешифратор, на выходе которого вырабатывается двоично-десятичный эквивалент двоичного кода. Далее двоично-десятичный эквивалент разряда подекадно суммируется с содержимым двоично-десятичного сумматора. Недостатком такого преобразователя является низкое быстродействие. Цель изобретения - повьоиение быстродействия. Поставленная цель достигается тем, что в преобразователь двоичного кода в двоично-десятичный код, содержащий

дешифратор, двоично-десятичный накапливающий сумматор, входы которого соединены с выходами дешифратора, блок управления, выходы которого : соединены с управляющим входом двоично-десятичного накапливающего сумматора и входом дешифратора,введен п-разрядный сдвигающий регистр, выходы которого соединены со входами дешифратора, а управляющие входы соединены с выходами сброса и сдвига блок управления, причем выход младдаего разряда п-разрядного сдвигающего ре.гистра соединен со входом младшего разряда двоично-десятичного накапливающего сумматора, выходы которого являются выходами устройства.

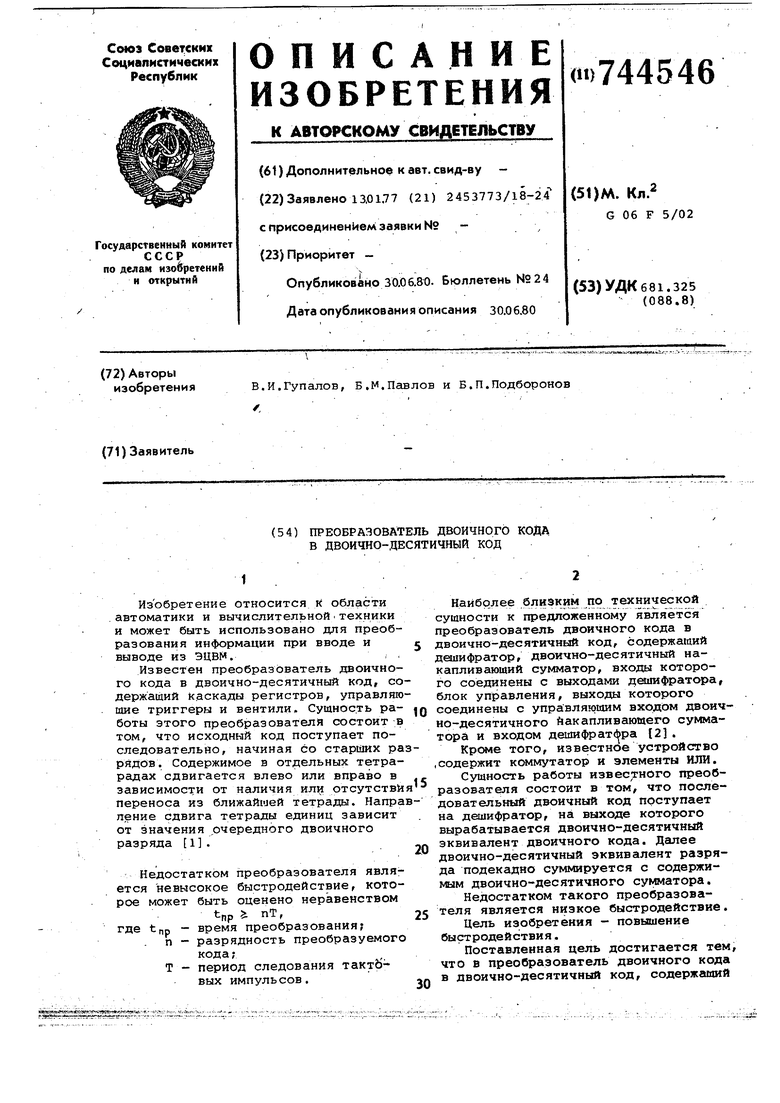

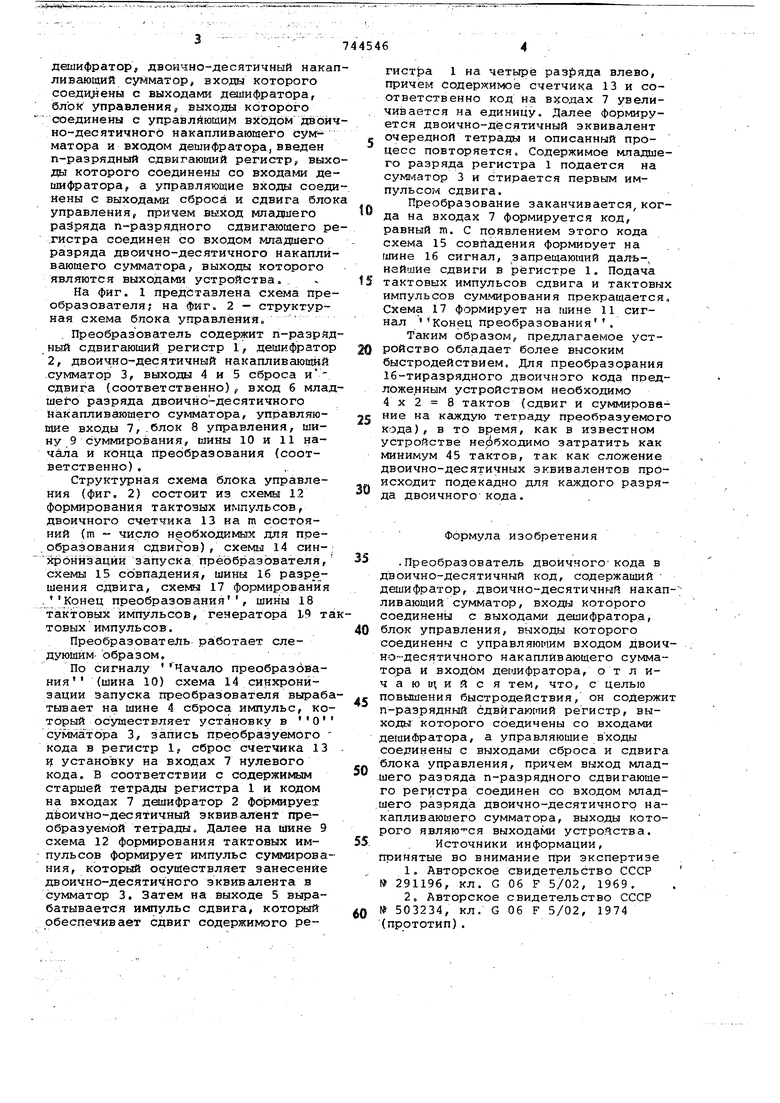

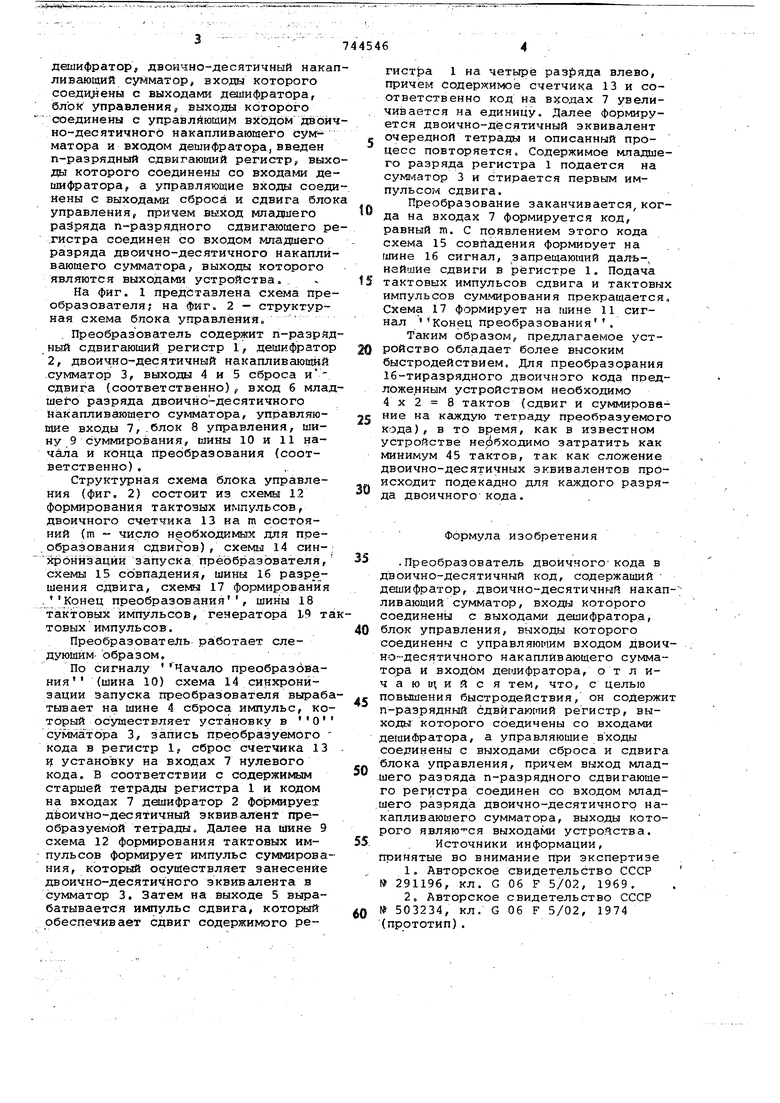

На фиг. 1 представлена схема преобразователя; на фиг, 2 - структурная схема блока управления.

ПреобразЪватель содержит п-разрядный сдвигающий регистр 1, дешифратор 2, двоично-десятичный накапливаюЕций .сумматор 3, выходы 4 и 5 сброса и°сдвига (соответственно), вход 6 младшего разряда двоично-десятичного Накапливающего сумматора, управляющие входы 7,.блок 8 управления, шину 9 суммирования, шины 10 и 11 начала и конца преобразования (соответственно) .,

Структурная схема блока управления (фиг. 2) состоит из схемы 12 формирования тактовых импульсов, двоичного счетчика 13 на га состояний (т - число необходимых д.пя пре.образования сдвигов), схемы 14 синзфбннзацйи запуска преобразователя, схемы 15 совпадения, шины 16 разре шения сдвига, схемы 17 формирования .Конец преобразования , шины 18 та.ктовых импульсов, генератора L9 татовых импульсов.

Преобразователь работает следующим- образом,

По сигналу Начало преобразования (шина 10) схема 14 синхронизации запуска преобразователя вырабатывает на шине 4 сброса импульс, который осуществляет установку в О сумматора 3, запись преобразуемого кода в регистр 1, сброс счетчика 13 И установку на входах 7 нулевого кода. В соответствии с содержимым старшей тетрады регистра 1 и кодом на входах 7 дешифратор 2 формирует дйоично-десятичный эквивалент преобразуемой тетрады Далее на шине 9 схема 12 формирования тактовых импульсов формирует импульс суммирования, который осуществляет занесение двоично-десятичного эквивалента в сумматор 3. Затем на выходе 5 вырабатывается импульс сдвига, который обеспечивает сдвиг содержимого регистра 1 на четыре разряда влево, причем Содержимое счетчика 13 и соответственно код на 7 увели, чивается на единицу. Далее формируется двоично-десятичный эквивалент g очередной тетрады и описанный процесс повторяется. Содержимое младшего разряда регистра 1 подается на сумматор 3 и стирается первым импульс сдвига.

Преобразование заканчивается,когда на входах 7 формируется код, равный т. С появлением этого кода схема 15 совладения формирует на глине 16 сигнал, запрещающий дальнайшие сдвиги в регистре 1. Подача

5 тактовых импульсов сдвига и тактовых импульсов суммирования прекращается, Схема 17 формирует на шине 11 сигнал Конец преобразования .

Таким образом, предлагаемое устройство обладает более высоким

быстродействием. Для преобразования 1б-тиразрядного двоичного кода предложенным устройством необходимо тактов (сдвиг и суммирование на каикдую тетраду преобразуемого кода), в то время, как в известном устройстве нес бходимо затратить как минимум 45 тактов, так как сложение двоично-десятичных эквивалентов происходит подекадно для каждого разряда двоичного кода.

Формула изобретения

.Преобразователь двоичногокода в двоично-десятичный код, содержащий дешифратор, двоично-десятичный накапливающий сумматор, входы которого соединены с выходами дешифратора,

блок управления, выходы которого

соединены с управляющим входом двоично-десятичного накапливающего сумматора и входЬм дешифратора, от л ичающийс я тем, что, с целью

повышения быстродействия, он содержит п-разрядный сдвигающий регистр, выходы которого соединены со входами дешифратора, а управляющие входы соединены с выходами сброса и сдвига блока управления, причем выход младшего разряда п-разрядного сдвигающего регистра соединен со входом младшего разряда двоично-десятичного накапливающего сумматора, выходы которого являю- ся выходами устройства.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 291196, кл. G 06 Р 5/02, 1969.

2.Авторское свидетельство СССР № 503234, кл. G 06 F 5/02, 1974

(прототип).

.IJiUiUl

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоичнодесятичного кода в двоичный | 1977 |

|

SU656052A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

Фиг. г

Авторы

Даты

1980-06-30—Публикация

1977-01-13—Подача