ливающего сумматора, информацяонйые входы которого соединены с первыми входами комбинационного сумматора/ выходы которого соединены с информационными входами регистра, а вторые входы комбинационного сумматора соединены с выходами выходного регистра, входы старижх разрядов которого соединены с выходами элементов И группы, кроме первого и второго элементов И группы, выходы которых соединены соответственно с первыми входами второго и третьего элементов ИЛИ, вторые входы которых соединены соотвественно с выходами первого и второго элементов И, выходы второго и третьего элементов ИЛИ соединены соответственно с входами .nejiвого и второго разрядов выходного . регистра, вход разрешения записи которого соединен с выходом первого элемента ИЛИ.

3. Преобразователь по п.пп.1 и 2, отличающийся тем, что в нем блок управления содержит четыре триггера,четыре элемента И,элемент ИЛИ и элемент задержки, вход которого соединен d выходом первого элемента И,которы является выходом окончания преобразования блока управления и соединен с R -входами первого и второго триггеров, выходы которых соединены соответственно с первыми входами второго и третьего элементов И, выходы которых соответственно являются выходом сдвига и передачи и выходом разрешения записи блока управления, выход второго элемента И соединен с первым входом элемента ИЛИ, выход которого является выходом считывания |блока управления, вход пуска которото соединен с 5- входом третьего триггера, Я-гвход которого соединен с выходом третьего элемента И и S-входом первого триггера, второй вход элемвн-та ИЛИ соединен с выходом четвертого элемента И, выход которого явля-г ется выходс 4 сброса и занесения блока управления и соединен с S-входами второго и четвертоготриггеров, первые входы первого, второго и четвертого элементов И являются соответственно первым, вторым и третьим тактовыми входами блока управления, вторые входы первого, второго и чет- вертого элементов И соединены соответственно с выходом четвертого триггера, третьим тактовым входом блока управления и выходом третьего триггера, выход элемента задержки соединен с R-входом четвертого триггера, третий вход первого элемента И является входом окончания преобразования блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU744546A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU922723A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

1. ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ, содержаьщй сдвиговый регистр, входы которого соединены с {|1-3)-мя старшими разрядами информационных входоз преобразователя, где п - число разрядов входного кода, двоичнодесятичвилй накапливающий сумматор, выходы которого являются йнФорма ционными выходами преобразователя, блок управления, вход пуска которого является входом пуска преобразр --: . вателя, а выход окончания преобразОтвания является выходом окончания ; преобразования преобразователя, :счетчик, вход сброса которого сое;динен с выходом Сброса и зане сения блока управления и с входами занесения сдвигового регистра и c6pot са двоичйо-десятичиого накапливающего сумматора, блок хранения эквиг валентов, управляющий вход которог о соединён с.выходом считываниялбло1с9 у яравления, выход сдвига и передачи которого соединен со счетным входом счетчика, выходы блока хранения эквивалентов соединены с информациЬй-.. НЕлми входами двоично-десятичного накапливаю1цего сумматора, .о т л И-г чающийся тем, что, с целью повышения быстродействия в него введен дешифратор нуля, входы которого соединены с первой группой выхо;дов сдвигового регистра, а выход дешифратора нуля соединен с-входом -окончания преобразования блока управления, выход сдвига и передачи ко-. ;торого соединен с входом сдвига сдвигового регистра и входом передачи двоично-десятичного накапливающего сумматора, установочные входы которого соединены с младшими разрядами информационных входов преобразователя, вторая группа выходов сдвигового регистра соединена с входами младших разрядов блока хранения эквивалентов , входы старших разрядов которого соединены с выходами счетчика, вход разрешения записи двоично-десятичного накапливающего сумi матора соединен с выходом разрешения записи блока управления, первый (Л второй и третий тактовые входы которого являются соответственно пвуьым, вторым и третьим тактовыми входами преобразователя. 2. Преобразователь по п.1, о тличающийся тем, что в нем двоично-десятичный накапливающий сумматор содержит комбинационный сумматрр,- регистр, выходной регистр, .группу элеьлентов И, триггер, три эле мента ИЛИ и два элемента И, первые ;входы которых соединены с входом .сброса двоично-десятичного накапливающего сумматора, с синхровходом .триггера и первым входам первого .Элемента ИЛИ, второй вход .которого соединен с входом передачи двоичнодесятичного накапливающего суммато,ра и первым входом элементов И груп-, пы, вторые входы которых соединены ic выходами регистра,управляющий вход которого является входом разрешения записи двоично-десятичного накапливающего сумматора,установочные входы которого соединены с вторыми входами элементов И и управляющим входом триггера, выход которого совместно , с выходами выходного регистра являются выходакш двоично-десятичного накгиг

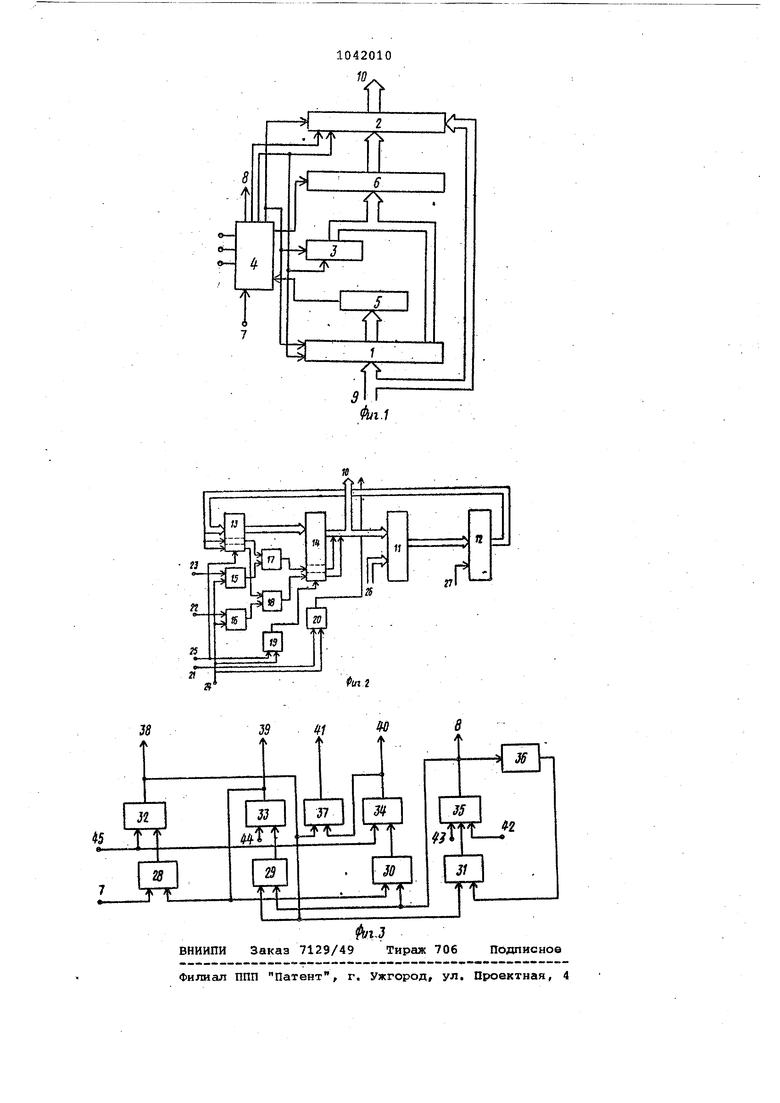

Изобретение относится к области автоматики и цифровой вычислительной техники и может быть использова но в устройствах, работающих в кода с различными системами счисления. Известен преобразователь кодов, содержащий формирователь признаков поразрядных цифр, параллельные двоично-десятичные декадные сумматоры, регистр промежуточных сумм, генератор тактовых импульсов, распределитель , формирователь сигналов запнси и выходной регистр l. Недостаток известного устройства состоит Б малом быстродействии. Наиболее близким к предлагаемому по технической сущности и схемному построению является преобразователь двоичного кода в двоично-десятичный, содержащий сдвиговый регистр, двоично-десятичный накапливающий сумматор, блок управления, счетчик и блок хранения эквивалентов 2 . Недрстаток известного преобразователя состоит в относительно низко быстродействии при преобразовании кодов переменной длины, что связано с обрае}откой максимального числа ра рядов входного кода (в том числе и незначащиЦ. Цель изобретения - повьшение быстродействия. Поставленная цель достигается тем, что в преобразователь двоичного кода в двоично-десятичный, содержащий сдвиговый регистр, входы которого соединены с (ц -3)-мя старипми разрядами информационных входов преобразователя, где h - число разря1 дов входного кода, двоично-десятич.ный накапливающий сумматор, выходы которого являются информационными 1ВыхЬдами преобразователя, блок управ ления, вход пуска которого является входом пуска преобразователя, а выход окончания преобразования является выходом окончания преобразования преобразователя, счетчик, вход сброса которого соединен с выходом сброса и занесения блока управления и с входами занесения сдвигового регистра и сброса двоично-десятичного накапливающего сумматора, блок хранения эквивалентов, управляющий вход которого соединен с выходом считывания блока управления, выхоД сдвига И передачи которого соединен со сче ным входом счетчика, выходы блока х нения эквивалентов соединены с инфо мационными входами двоично-десятичй го накапливающего сумматора, дополнительно введен дешифратор нуля, входы которого соединены с первой группой выхЬдов сдвигового регистра, а выход дешифратора нуля соединен с входом окончания преобразования блока управления, выход сдвига и передачи которого соединён с входом сдвига сдвигового регистра и вхо дом передачи двоично-десятичного накапливающего сумматора, установочные входы которого соединены с младшими разрядами информационных BxojtO преобразователя, вторая группа выхо. дов сдвигового регистра соединена с входами младших разрядов блока хранения эквивалентов, входы старших разрядов которого соединены с выходгмп счетчика, вход разрешения заг писи двоично-десятичного накапливающего сумь4атора соединен с выходом разрешения записи блока управления, первый, второй и третий тактовые вхо ды которого являются соответственно первым, вторьш и Уретъюл тактовш4И входами преобразователя. В преобразователе двоично-деся:тичный накапливакяций сумматор содержит комбинационный сумматор, ре гис, выходной регистр, группу,элементов И, триггер, три элемента ИЛИ и два элемента И, первые входы которых соединены с входом сброса двоично-десятичного накапливающего сумматора, с синхровходом триггера и: первым входом первого элемента ИЛИ, второй вход которого соединен с входом передачи двоично-десятичного накапливающего сумматора и первым входом элементов И.групгел, вторые входы которых соединены с выходами регистра, управляющий вход которого является входом разрешения записи двоично-десятичного накапливающего сумматора, установочные входы ко торого соединены с вторыми входами элементов И и управляющш4 входсж. триггера, выход которого совместно с выходами выходного регистра являются йосодами двоич но-десятичногонакапливающего сукохатора, ин1фО1 1ационные входы которого соединены с первыми входами кснмбинационного сумматора, выхЬды которого соединены с информационными входами регистра а вторые входы комбинационного сумматора соединены с выходами выходного регистра, входы старших разрядов хо торого соедииены с выходами элементов И группы, кроме первого и вто рого элементов И группы, выходы кото рых аоединены соответственно с первы ми входами второго и третьего эл&лея тов ИЛИ, вторые входы которых соединены соответственно с выходами пер вого и второго элементов И, выходы второго и третьего- элементов ИЛИ соединены соответств.енно с входами первого и второго разрядов выходного регистра, вход разрешения записи которого соединен с выходом первого элем(ента ИЛИ. Блок управления содержит четыре триггера, четыре элемента И, элемент ИЛИ и элемент задержки, вход которо- го соединен с выходом первого элемента И, который является выходом окончания преобразования блока управления и соединен - с R-входами первого и второго триггеров, выходы которялх соединены соответственно с первыми входами второго и третьего элементов И, выходы которых соответственно являются выходом сдвига и передачи и выходом разрешения записи блока управления, выход второго элемента И соединен с первым входом элемента ИЛИ, выход которого является выходом считывания блока управления,, вход пуска которого соединен с S-входом третьего триггера, R-вход которого соединен с выходом третьего элемента И и 8-входс 1 первого триггера, второй вход элемента ИЛИ соединен с выходом четвертого элемента И, выход которого является выходом сброса и занесения блока управления и соединен с S-входами второго и четвертого триггеров, первые входы первого, второго и четвертого эле-ментов И являются соответственно первым, вторым и третьим тактовыми входами блока управления, вторые входы первого, второго и четвертого элементов И соединены соответственно с выходом четвертого триггера, третьим тактовым входом блока управления и выходом третьего триггера, выход элемента задержки соединен с R-BXOдом четвертого триггера, третий вход первого элемента И является входом окончания преобразования блока управления. На фиг.1 представлена блок-схема преобразователяJ на фиг.2 - структурная схема двоично-десятичного накапливающего сумматора{ на фиг.З (структурная схема блока управления. в состав преобразователя (фиг.1) .входят сдвиговый регистр 1 на П 3 двоичных разряда, двоич но-десятич-: ный накапливакидий сумматор 2, счетчик 3, блок 4 управления, дешифратор нуля 5 и блок б хранения эквивалентов. Входы блока 4 управления сое-, динены с входом 7 пуска и выходом дешифратора нуля 5, а его выхода с выходом 8 конца преобразования, входами сдвигового регистра 1,i двоично-десятичного накапливающего сумматора 2 и счетчика 3, а также с i управляющим входом блока хранения эквивалентов. Входы старших разрядов

адреса послелнего соединены с выхсГдами к младших разрядов сдвигового регистра 1, а выходы всех П -3 разрядов которого соединены в содами с дешифратора 5, а входы - с п-З старошми кодовыми входами преобразователя, причем три младших кодо-, вых входа последнего подсоединены непосредственно к установочным входам TJsex младших разрядов двоичнодесятичного на-капливающего сумматора 2. При этом П-З стагл1тх.,и три младших кодовых входа образуют 17-разрядные кодовые входы 9 преобразователя, а выходы сумматора 2 - выходы10 преобразователя.

Сдвиговый регистр 1 осуществляет сдвиг на k разрядов за один такт, для чего, например, при k 3 вы- . ход k +1 разряда соединен с входом 1-го разряда, внрсод k 4-.2 разряда - с входом 2-го, выход k +3 разряда с входом 3-го, выходk+4 разряда с входом k +1 и т.д. Счетчик 3 дол-жен обеспечивать двоичивлй счет до величины р -1, где - больше или рав-, Ho.vi -3) /ic (величина целая), так что объем блока 6 хранения эквивалентов составляет : 2 слов юв соответствующей разрядности.

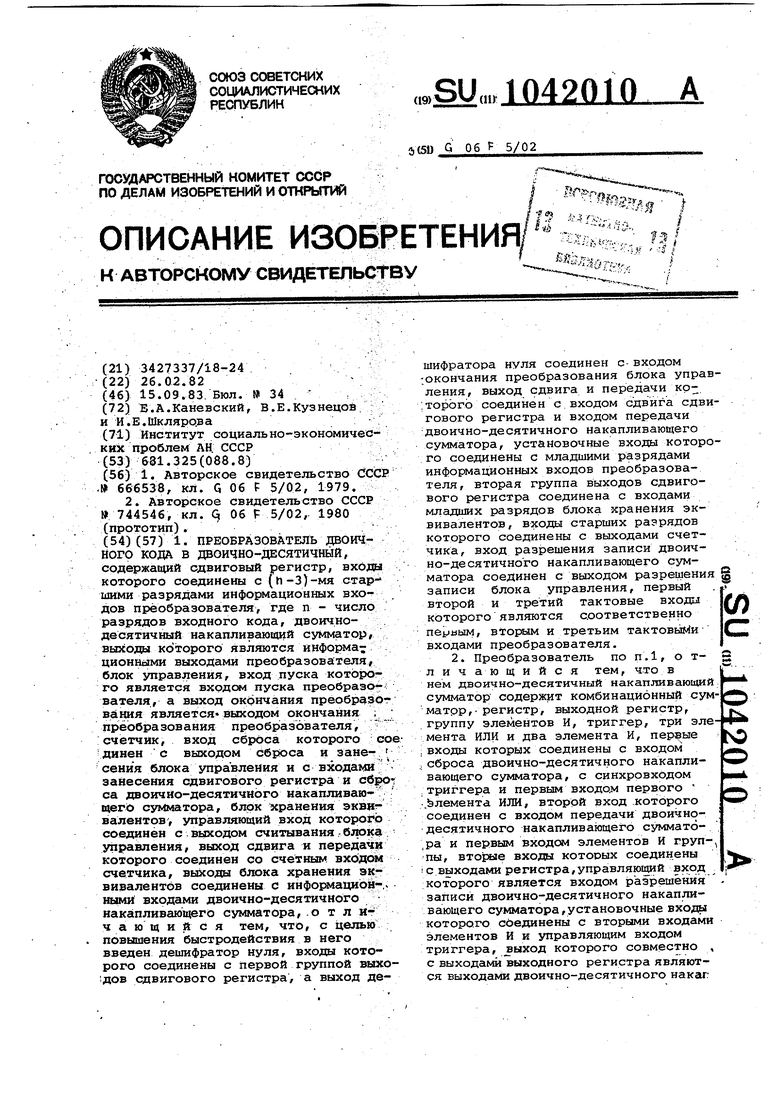

В состав двоично-десятичного накапливающего сумматора (фиг.2) вх дят последовательно соединенные комбинационный сумматор 11, выходной регистр 12, группа 13 элементов И и выходной регистр 14, а также элемент 15, 16 И, 17-19. ИЛИ и триггер 20. Последний является Dr-триггером} пус для определенности регистры 12, 14 также используют триггеры этого типа. Входы 21-23 ЯВЛЯ10ТСЯ установочными для занесения 1-го, 2-го и 3-го младших разрядов соответственно и подсоединены к D-входу триггера 20 и первым входам элементов 16 и 15 И, причем их вторые входы, первый вход элемента 19 ИЛИ и синхр вход триггера 20 подсоединены к входу 24 сброса. Вход 25 передачи соединен с входами группы 13 элементов И и вторым входом элемента 19 ИЛИ Если максимальное десятичное число после преобразования должно выражаться .т двоичными разрядами, то разрядность сумматора 11, регистров 12, 14 и группы 13 элементов И есть m -1, причем выходы регистра 1 и триггера 20 образуют выходы 10 преобразователя, а вторые входы двоично-десятичного комбинационного сумматора 2 являются входами 26 двоично-десятичшэ о накапливающего сумматора 2. При этом выходы двух младших разрядов группы 13 элементов И подсоединены к первым входам элементов 17, 18 ИЛИ соответственно, вторые входы которых подсоединены к выходам элементов 15, 16 И,

а их выходы - к входам двух младших разрядов регистра 14, вход занесения которого соединен-с выходом элемента 19 ИЛИ {этот вход эанеге ния соответствует синхровходу триггеров) . Вход 27 разрешения записи сложения подсоединен к входу занесения регистра 12.

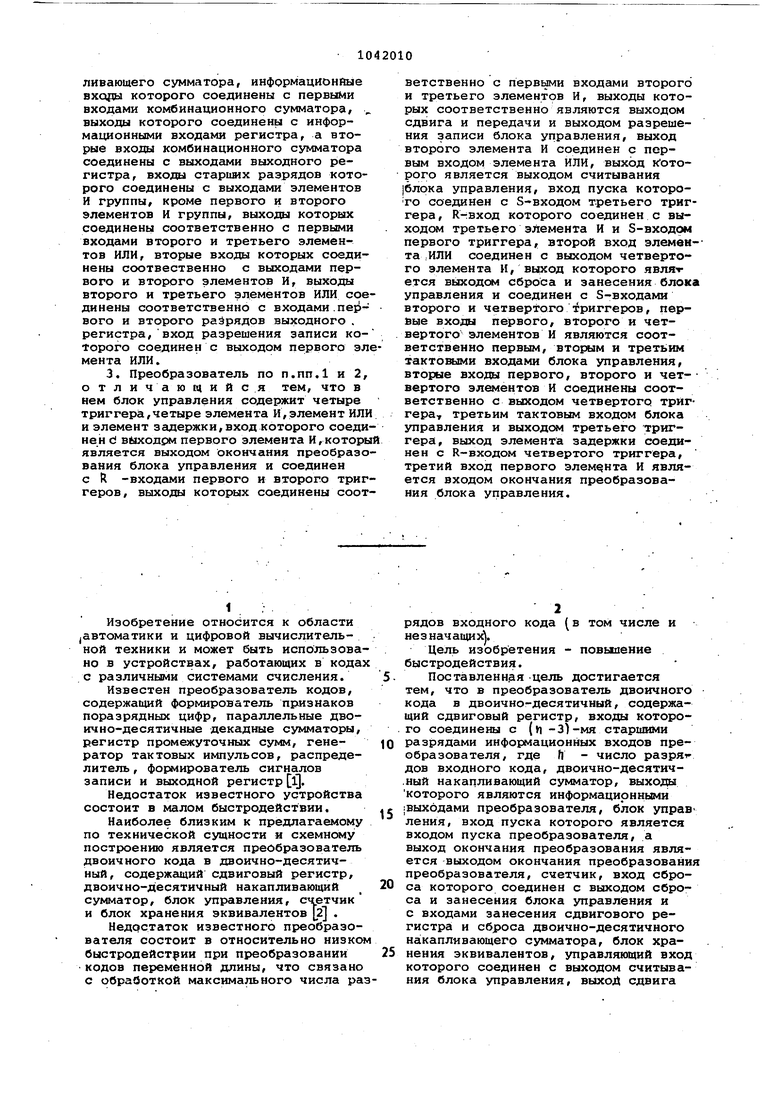

Блок управления (фиг.3)састоит из триггеров 28-31 и элементов 32-35 И, элемент. 36 задержки, элемент .37 ИЛИ, Выходы 38-41 являются соответственно выходом сброса и занесения выходом разрешения записи, выходом считывания, выходом сдвига и передачи. Вход 42 окончания преобразования соединен с входом элемента и 35. Входы 43-45 являются первым, вторым и.третьим тактовыми входами блока управления.

Рассмотрим подробнее работу предлагаемого преобразователя, например при m -16, И -14 и k 3 (максимальное преобразованное, десятичное число есть. 9999J. После того, как да входах 9 выставлен преобразуемый : код, .на вход 7 поступит сигнал НачалоЛ преобразования, по которому триггер 28 установится 13 I

первый тактовый импульс Т1у постпивший на вход 45, откроет элемент 32 И, так что образующийся на Выходе последнего импульс по выходу 38 установит в О счетчик 3 /(своим передним фронто, обеспечит занесение в сдвиговый регистр 1 содержимого одиннадцати старших разрядов преобразуемого кода (разряды 4-14)у и поступит на вход 24 сброса двоичндесятичного накапливающего суммато ра 2.

В результате на выходе элемента 19 ИЛИ (см. фиг.2) образуется импульс, который поступает на вход регистра 14 и разрешает занесение в него кода. Так.как группа 13 элементов И , то в 12 старших разрядов регистра 14 занесется О, а три младшие разряда преобразуемого кода занесутся соответственно: третий разряд кода по цепи, вход 23 элемент 15 И элемент 17 ИЛИ второй разряд регистра 14 второй разряд кода по цепи вход 22 - эле.. мент 16 И - элемент liB ИЛИ - перт .вый (младошй) разряд |регистра 14, первый разряд кода по цепи, вход 21 триггер 20

Кроме того, импульс с. выхода элемента 32 И (см.фиг.З) устанавливает в 1 триггеры 29, 31 и через элемент 37 ИЛИ и выход 10 задним фронтом обеспечивает считывания из блока хранения 6 эквивалентов, на выходе которого выбранный код фиксируется до следующего тактового импульса Т1 (см-, фиг.1) . Так как к этому моменту времени содержимое счетчика 3 равно О, а в .трех младаа разрядах сдвитового регистра 1 соде жится .часть преобразуемого кода (че вертый - шестой разряды), то на выходе блока 6 выбран код хранящийся в нем по адресу, представляющему собой содержимое этих трех разрядов регистра 1. Этот код является Двоич но-десятичным эквивалентом трех раз рядов преобразуемого кода.. Первый тактовый импульс Т2 по вй ходу 44 откроет элемент 33 И .(см, . фиг.З), так что образующийся на Выходе последнего импульс установит в О триггер 28 и в 1 триггер 30 а также .через выход 39 и вход 27 поступит на вход регистра 12 (см. .фиг.2). Так как на вхоДы комбинацио ного сумматора 11 с момента окончания тактового импульса Т1 noctyndют код второго и третьего младшихразр;1дов преобразуемого кода из IH&гистра 14 и код эквивсшента из $лрка 6, то .по окончании тактового: импульса Т2 в регистре12 окажется их двоично-десятичная сумма. Самый младший разряд преобразуемо го кода (первый) хранится в триггё ре 20 и в njpouecce преобразования н изменяется. . При поступлении на вход 45 втОро го тактового импульса Т1 открывается элемент 34 И, так что образую-; щийся на его выходе 41 импульс обес печит сдвиг на три разряда .вправо Гцо переднему фронту), в. сдвиговом регист е 1, занесет 1 в счетчик 3 по своему переднему фронту); и поступит на вход 25 двоично-десятичного накап ливающего сумматора 2. В результате на выходе элемента 19 ИЛИ образуется импульс, который разрешит занесение кода в регистр 14. Так как группа 13 элементов И открыта, то содержимое регистра 12 передастся в регистр 14, причем оба младших разряда передаются по элементам 17, 18 ИЛИ соответственно. Кроме того, импульс с выхода элемента 34 И чере элемент 37 ИЛИ своим задним фронтом обеспечивает считывание из блока 6 хранения эквивалентов. Так как к этому моменту времени содержимое счетчика 3 равно 1, а в трех млгщших разрядах сдвигового регистра 1 содержится седьмой - девятый разряды преобразуемого кода, то на выходе блока 6 хранения эквивалентов выбран код, хранящийся по адресу,, представляющему собой сумму двух ко.дов, один из которых есть 1000, а I второй - содержимое трех младших раз рядов регистра 1; При поступлении на вход 44 второго тактового импульса Т2 блок 4 управления и двоично-десятичный накапливающий сумматор 2 работают так же, как указано. Прн поступлении на вход 45 следующего тактового импульса Т1 блоки и узлы преобразователя работают аналогично предыдущему, причем в этом случае на выход блока 6 хранения эквивалентов выбран код, хранящийся по адресу, представляющему сумму кода 10000 и содержимого трех младших разрядов сдвигового регистра 1, т.е. десятого - двенадцатого разряда преобразуемого кода. По следующему тактовому импульсу Т1 адрес для блока б представляет сумму кода 11000 и нового содержимого трех младших разрядов регистра 1 и т.д. Так продолжается до тех пор, йока после очередного сдвига регистр 1 не окажется в нулевом состоянии.Тогда сработает дешифратор 5 и сигнал с его выхода поступит на вход 42 блока управления. При поступлении на вход 43 тактового импульса Т1 элемент И 35 сработает, импульс с его выхода установит в О триггеры 29, 30 и через элемент 36 задержки установит в О триггер 31.. В результате на выходе элемента 35 И формируется сигнал Конец преобразования, который поступает на выход 8. Его длительность определяется величиной задержки элемента 36 (но не более периода тактового импульса Т1). Таким образом, предлагаемое устройство осуществляет преобразование двоичного кода в двоично-десятичный за 2р тактов, где р - целая величина большая или ра.вная (h-3)/k , причем п - в данном случае - это разрядность данного преобразуемого кода. Если известному преобразователю требуется 2 тактов, где 8 есть целая величина; большаяГ или равная()./и, причем ,- это разрядность максимально большого преобразуемого кода, то в большинстве случаев предлагаемое устройство эаканчи.вает процесс преобразования раньше прототипа, так как в подавляющем большинстве случаев раз рядность преобразуекых кодов меньше максимально допустимой. Если взять среднестатистическое распределение кодов, то и тогда имеет место повыиение быстродействия.Так, например,при k 4 и п 21 быстродействие повышается на 4,8%, при It « 20 па 10,6%, приП 19 на 21,3% Л при ,п 18 на 22,7%.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР | |||

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU666538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU744546A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1983-09-15—Публикация

1982-02-26—Подача