Известны устройства для коммутаторов с разделенной нагрузкой, выполненных в виде матрицы Адамара, каждый вход которых состоит из пары обмоток с присоединенной к ним парой однополярных формирователей тока.

Предложенное устройство отличается от известных тем, что оно содерл ит трансформатор, число первичных обмоток которого, намотанных в одном направлении, равно числу Первичных обмоток, намотанных в другом направлении, при этом первичные обмотки включены между формирователями тока и входом коммутатора так, что две обмотки, подключенные к одному входу коммутатора, намотаны в одном направлении. Это нозволяет обнаружить ошибки входных цепей коммутатора.

Кроме того, устройство отличается от известных тем, что в нем выходные обмотки п трансформаторов подключены к схеме «ИЛИ. Это позволяет обнаружить ошибки входных цепей коммутатора с большим числом входов.

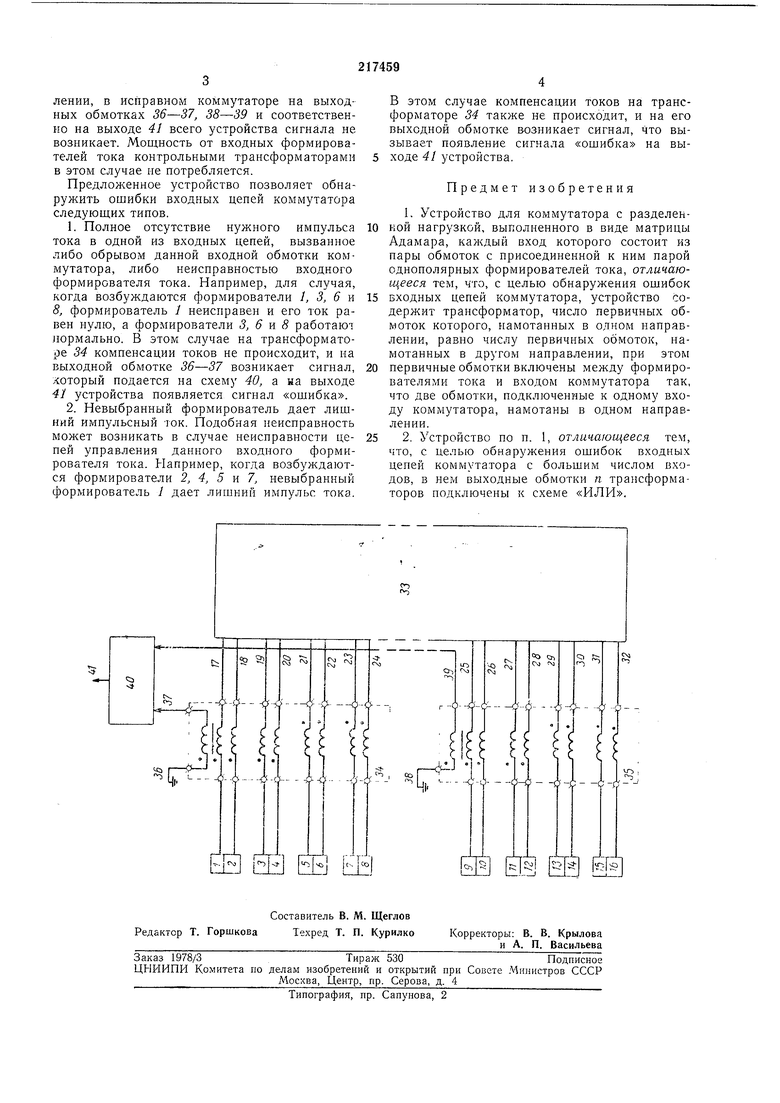

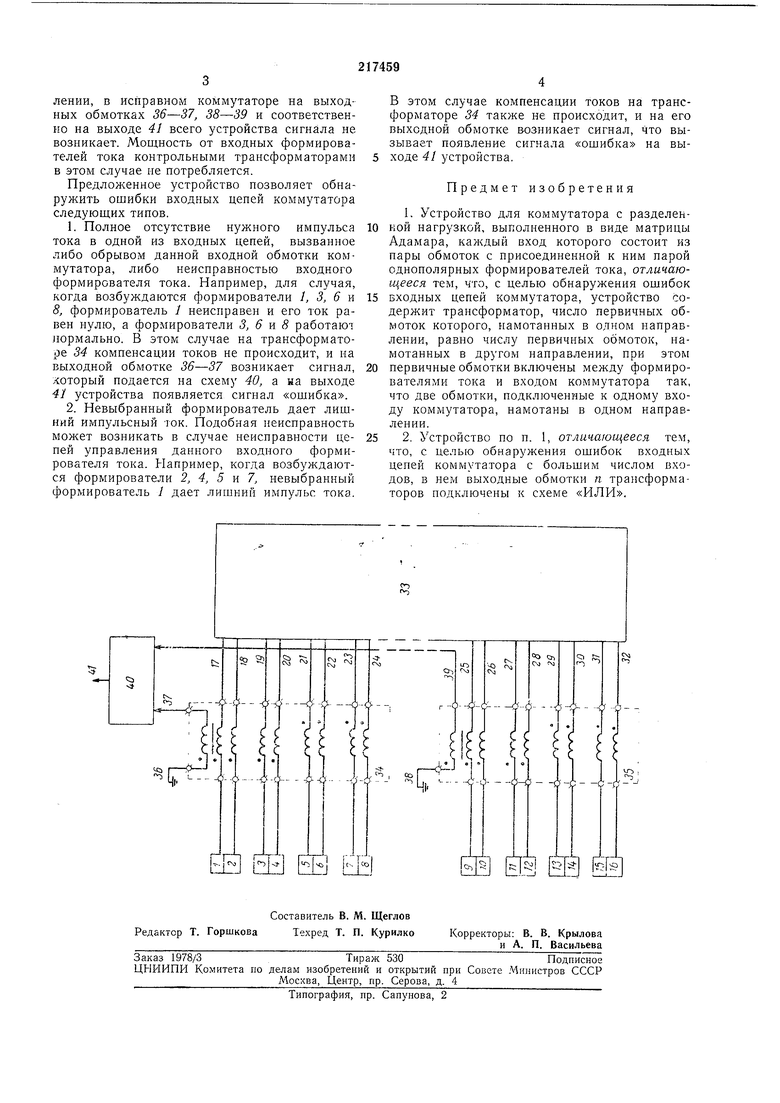

На чертел е изобралсена принципиальная схема предложенного устройства.

ные трансформаторы 34 и 35 включены во входные цепи между формирователями тока и коммутатором. Каждый контрольный трансформатор в данном случае объединяет четыре пары входных формирователей (может быть объединение любого четного числа пар входных формирователей). Точками условно обозначено направление прошивки сердечника трансформатора соответствующей обмоткой. Выходные обмотки 36 и 37, 38 и 39 контрольных трансформаторов объединяются на логической двухполярной схеме «ИЛИ 40, выход которой 41 является выходом устройства обнаружения ошибок.

В рабочем состоянии в исправном коммутаторе с разделенной нагрузкой, реализующем стандартную матрицу Адамара, каждый вход которого состоит из пары обмоток с присоединенной к ним парой однополярных формирователей тока, один из каждой пары, входных формирователей (/-2, 3-4 и т. д.), соотвегствующий одному входу коммутатора, всегда возбуждается. Поэтому по одному из проводов каждой пары входных обмоток коммутатора 17-18, 19-20 и т. д. всегда протекают равные импульсные токи. Поскольку на каждом контрольном трансформаторе число пар входных обмоток, прошивающих его в одном направлении, равно числу пар входных обмоток, прошивающих его в другом направлении, в исправном коммутаторе на выходных обмотках 36-37, 38-39 и соответственно на выходе 41 всего устройства сигнала не возникает. Мощность от входных формирователей тока контрольными трансформаторами в этом случае не нотребляется.

Предложенное устройство нозволяет обнаружить ошибки входных ценей коммутатора следующих типов.

1.Полное отсутствие нужного импульса тока в одной из входных цепей, вызванное либо обрывом данной входной обмотки коммутатора, либо неисправностью входного формирователя тока. Например, для случая, когда возбуждаются формирователи 1, 3, 6 w 8, формирователь 1 неисправен и его ток равен нулю, а формирователи 3, 6 и 8 работают нормально. В этом случае на трансформаторе 34 компенсации токов не происходит, и на выходной обмотке 36-37 возникает сигнал, хоторый подается на схему 40, а на выходе устройства появляется сигнал «ошибка.

2.Невыбранный формирователь дает лишний импульсный ток. Подобная ненсправность может возникать в случае неисправности цепей управления данного входного формирователя тока. Например, когда возбуждаются формирователи 2, 4, 5 и 7, невыбранный формирователь У дает лишний импульс тока.

В этом случае компенсации токов на трансформаторе 34 также не происходит, и на его выходной обмотке возникает сигнал, что вызывает появление сигнала «ошибка на выходе 41 устройства.

Предмет изобретения

1. Устройство для коммутатора с разделенкой нагрузкой, выполненного в виде матрицы Адамара, каждый вход которого состоит из пары обмоток с присоединенной к ним парой однополярных формирователей тока, отличающееся тем, что, с целью обнаружения ошибок

входных ценей коммутатора, устройство содержит трансформатор, число первичных обмоток которого, намотанных в одном направлении, равно числу первичных обмоток, намотанных в другом нанравлении, при этом

первичные обмотки включены между формирователями тока и входом коммутатора так, что две обмотки, подключенные к одному входу коммутатора, намотаны в одном нанравленнн.

2. Устройство по н. 1, отличающееся тем, что, с целью обнаружения ошибок входных ценей коммутатора с большим числом входов, в нем выходные обмотки п трансформаторов подключены к схеме «ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕШИФРАТОР | 1972 |

|

SU424314A1 |

| ПЕРЕКЛЮЧАТЕЛЬ НА ОСНОВЕ МАТРИЦ АДАМАРА | 1972 |

|

SU330541A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| Устройство для контроля коммутатора сигналов постоянного тока | 1984 |

|

SU1231625A1 |

| СПОСОБ ПОДАВЛЕНИЯ ПЕРЕКРЕСТНЫХ ПОМЕХ В МНОГОПРОВОДНЫХ ЛИНИЯХ СВЯЗИ | 2014 |

|

RU2579915C2 |

| Матричный магнитный переключатель | 1976 |

|

SU635511A1 |

| Импульсный дешифратор | 1976 |

|

SU813784A1 |

| МНОГОКАНАЛЬНЫЙ ИМПУЛЬСНЫЙ ИСТОЧНИК ЭЛЕКТРОПИТАНИЯ | 2024 |

|

RU2838912C1 |

| Постоянное запоминающее устройство трансформаторного типа | 1972 |

|

SU576610A1 |

| Трансформаторное постоянное запоминающее устройство | 1977 |

|

SU733027A1 |

Даты

1968-01-01—Публикация