I

Изобретение относится к области запоминающих устройств..

Известны запоминающие устройства с исправлением ошибок при считывании информации, содержащие блок контроля достоверности информации, соединенный с блоком управления, и оперативный накопитель, подключенный через блок воспроизведения и блок контроля досюверности информации к регистру числа, выполненному на триггерах со счетным входом {.

В этом устройстве информация хранится в виде кода с исправлением ошибок, содержашего информационные и контрольны:е разряды. После считывания слова блок контроля достоверности информации образует из информационных разрядов контрольные и сравннвает их с хранимыми контрольными разрядами; в случае неравенства образованных и хранимых конг трольных разрядов блок контроля достоверности информации вырабатывает сигнал коррекции, который переводит соответствующий трйггер регистра числа в противоположное состояние.

Однако известное устройство требует выполнения ряда логических операций нйд информационными и контрольными разрядами хранимой информации, что усложняет его.

Наиболее близким по технической сущности к изобретению является запоминающее устройство с исправлением ощибок при считывании информации, содержащее регистр числа, разделенный на группы, накопитель, входы которого подключены к выходам формирователей записи и адресного блока, усилители считйвання, кодирующий блок с входным регистром, блок образования контрольного крда, дешифратор адреса неисправности, блок исправления ощибок, выходной регистр (2J.

В этом устройстве к числу, принятому на регистр, с помощью ко.аирующего блока добавляются избыточные, проверочные разряды кода Хэмминга, после считывания хранимой в коде Хэммннга информации декодирующий блок из информационной частн слова снова образует проверочные разряды; считанные и вновь образованные прове{ючные разряды сравниваются блоком образования контрольного кода; полученный в результате сравнения код ощнбки подается на вход дещифратора адреса неисправности, который дает сигнал на выходно й щине с тем же номером, который имеет неисправный разряд, в блоке исправления ощибкн проводится инверсия информации в неисправном разряде, и скорректированная информация устанавливается на выходном регистре.

Однако это устройство, как и предыдущее, требует выполнения ряда логических операций над записываемой и считываемой информацией и содержит в связи с этим ряд сложных логических блоков, что усложняет устройство и снижает его быстродействие.

Целью изобретения является упрощение и повышение быстродействия устройства.

Это достигается тем, что предлагаемое устройство содержит дещифраторы,, щифраторы и входные и выходные комбинаторные переключатели по числу групп регистра числа, входы дешифратора подключены к соответствующим выходам регистра числа, а выходы - ко входам входных комбинаторных переключателей, выходы которых соединены со входами формирователей записи, входы выходных комбинаторных переключателей соединены с выходами накопителя, а выходы - со входами усилителей считывания, выходы которых подключены ко входам соответствующих шифраторов.

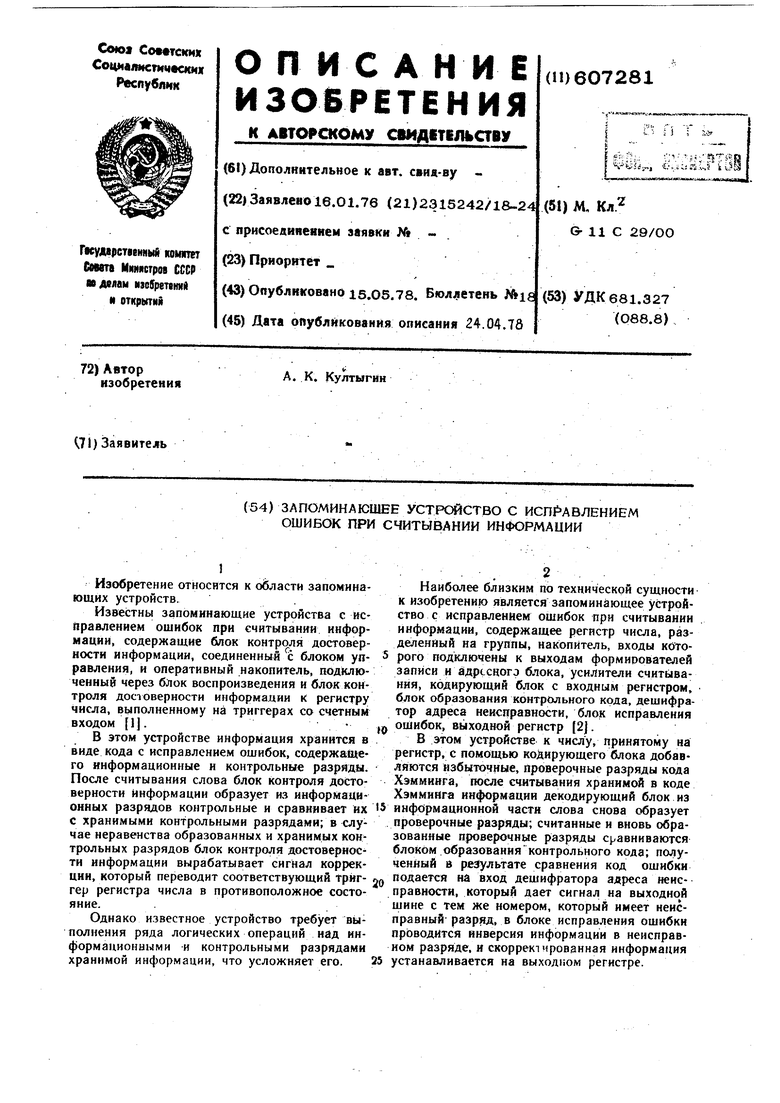

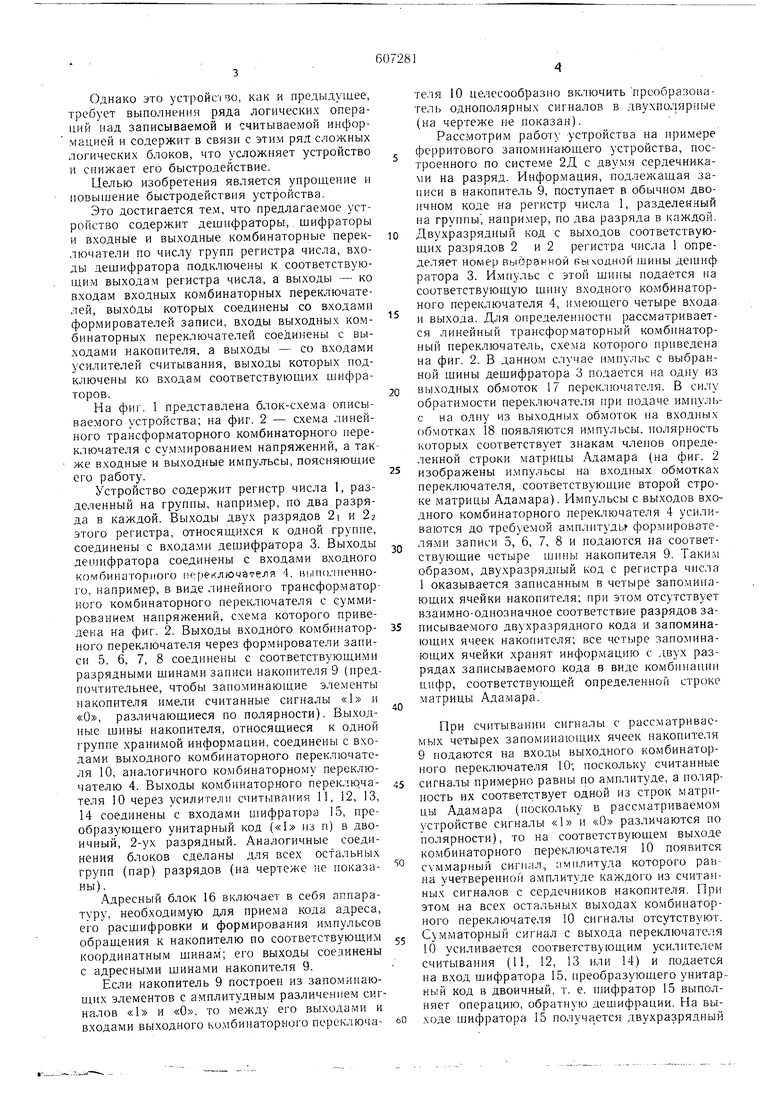

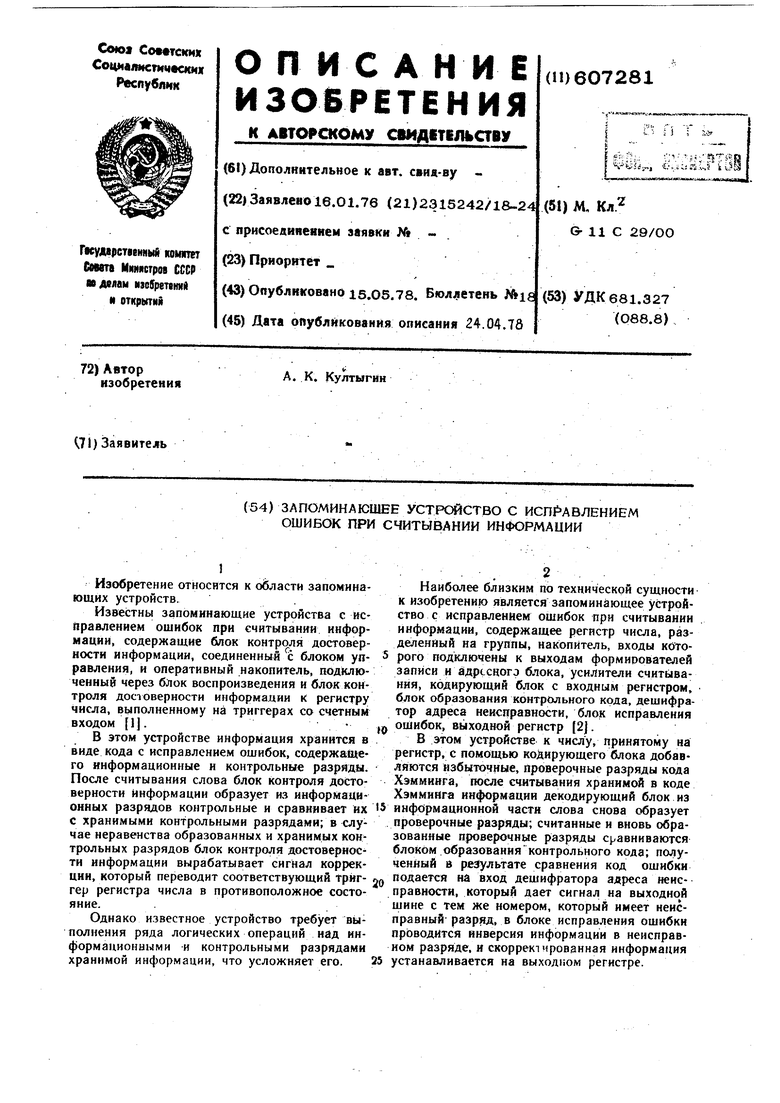

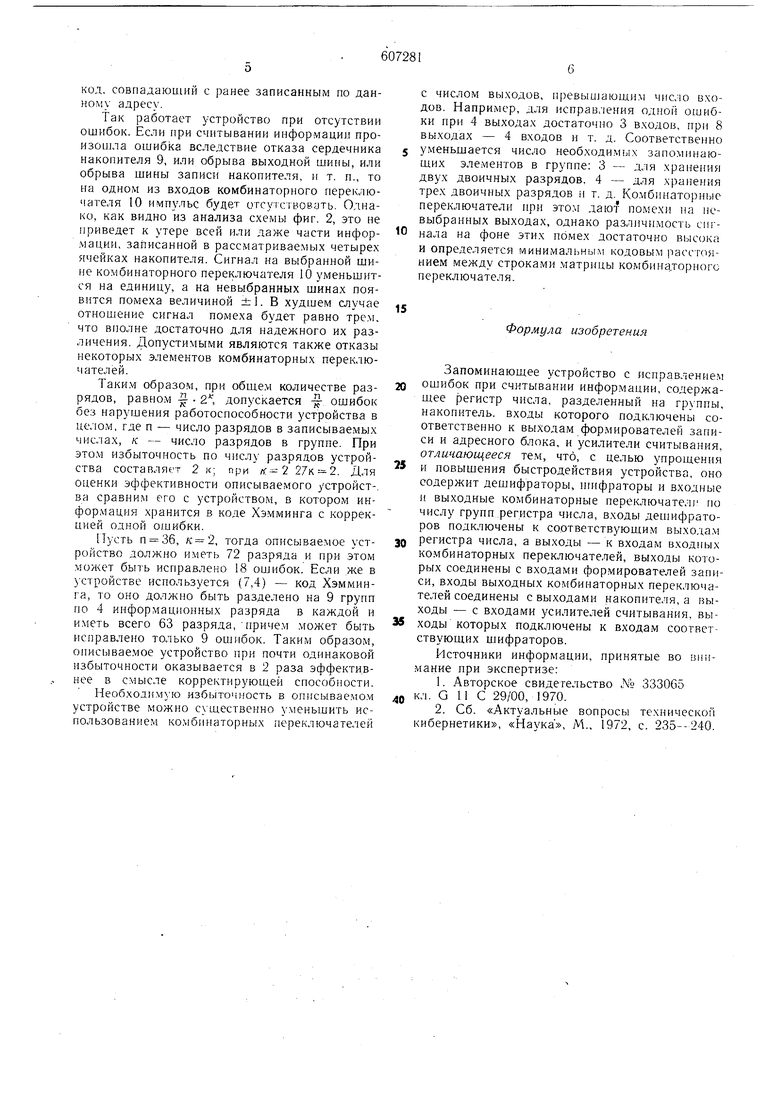

На фиг. 1 представлена блок-схема описываемого устройства; на фиг. 2 - схема линейного трансформаторного комбинаторного переключателя с суммированием напряжений, а также входные и выходные импуяьсы, поясняющие его работу.

Устройство содержит регистр числа 1, разделенный на группы, например, по два разряда в каждой. Выходы двух разрядов 2i и 2 этого регистра, относящихся к одной группе, соединены с входами дешифратора 3. Выходы де1пифратора соединены с входами входного комбинаторного иереключате.ля 4. выполненного, например, в виде линейного трансформаторного комбинаторного переключателя с суммированием напряжений, схема которого приведена на фиг. 2. Выходы входного комбинаторного переключателя через формирователи записи 5, 6, 7, 8 соединены с соответствующи.ми разрядными щинами записи накопителя 9 (предпочтительнее, чтобы запоминающие элементы накопителя имели считанные сигналы «1 и «О, различающиеся по полярности). Выходные шины накопителя, относящиеся к одной группе хранимой информации, соединены с входами выходного комбинаторного переключателя 10, аналогичного комбинаторному переключателю 4. Выходы комбинаторного переключателя 10 через усилители считывания 11, 12, 13, 14 соединены с входами шифратора 15, преобразующего унитарный код («1 из п) в двоичный, 2-ух разрядный. Аналогичные соединения блоков сделаны для всех ocfaльныx групп (пар) разрядов (на чертеже не показаны).

Адресный блок 16 включает в себя аппаратуру, необходимую для приема кода адреса, его расшифровки и формирования импульсов обращения к накопителю по соответствующим координатным щинам; его выходы соединены с адресными шинами накопителя 9.

Если накопитель 9 построен из запоминающп элементов с а.мплитудны.м различением сигналов «1 и «О, то между его выходами и входами выходного ко.мбинаторно1о переключа4

теля 10 целесообразно включить преобразователь однополярных сигналов в двухполярные (на чертеже не показан).

Рассмотрим работу устройства на примере ферритового запоминающего устройства, построенного по системе 2Д с двумя сердечниками на разряд. Информация, подлежащая записи в накопитель 9, поступает в обычном двоичном коде на регистр числа 1, разделенный на группы , например, по два разряда в каждой.

0 Двухразрядный код с выходов соответствующих разрядов 2 и 2 регистра числа 1 определяет номер выбранной выходной шины дешиф ратора 3. Импульс с этой шипы подается на соответствующую щину входного комбинаторного переключателя 4, имеющего четыре входа

5 и выхода. Для определенности рассматривается линейный трансформаторный комбннаторный переключатель, схема которого приведена на фиг. 2. В данном случае импульс с выбранной щины дешифратора 3 подается на одну из

0 выходных обмоток 17 переключателя. В силу обратимости переключателя при подаче импульс на одну из выходных обмоток на входных обмотках 18 появляются импульсы, полярность которых соответствует знакам членов определенной строки матрицы Адамара (на фиг. 2

5 изображены и.мпульсы на входных обмотках переключателя, соответствующие второй строке матрицы Адамара). Импульсы с выходов входного комбинаторного переключателя 4 усиливаются до требуемой aмплптyдь формирователями записи 5, 6, 7, 8 и подаются на соответ0ствующие четыре щины накопителя 9. Таким образом, двухразрядный код с регистра числа 1 оказывается записанным в четыре запоминающих ячейки накопителя; при этом отсутствует взаимно-однозначное соответствие разрядов записываемого двухразрядного кода и запоминающих ячеек накопителя; все четыре запоминающих ячейки хранят информацию с двух разрядах записываемого кода в виде комбинации цифр, соответствующей определенной строке матрицы Адамара.

При считывании сигналы с рассматриваемых четырех запоминающих ячеек накопителя

9подаются на входы выходного комбинаторного переключателя 10, поскольку считанные

сигналы примерно равны по амплитуде, а полярность их соответствует одной из строк матрицы Адамара (поскольку в рассматриваемом устройстве сигналы «1 и О различаются по полярности), то на соответствующем выходе комбинаторного переключателя 10 появится суммарный сигнал, .-(мп.литуда которого равна учетверенной амплитуде каждого из считанных сигналов с сердечников накопителя. При этом на всех остальных выходах комбинаторного переключателя 10 сигналы отсутствуют. Сумматорный сигнал с выхода переключателя

10усиливается соответствующим усилителем считывания (11, 12, 13 или 14) и подается на вход шифратора 15, преобразующего унитарный код в двоичный, т. е. П1ифратор 15 выполняет операцию, обратную дешифрации. На выходе шифратора 15 получается двухразрядный

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с контролем цепей коррекции ошибок | 1981 |

|

SU982099A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| Устройство для контроля блоков коррекции ошибок в памяти | 1980 |

|

SU951407A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Устройство для контроля памяти | 1982 |

|

SU1020865A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1104588A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство | 1975 |

|

SU746741A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

| Запоминающее устройство с исправлением ошибок | 1978 |

|

SU686085A1 |

i-- -х„-(код. совпадающий с ранее записанным по данному адресу.

tai работает устройство при отсутствии ошибок. Если при считывании информации произошла ошибка вследствие отказа сердечника накопителя 9, или обрыва выходной шины, или обрыва шины записи накопителя, и т. п., то на одном из входов комбинаторного переключателя 10 импульс будет отсутствовуть. Однако, как видно из анализа схемы фиг. 2, это не приведет к утере всей или даже части информации, записанной в рассматриваемых четырех ячейках накопителя. Сигнал на выбранной шине комбинаторного переключателя 10 уменьшится на единицу, а на невыбранных шинах появится помеха величиной ±1. В худшем случае отношение сигнал помеха будет равно трем, что вполне достаточно для надежного их различения. Допустимыми являются также отказы некоторых элементов комбинаторных переключателей.

TaKH.v образом, при обще.м количестве разрядов, равно.м -2- . , допускается - ошибок без нарушения работоспособности устройства в целом, где п - число разрядов в записываемых числах, к - число разрядов в группе. При этом избыточность по числу разрядов устройства составляет 2 к; при л:-2 27к 2. Для оценки эффективности описывае.мого устройст-. ва сравним его с устройством, в котором информация хранится в коде Хэмминга с коррекцией одной ошибки.

Пусть п 3б, к 2, тогда описываемое устройство должно иметь 72 разряда и при этом может быть исправлено 18 ошибок. Если же в }стройстве используется (7,4) - код Хэмминга, то оно должно быть разделено на 9 групп по 4 информационных разряда в каждой и иметь всего 63 разряда, нричем может быть исправлено только 9 ошибок. Таким образом, онисывае.мое устройство при почти одинаковой избыточности оказывается в 2 раза эффективнее в смысле корректируюндей способности.

Необ.ходимую избыточность в описывае.мом устройстве можно существенно уменьшить использованием ко.мби на торных переключателей

с числом выходов, превышающим число входов. Например, для исправления одной О1иибки при 4 выходах достаточно 3 входов, при 8 выходах - 4 входов и т. д. Соответственно уменьшается число необходимых запоминающих элементов в группе: 3 - для хранения двух двоичных разрядов. 4 - для хранения трех двоичных разрядов н т. д. Комбинаторн1 1е переключатели нри это.м дают помехи на невыбранных выходах, однако различимость сигнала на фоне этих пб.мех достаточно высока и определяется минимальным кодовым расстоянием .между строками .матрицы ко.мбина.торно1с переключателя.

15

Формула изобретения

Запоминающее устройство с исправлением

ошибок при считывании информации, содержащее регистр числа, разделенный на группы, накопитель, входы которого подключены соответственно к выхода.м фор.мирователей записи и адресного блока, и усилители считывания, отличающееся те.м, чтб, с целью упрощения

и повышения быстродействия устройства, оно содержит дешифраторы, шифраторы и входные и выходные комбинаторные переключател) по числу групп .регистра числа, входы дешифраторов подключены к соответствующим выходам

регистра числа, а выходы - к входам входных ко.мбинаторных переключателей, выходы которых соединены с входами формирователей записи, входы выходных комбинаторных переключателей соединены с выходами накопителя, а выходы - с входами усилителей считывания, выходы которых подключены к входа.м соответ ствующих шифраторов.

Источники информации, принятые во внимание нри экспертизе:

rz

t.i. гг

LL

Г I i Г

I

шиши

. . л

ГТ1 1 ,

.

-U- Л

Авторы

Даты

1978-05-15—Публикация

1976-01-16—Подача