Известные миожительно-делительные устройства частотно-импульсных сигналов обладают сложной схемой управления, необходимой для отработки скачкообразных изменений входной частоты за период меньшей из умножаемых частот.

Предложенное множительно-делительное устройство отличается тем, что с целью упрощения 1зходы двоичных счетчиков импульсов через вентили соединены с одним входным зажимо.м устройства и с выходом управляющего триггера. Счетный вход последнего подсоединен tKO второму входному зажиму устройства, выходы управляющего триггера подсоединены также « одному из входов двух групп схем «И, выходы которых соединены со входами схем «ПЛИ, выходы которых в свою очередь соединены с единичными входами триггеров делителя частоты, и через формирователи импульсав - со входами установки триггеров-счетчиков в «единичное состояние. Вход делителя частоты соединен с источником опорной частоты, а выход его - с выходом устройства и со вторыми входами схем «И, третьи входы которых соединены с выходами триггеров двоичных счетчиков.

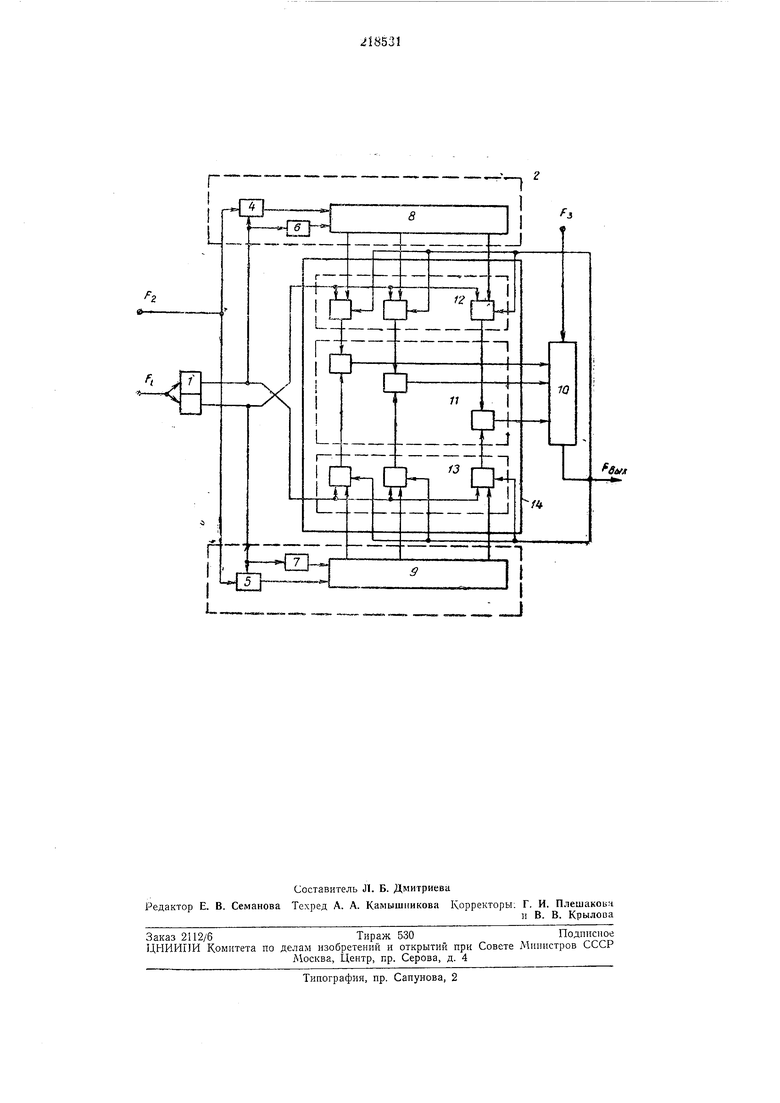

На чертеже приведена блок-схема множительно-лТ,ел.ительного устройства.

частот, состоящих из вентилей 4, 5, формирователей 6, 7 импульсов и счетчиков 8, 9 импульсов. На счетный вход управляющего триггера поступает одна из частот. Выходы триггера связаны с вентилями 4, 5 (через которые вторая частота поступает на счетный вход счетчиков 8, 9 импульсов) и через фор: пгрователи 6, 7 импульсов - с шинами установки триггеров счетч.иков ид пульсов в «единичное состояние. «Единичные входы триггеров делителя частоты 10 соединены с «единичными выходами триггеров счетчиков 8, 9 импульсов через поразрядные схе.мы «ИЛИ 11 и две груипы импульсно-потенциальных схем совпадения 12, 13, входы которых соединены с выходом делителя частоты и с противоположными выходами управляющего триггера. Поразрядные схемы «ПЛИ П и иМПульсно-потенциальные схемы совпадения

12, 13 объединены в блок передачи кодов 14.

В исходном состоянии триггеры счетчиков 8, 9 импульсов установлены в «нулевое состояние, а триггеры делителя частоты и управЛЯЮЩ.ИЙ триггер - в «единичное состояние. «Единичный выход управляющего триггера подключен к вентилю и к .выходам формирователя 6 и схемы совпадения 13, а «нулевой - к вентилю 5 и к входам фор.мироваПервый импульс, приходящий на счетный вход триггера I, перебрасывает его в HOiBoe состояние, лри этом на вентиль 4 и схему совпадения 13 поступает разрешающий потенциал, а триггеры счетчика 8 устанавливаются в «единичное состояние имлульсом, поступающим с выхода формирователя 6 импульсов.

С этого времени начинается измерение первого периода входного сигнала. На выходе устройства до прихода второго импульса будет импульсная последовательность с опорной частотой, равной Р$, так как код числа, хранящегося в счетчике 9 н переписываем ого с помощью схемы совпадения 13 и схемы «ИЛИ 11, равен 2 - 1 (п - количество триггеров в счетчиках 8, 9). К моменту прихода второго импульса в счетчике 8 зафиксируется код отношения N двух частот

PI

1,

где FZ - частота импульсов, поступающих на вход измерителей 2, 3 отно шений;

/i - частота импульсов, поступающих на вход управляющего триггера I.

С приходом второго импульса производится установка триггеров счетчика 9 в «единичное состояние, а на вентиль 5 и схемы совпадения 12 поступает разрешающий потенциал. Теперь в триггер решающего делителя частоты с помощью схем совпадения 12 ,и схемы «ИЛИ 11 вводится код 2 -1-N. В этом случае коэффициент деления решающего делителя

частоты становится равным отношению частоты FI и РЧ.

Иа выходе устройства будет импульсная последовательность

3 Л

Иредмет изобретения

Множительно-делительное устройство частотно-импульсных сигналов, содержащее двоичные счетчики, делитель частоты, управляющий триггер, формирователи импульсов, схемы «И и «ИЛИ, отличающееся тем, что, с

целью упрощения устройства, входы двоичных счетчиков импульсов через вентилл соединены с одним входным зажимом устройства и с выходо1М управляющего триггера, счетный вход которого подсоединен .ко второму :входному

зажиму устройства, выходы управляющего триггера подсоединены также к одному из входов двух групп схем «И, выходы которых соединены со входами схем «ИЛИ, выходы которых в свою очередь соединены с единичными входами триггеров дел-ителя частоты, и через формирователи импульсов - со входами установки триггеров-счетчиков в «единичное состояние, вход делителя частоты соединен с источником опорной частоты, а выход

его - с выходом устройства и со вторыми входами схем «Pi, третьи входы которых соединены с выходами триггеров двоичных счетчиков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

| Устройство задержки сигналов | 1982 |

|

SU1015491A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU364938A1 |

| Цифровой следящий частотомер | 1980 |

|

SU892335A1 |

| Преобразователь двоичного кода в двоично-десятичный код с масштабированием | 1978 |

|

SU746498A1 |

| Устройство задержки сигналов | 1982 |

|

SU1104655A2 |

| Делитель частоты с переменным коэффициентом деления | 1990 |

|

SU1812636A1 |

| Устройство задержки сигналов | 1984 |

|

SU1215166A1 |

| Устройство задержки сигналов | 1983 |

|

SU1091306A2 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1972 |

|

SU331400A1 |

Даты

1968-01-01—Публикация