Известны цифро-аналоговые преобразователи, содержащие регистр из запоминающих ячеек на триггерах в каждом разряде.

Отличием предлагаемого устройства является то, что к кодовой шине каждого разряда подключен через транзисторный ключ несимметричный триггер, а адресная шина соединена через резистор с базой транзисторного ключа.

Это упрощает устройство.

В качестве запоминающего элемента запоминающей ячейки использованы транзисторные несимметричные триггеры, причем эмиттер первого транзистора триггера подключен к шине, потенциал которой лежит между уровнями, соответствующими сигналам кода 0 и 1.

В качестве ключа, включенного между сигнальным входом запоминающей ячейки и входом триггера, использован транзистор, база которого подключена к управляющему входу ячейки. При этом ток в цепи эмиттер-коллектор при записи единицы противоположен току в этой же цепи при записи нуля.

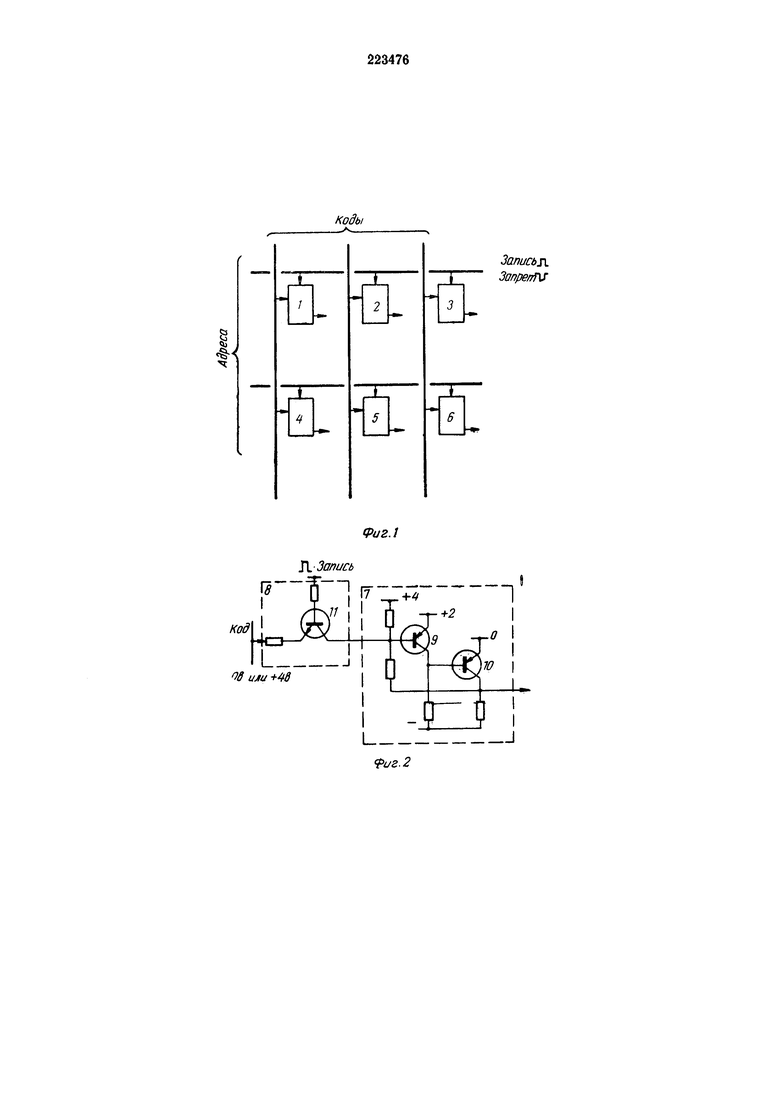

На фиг. 1 показано запоминающее устройство предлагаемого преобразователя; на фиг. 2 - схема запоминающей ячейки. Преобразователь имеет систему вертикальных шин, на которые подается параллельный цифровой код, систему горизонтальных шин, на которые подаются адреса (сигналы, разрешающие записать данный код в данный регистр), и два регистра, составленные из запоминающих ячеек 1, 2, 3 и 4, 5, 6. Каждая ячейка имеет два входа: сигнальный, подключенный к вертикальной шине, и управляющий, подключенный к адресной шине.

Ячейка состоит из двух элементов: запоминающего элемента - несимметричного триггера 7 и ключа 8. Запоминающий элемент образован транзисторами 9, 10 и относящимися к ним резисторами.

Ключ образован транзистором 11 и двумя резисторами. Таким образом, запоминающая ячейка содержит всего три транзистора и шесть сопротивлений (всего девять деталей).

В качестве ключа на фиг. 2 показан транзистор типа n-p-n. Поэтому сигналу «запись» должен соответствовать положительный уровень, а сигналу «запрет» - отрицательный (менее положительный).

Сигналам 0 и I должны соответствовать уровни, один из которых на 1,5-2 в выше потенциала эмиттерной шины транзистора 9, а другой - на ту же величину ниже этого потенциала. Кодирование этих уровней (какой из них считать за 0, какой - за I) зависит от схемы связи между регистром и делителем, который управляется регистром. При прохождении положительного сигнала транзистор 11 ключа (см. фиг. 2) работает как бы в инверсном режиме, при подаче на сигнальный вход отрицательного сигнала режим работы ключа соответствует прямому включению транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2506598C1 |

| Устройство для многоточечной сигнализации | 1990 |

|

SU1741167A1 |

| Устройство для вывода данных из управляющей цифровой вычислительной машины на обьекты | 1974 |

|

SU507865A1 |

| Матричный анализатор оптических изображений | 1973 |

|

SU495989A1 |

| Функциональный преобразователь | 1977 |

|

SU674047A1 |

| РАЗРЯДНЫЙ ЭЛЕМЕНТ ДЛЯ ПРЕОБРАЗОВАТЕЛЯ КОДА В НАПРЯЖЕНИЕ | 1967 |

|

SU224176A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| Устройство фазоимпульсной модуляции | 1985 |

|

SU1411958A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

Запоминающее устройство многоканального цифро-аналогового преобразователя, содержащее транзисторные ключи и триггеры, отличающееся тем, что, с целью упрощения, к кодовой шине каждого разряда подключен через транзисторный ключ несимметричный триггер, а адресная шина соединена через резистор с базой транзисторного ключа.

Авторы

Даты

1968-11-13—Публикация

1966-08-19—Подача