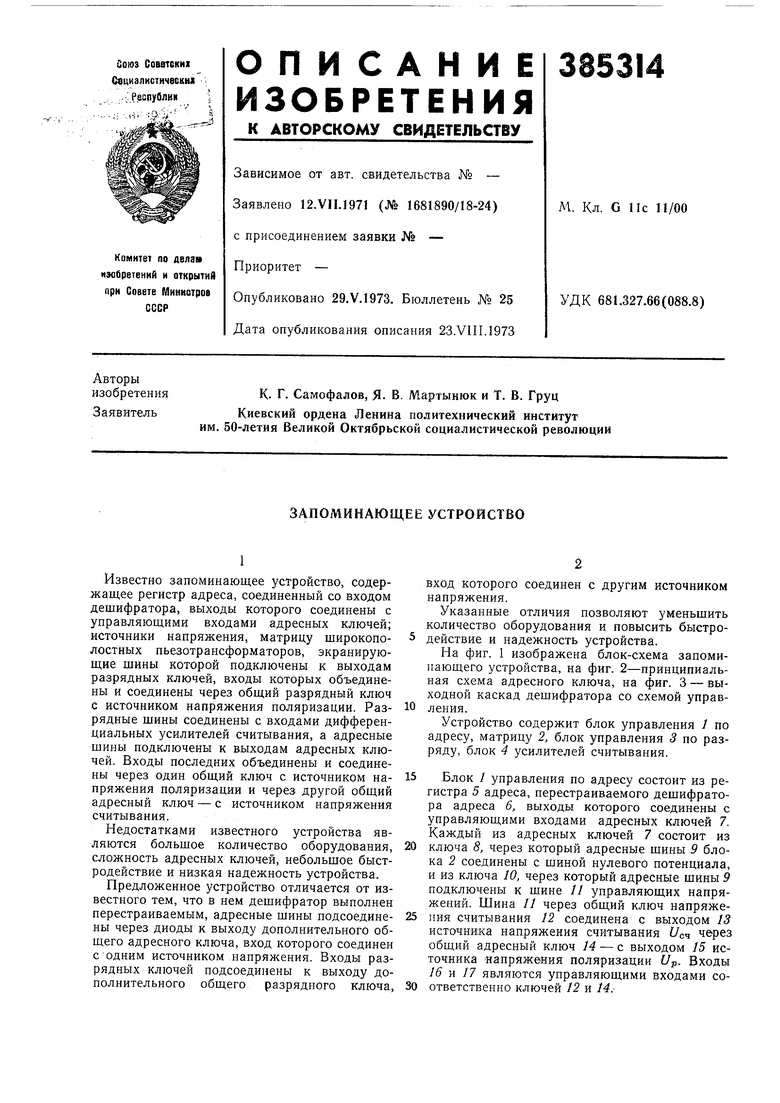

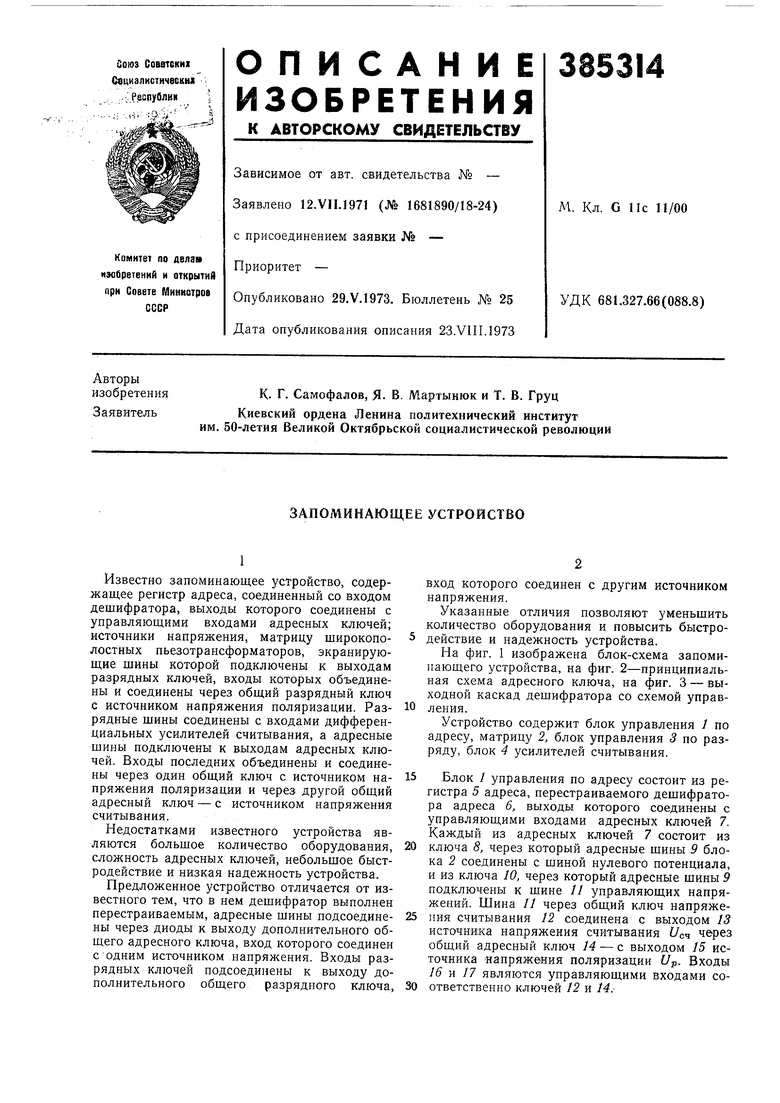

Известно запоминающее устройство, содержащее регистр адреса, соединенный со входом дешифратора, выходы которого соединены с управляющими входами адресных ключей; источники напряжения, матрицу щирокополостных пьезотрансформаторов, экранирующие щины которой подключены к выходам разрядных ключей, входы которых объединены и соединены через общий разрядный ключ с источником напряжения поляризации. Разрядные щины соединены с входами дифференциальных усилителей считывания, а адресные шины подключены к выходам адресных ключей. Входы последних объединены и соединены через один общий ключ с источником напряжения поляризации и через другой общий адресный ключ - с источником напряжения считывания. Недостатками известного устройства являются больщое количество оборудования, сложность адресных ключей, небольщое быстродействие и низкая надежность устройства. Предложенное устройство отличается от известного тем, что в нем дешифратор выполнен перестраиваемым, адресные щины подсоединены через диоды к выходу дополнительного общего адресного ключа, вход которого соединен с одним источником напряжения. Входы разрядных ключей подсоединены к выходу дополнительного общего разрядного ключа, ход которого соединен с другим источником напряжения. Указанные отличия позволяют уменьшить количество оборудования и повысить быстродействие и надежность устройства. На фиг. 1 изображена блок-схема запоминающего устройства, на фиг. 2-принципиальная схема адресного ключа, на фиг. 3 - выходной каскад дещифратора со схемой управления. Устройство содержит блок управления / по адресу, матрицу 2, блок управления 3 по разряду, блок 4 усилителей считывания. Блок / управления по адресу состоит из регистра 5 адреса, перестраиваемого дещифратора адреса 6, выходы которого соединены с управляющими входами адресных ключей 7. Каждый из адресных ключей 7 состоит из ключа 8, через который адресные щины 9 блока 2 соединены с щиной нулевого потенциала, и из ключа 10, через который адресные шины 9 подключены к шине // управляющих напряжений. Шина // через общий ключ напряжения считывания 12 соединена с выходом 13 источника напряжения считывания через общий адресный ключ 14 - с выходом 15 источника напряжения поляризации Up. Входы 16 и /7 являются управляющими входами соответственно ключей 12 и 14.

Адресные шины 9 через диоды подключены к выходу ключа 19, вход 20 которого соединен с источником напряжения 1/3 . Вход 21 - управляющий вход ключа 19.

В матрице 2 входные электроды 22 широкополосных пьезотрансформаторов 23 соединены с адресными шинами 9. Экранируюш,ие электроды 24 пьезотрансформаторов объединены по разрядам в экранируюш,ие шины 25. Выходные электроды 26 и 27 (по два на каждый разряд) пьезотрансформаторов объединены в разрядные шины 28 и 29, которые соединены с входами дифференциальных усилителей считывания 30 блока 4.

Пьезокерамические пластины 31 генераторной секции пьезотрансформаторов имеют жесткую поляризацию противоположного направления под выходными электродами 26 и 27. Пластина 32 секции возбуждения может иметь различную поляризацию, причем паправление ее определеяется записанной информацией.

Экранирующие щины 25 подключены к выходам разрядных ключей 33, каждый из которых состоит из двух ключей: ключа 34, через который экранирующие шины соединены с шиной нулевого потенциала, и ключа 35, через который экранирующие шины 25 соединены с выходами регистра числа 37. Шина 36 соединена через ключ 38 с выходом 39 источника напряжения поляризации t/p и через ключ 40 с выходом 41 источника напряжения 2/3 f/p. Входы 42 и 43 являются управляющими входами соответственно ключей 38 и 40.

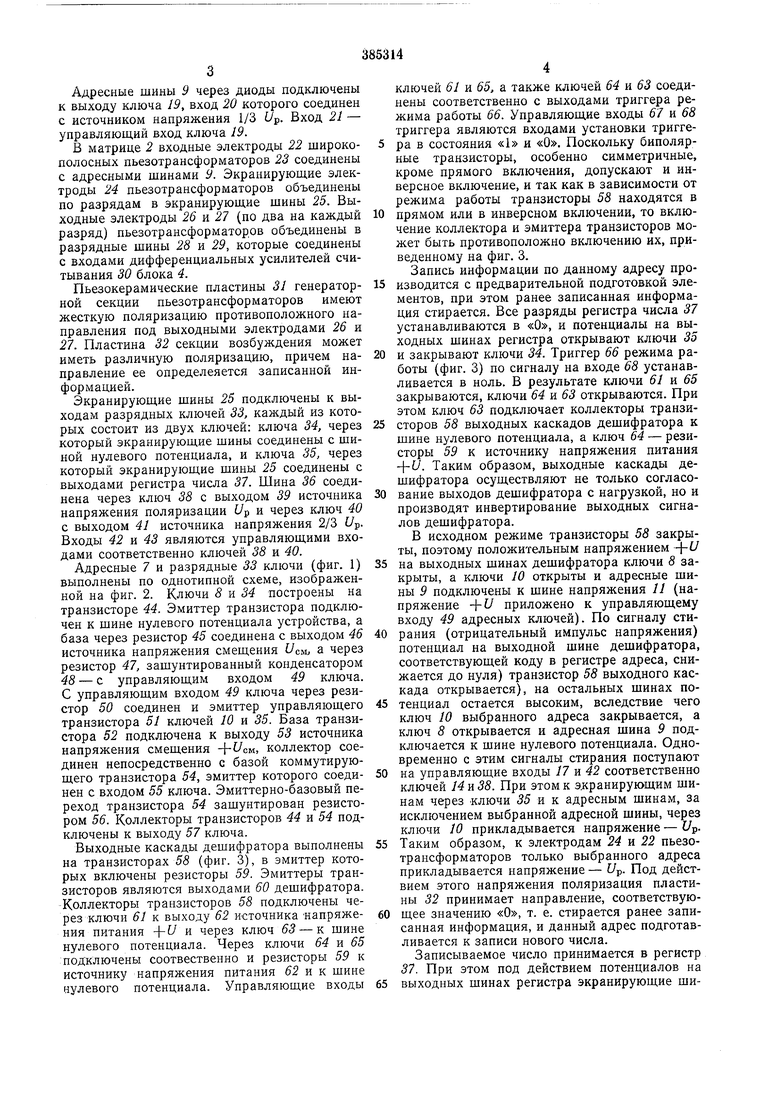

Адресные 7 и разрядные 33 ключи (фиг. 1) выполнены по однотипной схеме, изображенной на фиг. 2. Ключи 8 и 34 построены на транзисторе 44- Эмиттер транзистора подключен к шине нулевого потенциала устройства, а база через резистор 45 соединена с выходом 46 источника напряжения смещения Ucu, а через резистор 47, зашунтированный конденсатором 48 - с управляющим входом 49 ключа. С управляющим входом 49 ключа через резистор 50 соединен и эмиттер управляющего транзистора 51 ключей 10 и 35. База транзистора 52 подключена к выходу 53 источника напряжения смещения +t/cM, коллектор соединен непосредственно с базой коммутирующего транзистора 54, эмиттер которого соединен с входом 55 ключа. Эмиттерно-базовый переход транзистора 54 зашунтирован резистором 56. Коллекторы транзисторов 44 и 54 подключены к выходу 57 ключа.

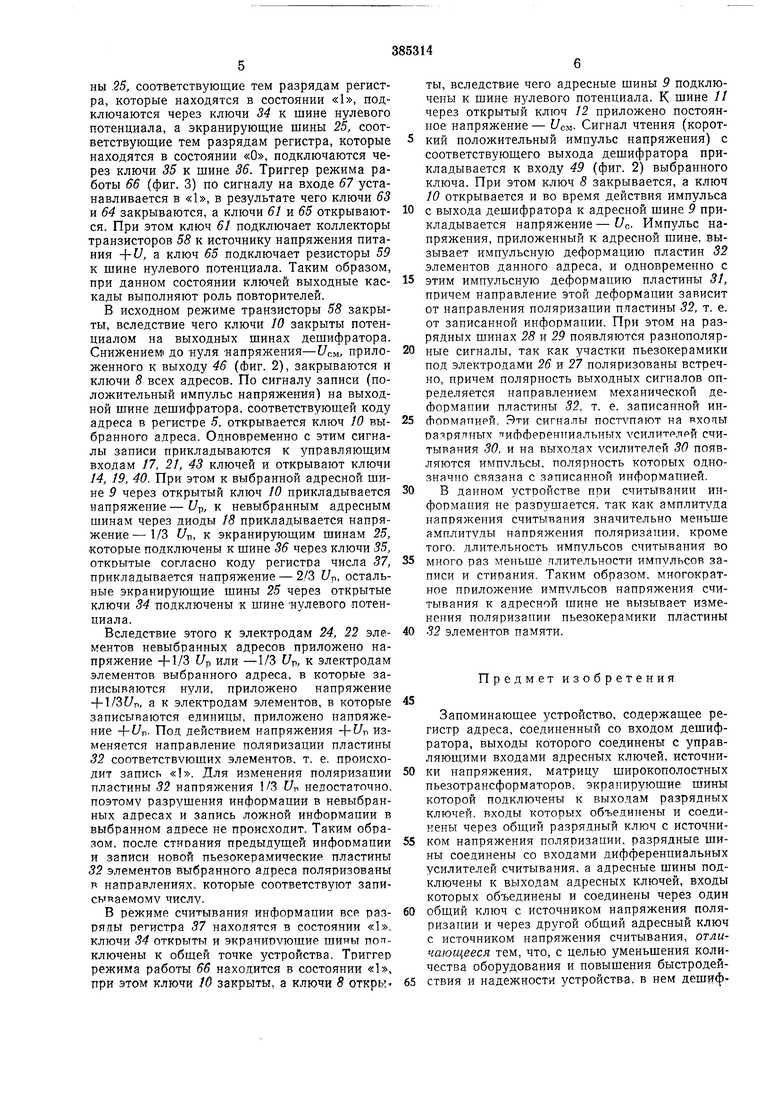

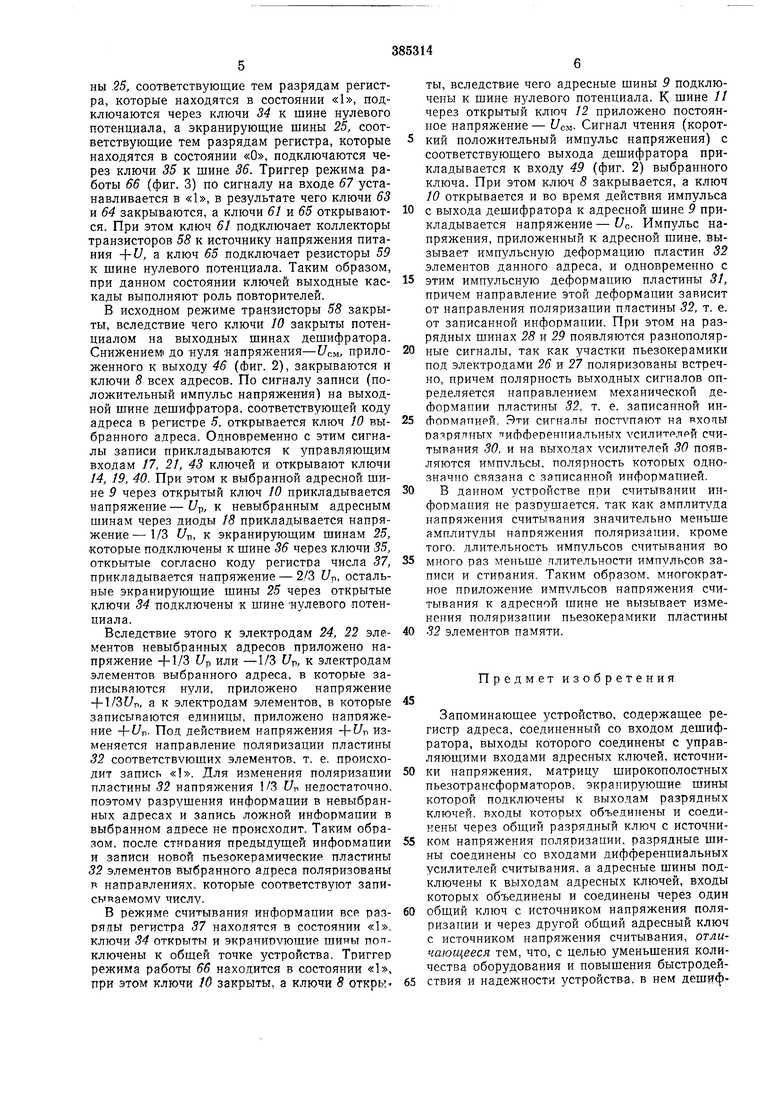

Выходные каскады дешифратора выполнены на транзисторах 55 (фиг. 3), в эмиттер которых включены резисторы 59. Эмиттеры транзисторов являются выходами 60 дешифратора. Коллекторы транзисторов 58 подключены через ключи 61 к выходу 62 источника напряжения питания к через ключ 63 - к шине нулевого потенциала. Через ключи 64 и 65 подключены соотвественно и резисторы 59 к источнику напряжения питания 62 и к шине нулевого потенциала. Управляющие входы

ключей 61 и 65, а также ключей 64 и 63 соединены соответственно с выходами триггера режима работы 66. Управляющие входы 67 и 68 триггера являются входами установки триггера в состояния «1 и «О. Поскольку биполярные транзисторы, особенно симметричные, кроме прямого включения, допускают и инверсное включение, и так как в зависимости от режима работы транзисторы 55 находятся в

10 прямом или в инверсном включении, то включение коллектора и эмиттера транзисторов может быть противоположно включению их, приведенному на фиг. 3. Запись информации по данному адресу производится с предварительной подготовкой элементов, при этом ранее записанная информация стирается. Все разряды регистра числа 37 устанавливаются в «О, и потенциалы на выходных шинах регистра открывают ключи 35

0 и закрывают ключи 34. Триггер 66 режима работы (фиг. 3) по сигналу на входе 68 устанавливается в ноль. В результате ключи 61 и 65 закрываются, ключи 64 и 63 открываются. При этом ключ 63 подключает коллекторы транзисторов 55 выходных каскадов дешифратора к шине нулевого потенциала, а ключ 64 - резисторы 59 к источнику напряжения питания . Таким образом, выходные каскады дешифратора осуществляют не только согласование выходов дешифратора с нагрузкой, но и производят инвертирование выходных сигналов дешифратора.

В исходном режиме транзисторы 55 закрыты, поэтому положительным напряжением

5 на выходных шинах дешифратора ключи 5 закрыты, а ключи 10 открыты и адресные шины 9 подключены к шине напряжения 11 (напряжение приложено к управляющему входу 49 адресных ключей). По сигналу стирания (отрицательный импульс напряжения) потенциал на выходной шине дешифратора, соответствующей коду в регистре адреса, снижается до нуля) транзистор 58 выходного каскада открывается), на остальных шинах потенциал остается высоким, вследствие чего ключ 10 выбранного адреса закрывается, а ключ 8 открывается и адресная шина 9 подключается к шине нулевого потенциала. Одновременно с этим сигналы стирания поступают

0 на управляющие входы 17 и 42 соответственно ключей 14 и 55. При этом к эдранирующим шинам через КЛЮЧИ 35 и к адресным шинам, за исключением выбранной адресной шины, через ключи 10 прикладывается напряжение - i/p.

5 Таким образом, к электродам 24 и 22 пьезотрансформаторов только выбранного адреса прикладывается напряжение - Up. Под действием этого напряжения поляризация пластины 32 принимает направление, соответствующее значению «О, т. е. стирается ранее записанная информация, и данный адрес подготавливается к записи нового числа.

Записываемое число принимается в регистр 37. При этом под действием потенциалов на

выходных щинах регистра экранирующие шины 25, соответствующие тем разрядам регистра, которые находятся в состоянии «1, подключаются через ключи 34 к шине нулевого потенциала, а экранирующие щины 25, соответствующие тем разрядам регистра, которые находятся в состоянии «О, подключаются через ключи 35 к шине 36. Триггер режима работы 66 (фиг. 3) по сигналу на входе 67 устанавливается в «1, в результате чего ключи 5с и 64 закрываются, а ключи 61 и 65 открываются. При этом ключ 61 подключает коллекторы транзисторов 58 к источнику напряжения питания -{-U, г. ключ 65 подключает резисторы 59 к щине нулевого потенциала. Таким образом, при данном состоянии ключей выходные каскады выполняют роль повторителей.

В исходном режиме транзисторы 58 закрыты, вследствие чего ключи 10 закрыты потенциалом на выходных шинах дешифратора. Снижением до нуля напряжения-С/см, приложенного к выходу 46 (фиг. 2), закрываются и ключи 8 всех адресов. По сигналу записи (положительный импульс напряжения) на выходной щине дешифратора, соответствующей коду адреса в регистре 5, открывается ключ 10 выбранного адреса. Одновременно с этим сигналы записи прикладываются к управляющим входам 17, 21, 43 ключей и открывают ключи 14, 19, 40. При этом к выбранной адресной шине 9 через открытый ключ 10 прикладывается напряжение - U-p, к невыбранным адресным шинам через диоды 18 прикладывается напряжение-1/3 U-n, к экранирующим шинам 25, которые подключены к щине 36 через ключи 35, открытые согласно коду регистра числа 37, прикладывается напряжение - 2/3 f/p, остальные экранируюшие шины 25 через открытые ключи 34 -подключены к щине нулевого потенциала.

Вследствие этого к электродам 24, 22 элементов невыбранных адресов приложено напряжение + 1/3 f/p или -1/3 С/р, к электродам элементов выбранного адреса, в которые записываются нули, приложено напряжение - 1/3f/p, а к электродам элементов, в которые записываются единицы, приложено напряжение + 7т1. Под действием напряжения +t/p изменяется направление поляризации пластины 32 соответствующих элементов, т. е. происходит запись «1. Для изменения поляризации пластины 32 напряжения 1/3 Vv недостаточно, поэтому разрущения информации в невыбранных адресах и запись ложной информации в выбранном адресе не происходит. Таким образом, после стирания предыдущей информации и записи новой пьезокерамические пластины 32 элементов выбранного адреса поляризованы р направлениях, которые соответствуют записываемому числу.

В режиме считывания информации все разряды регистра 37 находятся в состоянии «1. ключи 34 открыты и экранирующие шины потключены к общей точке устройства. Триггер режима работы 66 находится в состоянии «1, при этом ключи 10 закрыты, а ключи 8 открК

ты, вследствие чего адресные щины 9 подключены к щине нулевого потенциала. К шине // через открытый ключ 12 приложено постоянное напряжение - t/см. Сигнал чтения (короткий положительный импульс напряжения) с соответствующего выхода дешифратора прикладывается к входу 49 (фиг. 2) выбранного ключа. При этом ключ 5 закрывается, а ключ 10 открывается и во время действия импульса

с выхода дешифратора к адресной шине 9 прикладывается напряжение - С/с. Импульс напряжения, приложенный к адресной шине, вызывает импульсную деформацию пластин 32 элементов данного адреса, и одновременно с

этим импульсную деформацию пластины 31, причем направление этой деформации зависит от направления поляризации пластины 32, т. е. от записанной информации. При этом на разрядных щинах 28 и 29 появляются разнополярные сигналы, так как участки пьезокерамики под электродами 26 и 27 поляризованы встречно, причем полярность выходных сигналов определяется направлением механической деформации пластины 32, т. е. записанной инсЬормапиРЙ. Эти сигналы поступают на входы раярялньтх яиффеоенпиальных усилителей считывания 30. и на выходах усилителей 30 появляются ИМПУЛЬСЫ, полярность которых однозначно связана с записанной информацией.

В данном устройстве при считывании информация не разрущается, так как амплитуда напряжения считывания значительно меньше амплитуды напряжения поляризации, кроме того, длительность импульсов считывания во

много раз меньше длительности импульсов записи и стирания. Таким образом, многократное приложение импульсов напряжения считывания к адресной щине не вызывает изменения поляризации пьезокерамики пластины

32 элементов памяти.

Предмет изобретения

45

Запоминающее устройство, содержащее регистр адреса, соединенный со входом дешифратора, выходы которого соединены с управляющими входами адресных ключей, источники напряжения, матрицу широкополостных пьезотрансформаторов, экранирующие щины которой подключены к выходам разрядных ключей, входы которых объединены и соединены через общий разрядный ключ с источником напряжения поляризации, разрядные шины соединены со входами дифференциальных усилителей считывания, а адресные щины подключены к выходам адресных ключей, входы которых объединены и соединены через один

общий ключ с источником напряжения поляризации и через другой общий адресный ключ с источником напряжения считывания, отличающееся тем, что, с целью уменьшения количества оборудования и новыщения быстродействия и надежности устройства, в нем дещиф7

ратор -выполиен перестраиваемым, адресные шины подсоединены через диоды к выходу дополнительного общего адресного ключа, вход которого соедииен с одним источником .напряжения, входы разрядных ключей подсоединены ;к выходу дополнительного общего разрядного ключа, вход которого соединен с другим источником напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОЦП•'t-li | 1971 |

|

SU419982A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Запоминающее устройство | 1973 |

|

SU481067A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU364962A1 |

| ВСЕСОЮЗНАЯ ' | 1973 |

|

SU368645A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Запоминающее устройство | 1973 |

|

SU447757A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

| Запоминающее устройство | 1976 |

|

SU608197A1 |

11613 17 15

ТТ ир

(57 68

Л

-25

UCM

-05

Риг.2

Pu2.3

Авторы

Даты

1973-01-01—Публикация