Известен функциональный преобразователь, содержащий амплитудные дискриминаторы, дешифраторные схемы, матрицы сопротивлений, аналоговые усилители-сумматоры и аналоговые логические схемы.

Предложенное устройство отличается тем, что для увеличения его точности оно содержит амплитудно-позиционные генераторы образующих функций, состоящие из последовательно соединенных амплитудного дискриминатора, дешифратора, матриц сопротивлений и аналогового усилителя сумматора, и логический блок, включающий амплитудно-позиционные логические схемы. Каждая из этих схем содержит разрядные схемы выбора, в которых выход разряда каждой входной величины подсоединен к эмиттеру одного триода-усилителя и базе другого. Выходы этих усилителей подключены через триоды-инверторы к вентилям на входе следующей разрядной схемы выбора и к вентилям, пропускающим соответствующие разряды входных величин на вход аналоговой логической схемы. Кроме того, в предлагаемом устройстве для упрощения схемы выходы триодов разрядных схем выбора амплитудно-позиционных логических схем подключены к дешифратору, выходы которого через схемы «ИЛИ» подключены к вентилям.

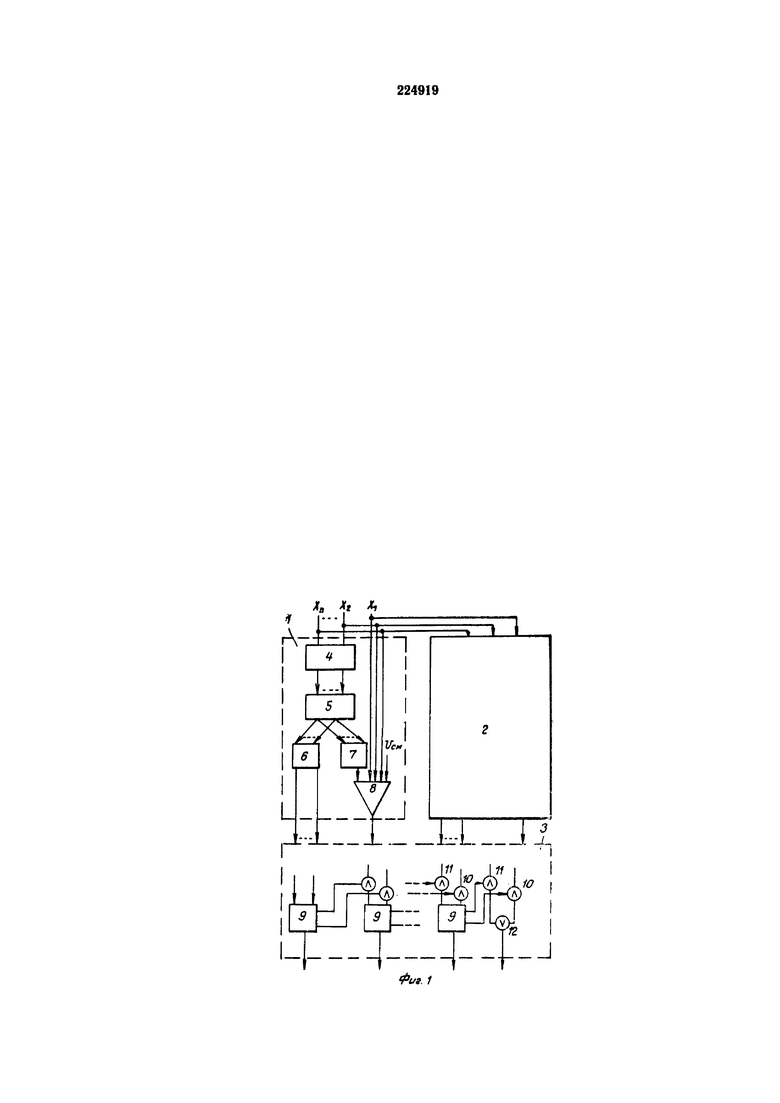

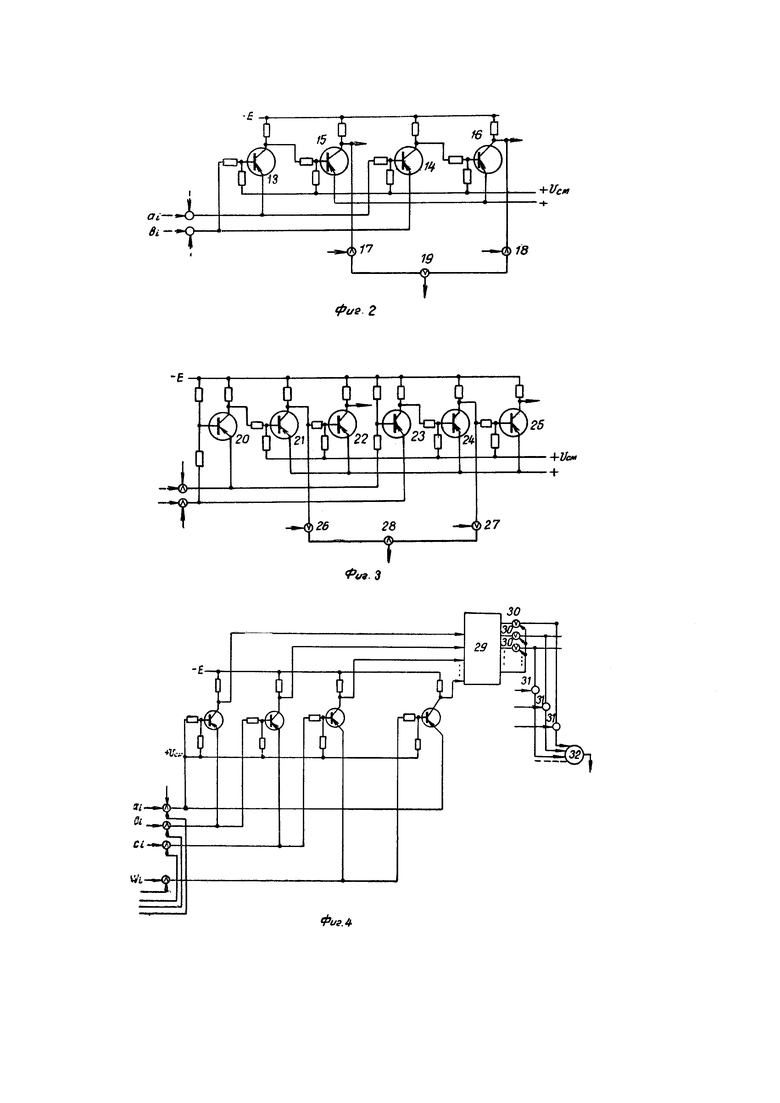

На фиг. 1 изображена структурная схема описываемого преобразователя; на фиг. 2 - разрядная схема выбора для амплитудно-позиционной схемы выбора максимума; на фиг. 3 - разрядная схема выбора амплитудно-позиционной схемы выбора минимума; на фиг. 4 - разрядная схема выбора для амплитудно-позиционной логической схемы со многими входами.

Преобразователь содержит генераторы образующих функций 1 и 2, логический блок 3, амплитудный дискриминатор 4, дешифраторную схему 5, матрицы 6 и 7 сопротивлений, аналоговый усилитель-сумматор 8, разрядные схемы выбора 9, вентили 10 и 11 (схемы выбора минимума) и аналоговую схему выбора максимума 12.

Схема (фиг. 1) состоит из амплитудно-позиционных генераторов образующих функций 1 и 2, на вход которых подано амплитудно-позиционное представление аргумента X: Xn, …, Х2, Х1, присоединенных к логическому блоку 3, состоящему из амплитудно-позиционных схем для выбора максимума или минимума (логических схем).

Рассматриваемая схема представляет собой функциональный преобразователь одной переменной, воспроизводящий функции Y=F(X). Образующими функциями при этом являются функции вида:

A=K1X+C1

B=K2X+C2,

где X - аргумент, А и В - образующие функции, K1, K2, C1 и С2 - постоянные.

Каждый амплитудно-позиционный генератор образующих функций состоит из амплитудного дискриминатора 4(n-1) старших разрядов аргумента, соединенного через дешифраторную схему 5 с матрицами 6 и 7 сопротивлений и аналогового усилителя - сумматора 8. В матрице 6 задаются n-1 старших разрядов образующей функции (каждый разряд задается отдельным сопротивлением, матрица 6 имеет n-1 выходов), а в матрице 7 эти же n-1 разрядов образующей функции задаются с помощью одного сопротивления; матрица 7 имеет один (аналоговый) выход. Аналоговый усилитель-сумматор 8 воспроизводит функцию

а1=XnK1+…+X2K1+X1K1+C1-V,

где а1 - младший разряд амплитудно-позиционного представления образующей функции A, XnK1+X2K1+X1K1+C1=A - образующая функция А в аналоговой форме, где V - выходное напряжение матрицы 7, т.е. аналоговый эквивалент n-1 старших разрядов амплитудно-позиционного представления образующей функции А.

При необходимости воспроизвести функцию нескольких переменных образующие функции (для двух переменных) имеют вид: A=k1X+C1+k2Y+C2, где X и Y - аргументы, и образуются присоединением нескольких амплитудно-позиционных генераторов ко входам амплитудно-позиционного сумматора.

В логический блок 3 входят амплитудно-позиционные логические схемы выбора максимума или минимума. Блок 3 представлен в виде амплитудно-позиционной схемы выбора максимума с двумя входами. Схема состоит из ряда разрядных схем выбора 9, на вход которых подаются соответствующие разряды образующих функций через вентили 10 и 11 (аналоговые схемы выбора минимума), управляемые выходами схем выбора предыдущих разрядов.

Разрядная схема выбора для амплитудно-позиционной схемы максимума (фиг. 2) содержит усилители на полупроводниковых триодах 13 и 14 (фиг. 2), работающие в ключевом режиме. Выход разряда ai одной образующей функции присоединен к эмиттеру триода 13 и (через сопротивление) - к базе триода 14, а разряд bi другой образующей функции - к эмиттеру триода 15 и к базе триода 13 (принято, что а>0; b>0).

Если А>В (при открытых вентилях на входе), триод 13 открыт, а триод 14 закрыт, если А<В, то наоборот, триод 13 закрыт, а триод 14 открыт. На базы обоих триодов подано положительное постоянное напряжение Uсм через сопротивление, рассчитанное так, чтобы при А=В оба триода 13 и 14 были закрыты. Выходы усилителей на триодах 13 и 14 присоединены к инверторам на триодах 15 и 16, выходы которых поданы на аналоговые схемы 17 и 18 выбора минимума. На другой вход каждой из схем 17 и 18 поданы значения образующих функций в i-ом разряде ai и bi. Выходы схем 17 и 18 являются входами аналоговой схемы выбора максимума 19, на выходе которой образуется i-ый разряд результирующей функции.

Выходы усилителей-инверторов управляют также входными вентилями схемы выбора последующего разряда.

Структура амплитудно-позиционной схемы выбора минимума (фиг. 3) отличается от структуры амплитудно-позиционной схемы выбора максимума (фиг. 2) только тем, что вместо аналоговой схемы выбора максимума 12 включается аналоговая схема выбора минимума.

Схема (фиг. 3) содержит полупроводниковые триоды 20-25, аналоговые схемы 26 и 27 выбора максимума и аналоговую схему выбора минимума 28.

Фиг. 3 имеет следующие отличия от фиг. 2: на базы триодов 20 и 21 подано отрицательное смещение (от постоянного напряжения - Е) для того, чтобы при А=В оба триода были открыты. Аналоговые схемы 17 и 18 выбора минимума (см. фиг. 2) заменяются аналоговыми схемами 26 и 27 выбора максимума (см. фиг. 3), а схема выбора максимума 19 (см. фиг. 2) - аналоговой схемой выбора минимума 28 (см. фиг. 3); вводятся инверторы на триодах 24 и 25, выходы которых связаны с вентилями на входе разрядной схемы выбора следующего разряда.

При воспроизведении функциональных зависимостей часто встречается необходимость в схемах выбора максимума или минимума с числом входов больше двух. Разрядная схема выбора для амплитудно-позиционной логической схемы с многими входами (фиг. 4) содержит дешифраторную схему 29, включающую инверторы входных сигналов; схемы «ИЛИ» 30, аналоговые логические схемы 31 (схема выбора минимума - в амплитудно-позиционной схеме выбора максимума, максимума - в амплитудно-позиционной схеме выбора минимума); аналоговую логическую схему 32 со многими входами (схема выбора максимума для амплитудно-позиционной схемы выбора максимума, минимума - для амплитудно-позиционной схемы выбора минимума).

Схема (фиг. 4) включает ряд полупроводниковых триодов (по числу входов амплитудно-позиционной логической схемы). На эмиттеры и базы этих триодов в определенном порядке через вентили, управляемые от схемы выбора предыдущего разряда, поданы разряды входных амплитудно-позиционных величин. Все триоды имеют смешение в цепи базы от постоянного напряжения для того, чтобы при равенстве напряжений, поданных на базу и на эмиттер, каждый триод был закрыт. Коллекторы триодов соединяются с дешифраторной схемой 29. Число выходов дешифратора на единицу больше числа входных величин в амплитудно-позиционной логической схеме. Каждый выход дешифратора соответствует определенному соотношению между выходными величинами.

Выход дешифратора, соответствующий состоянию, когда все триоды закрыты, связывается схемами «ИЛИ» 30 с остальными выходами дешифратора.

При ai=bi=ci=ωi на всех выходах схем «ИЛИ» будет высокий уровень отрицательного напряжения, а в остальных случаях этот уровень будет только на одном из выходов схем «ИЛИ». Выходы схем «ИЛИ» управляют входными вентилями следующей разрядной схемы выбора и присоединены ко входам аналоговых логических схем 31, на другие входы которых поданы i-тые разряды ai, bi, ci и ωi амплитудно-позиционных величин. Выходы логических схем 31 присоединены ко входам аналоговой логической схемы 32.

Схему (фиг. 4) целесообразно использовать при необходимости выбора между многими амплитудно-позиционными величинами.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРО-АНАЛОГОВОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1969 |

|

SU232616A1 |

| ЦИФРО-АНАЛОГОВОЕ УСТРОЙСТВО | 1968 |

|

SU217750A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| МАЛОГАБАРИТНЫЙ РАДИОЛОКАТОР ТРАНСПОРТНОГО СРЕДСТВА | 1997 |

|

RU2117964C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Сцинтилляционный позиционно-чувствительный детектор | 1988 |

|

SU1562870A1 |

| Устройство для моделирования нелинейных функций | 1980 |

|

SU922793A1 |

| ПРИЕМНИК СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1997 |

|

RU2118054C1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1979 |

|

SU1840116A2 |

| ИНТЕГРАЛЬНЫЙ МАГНИТОТРАНЗИСТОРНЫЙ ДАТЧИК С ЦИФРОВЫМ ВЫХОДОМ | 2009 |

|

RU2437185C2 |

1. Функциональный преобразователь, содержащий амплитудные дискриминаторы, дешифраторные схемы, матрицы сопротивлений, аналоговые усилители-сумматоры, аналогоговые логические схемы отличающийся тем, что, с целью увеличения точности устройства, он содержит амплитудно-позиционные генераторы образующих функций, состоящие из последовательно соединенных амплитудного дискриминатора, дешифратора, матриц сопротивлений и аналогового усилителя сумматора, и логический блок, включающий амплитудно-позиционные логические схемы, причем каждая из них содержит разрядные схемы выбора, в которых выход разряда каждой входной величины подсоединен к эмиттеру одного триода-усилителя и базе другого, а выходы этих усилителей подключены через триоды-инверторы к вентилям на входе следующей разрядной схемы выбора и к вентилям, пропускающим соответствующие разряды входных величин на вход аналоговой логической схемы.

2. Преобразователь по п. 1, отличающийся тем, что, с целью упрощения схемы, в нем выходы триодов разрядных схем выбора амплитудно-позиционных логических схем подключены к дешифратору, выходы которого через схемы «ИЛИ» подключены к вентилям.

Авторы

Даты

1968-12-10—Публикация

1967-06-09—Подача