Известны цифро-аналоговые устройства, содержащие аналоговые сумматоры и пороговые Схемы. Предложенное устройство отличается от известных тем, что оно содержит амплитуднопозиционные сум маторы, в которых пороговые схемы переноса включены между разрядными аналоговыми сумматорами, и амплитудные .восстановители, включенные между амплитудно-позиционными сумматорами и измерительньши приборами, а также тем, что Пороговая схема соединена со схемой выбора максимума старших разрядо.в слагаемых, а между каждыми двумя соседними разрядными аналоговыми сумматорами в.ключены также две .пороговые схемы, имеющие общие .входы с разрядным сумматором младшего из двух соседних разрядов. Это повышает точность и бьгстродействие устройства, а также расширяет класс решаемых задач. Па фИг. 1 изображена структурная схема амнлитудно-нозиционного сумматора, предназначенного для сложения двух положительных трехразрядных чисел, представленных в амллитудно-позиционной форме. ры соответствен.но 1-го, 2-го и 3-го разрядов, 4, 5, 6 - пороговые элементы, 7, 8, 9, 10 - разряды суммы. Пороговые элементы 4, 5 v( 6 выключены .между аналоговыми усилителями-сумматорами 1, 2 W. 3. Па 1ВХО.Д /каждого порогового элеiMeHTa подаются соответствующие разряды слагаемых величии, опорно-е напряжение, а также .выходное напряжение предыдущего порогового элемента. При превышении выхо.днаго напряжения разрядного усилителя-.сумматора над некоторым предельным Напряжением, принятым за единицу, пороговый элемент обеспечивает вычитание единицы из выходного напряжения этого разрядного усилителя и одновременное прибавление к выходному напряжению следующего разрядного усилителя (старшего разряда) напряжения, равного 0,1. Старш.ий разряд 10 суммы образуется выходом порогового элемента предыдущего разряда. Аналогичным образом быть построен сумматор с числом разрядо.в больше трех (увеличивается число усилителей-сумматоров и .пороговых элементов). Для сложения трех и более чисел в амплитудно-позиционной форме следует использовать .последовательное соединение нескольких амплитудно-позиционных сумматоров.,

Описанные выше сумматоры предназначены для суммирования только положительных (или только отрицательных) чисел.

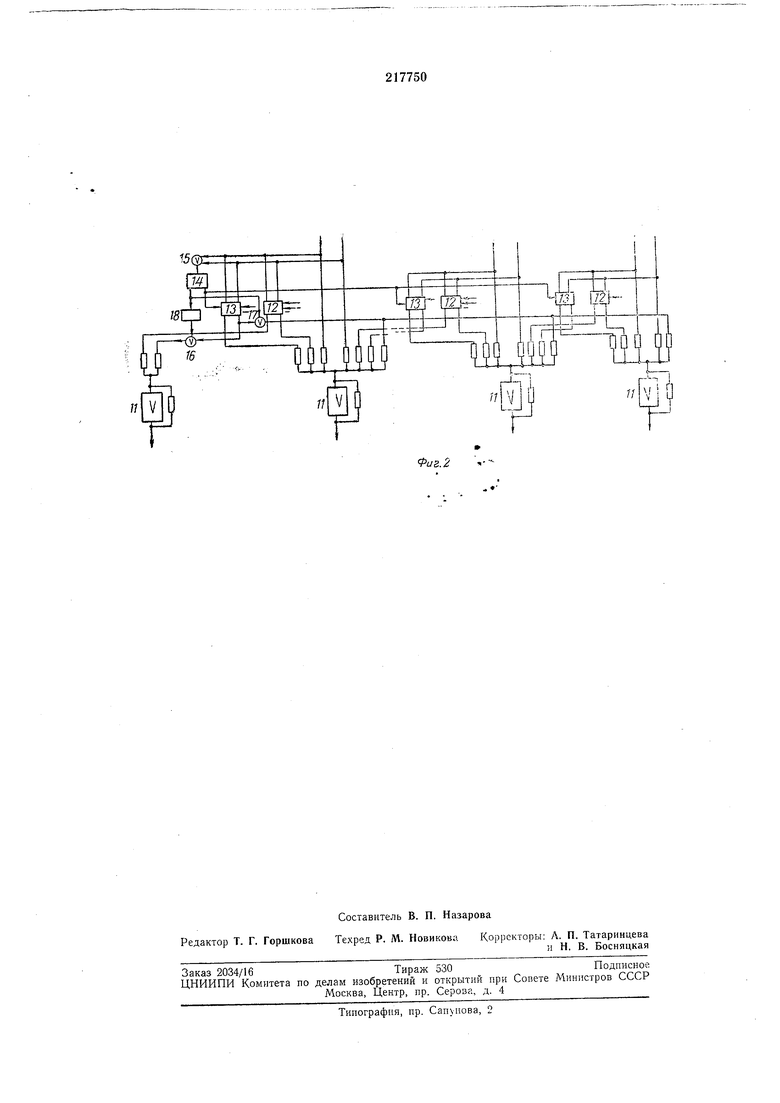

Для устранения этого недостатка схама амплитудно-позиционного сумматора видоизменяется , чтобы он был способен, производить как сложение, так и вычитание двух чисел, положительных или отридательных (фиг. 2).

Условные обозначения к фиг. 2:

Л - разрядные усилители-сумматоры; 12- пороговые элементы, обеспечивающие леренос на сложение; /J-пороговые элементы, обеспечивающие перенос на вычитание; 14-порого1вый элемент, обеспечивающий изменение опорного напряжения пороговых элементов 13; 15, 16, 17 - логические схемы (выбор максимума); 18 - инвертор.

Младшие разряды слагаемых и суммы представлены напряжением, амплитуда которого может изменяться непрерывно. В остальных разрядах слагаемых и суммы амплитуда напряжения может принимать одно из допустимых |3начаний.

Амплитудно-позиционный сумматор состоит из ряда разрядных усилителей-сумматоров 1J, между которыми включены два пороговых элемента, на входы которых подаются младщие из соседних разрядов слагаемых. Пороговый элемент 12 осуществляет перенос на сложение, а элемент 13 - на вычитание. При этом у пороговых элементов, осуществляющих перенос на сложение, опорно е напряжение постоянно и равно минус 1, а у порого1вых элементов, осуществляющих перенос на вычитание, опорным напряжением является выходное напряжение специального порогового элемента М.

Па вход порогового элемента 14 подается напряжение с выхода логической схемы 15 (выбор максимуса), имеющей выходами старшие разряды слагаемых. Выход порогового элемента 12 старщего разряда через логическую ключевую схему 17, управляемую выходом порогового элемента 14, присоединен ко

входам разрядных усилителей-сумматоров разрядов п... 2, 1, « разрядам п... 2 - с коэффициентом передачи 0,9, а к младшему разряду 1 -,с коэффициентом 1 ,а через логиче5 скую ключевую схему 16, управляемую выходом инвертора 18 сигнала порогового злемента 14, присоединен ко входу усилителя-сумматора старшего разряда -|-1. Для переноса на сложение входы пороговых элементов 12 каждого разряда присоединены КО входу усилителя-сумматора этого разряда с коэффициентом передачи 1, а выходы - ко входам усилителя-сумматора и порогового элемента следующего старшего

5 разряда с коэффициентом передачи 0,1.

Для переноса на вычитание входы пороговых элементов 13 каждого разряда присоединены ко входу усилителя-сумматора этого разряда (коэффициент передачи 1), а выходы пороговых элементов - .ко входам усилителя-сумматора и порогового элемента 13 следующего младшего разряда (коэффициент передачи равен 0,1).

Предмет изобретения

1.Цифро-аналоговое устройство, содержащее аналоговые сумматоры и пороговые схемы, отличающееся тем, что, с целью повышения точности и быстродействия устройства, оно содержит амплитудно-позиционные сумматоры, в которых пороговые схемы переноса включены между разрядными аналоговыми сумматорами, и амплитудные восстановители, включенные между амплитудно,-позиционными сумматорами и измерительными приборами.

2.Устройство по п. 1, отличающееся тем, что, с целью расширения класса решаемых задач, пороговая схема соединена со схемой

0 выбора максимума старших разрядов слагаемых, а между каждыми двумя соседними разрядными аналоговыми сумматорами включены также две пороговые схемы, имеющие общие входы ic разрядным сумматором младшего из двух соседних разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРО-АНАЛОГОВОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1969 |

|

SU232616A1 |

| Оптоэлектронный десятичный сумматор | 1978 |

|

SU840895A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2000 |

|

RU2173934C1 |

| СПОСОБ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2109325C1 |

| Устройство для суммирования чисел | 1984 |

|

SU1183959A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Параллельно-последовательный сумматор-вычитатель старшими разрядами вперед на нейронах | 2019 |

|

RU2708501C1 |

| Разрядно-аналоговый сумматор | 1988 |

|

SU1589293A1 |

| Преобразователь код-напряжение | 1984 |

|

SU1197084A1 |

Даты

1968-01-01—Публикация