Известны запоминающие устройства для аиалоговых сипналов, содержащие накопительные коиденсаторы, входные ключевые схемы, ключевые схемы коррекции, дискретную следящую систему коррекции с последовательныМ опросом накопительных конденсаторов, олок выбора адресов и аналогово-цифровой преобразователь со схемой сравнения, сумматором и декодирующей схемой.

li предлагаемом устройстве система коррекции содержит дополнительный входной ключ, связанный с одним из входов схемы сравнения, выход которой соединен с ее вторым входом через блок подбора цифрового эквивалента, я декодирующую схему, подключенную к одному из входов сумматора. Второй вход сумматора соединен с источником постоянного напряжения. Через выходной ключ сум-матор связан параллельно с ключевыми схемами коррекции, управляющие .входы которых соединены с распределителем.

Это упрощает устройство.

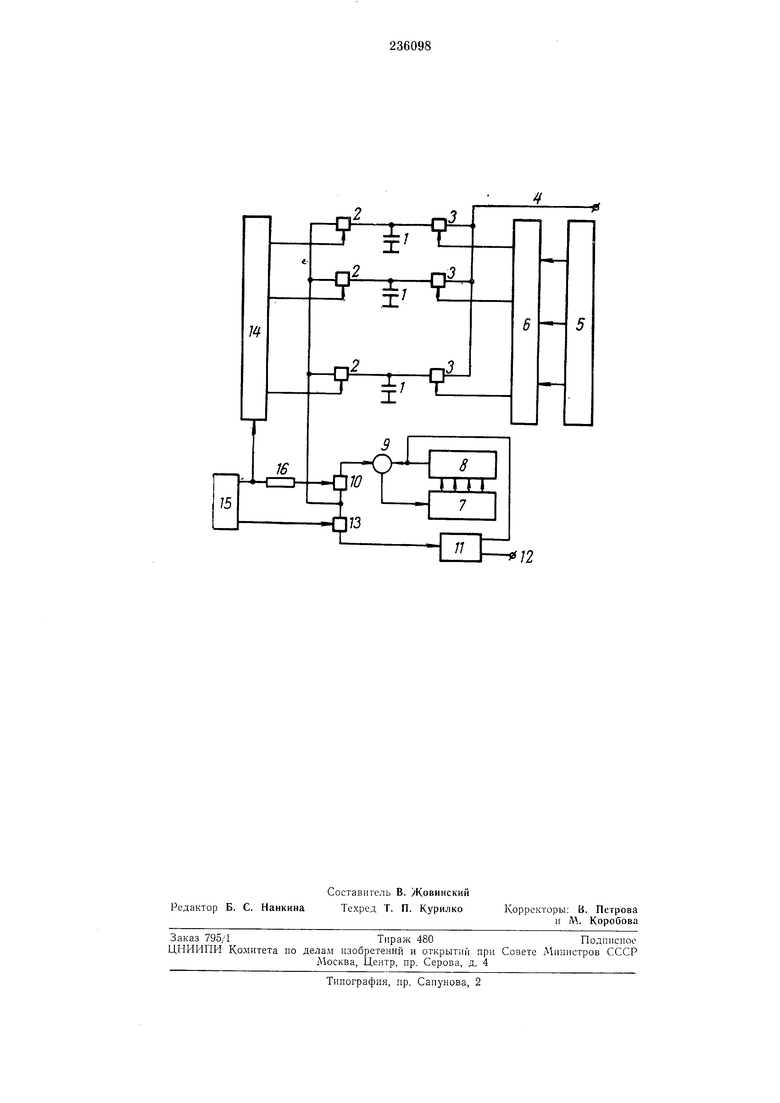

На чертеже показаиа блок-схема описываемого устройства.

Элементы памяти включают накопительные конденсаторы 1, ключевые схемы коррекции 2, ключи 3 записи-считывания, соединяющие конденсаторы / с шиной 4 записи-считывания.

6, который управляет ключами о записи-считывания соответствующих эле.ментов памяти. Дискретная следящая схема коррекции содержит аналогово-цифровон преобразователь,

состоящий из блока / подбора цифрового эквивалента, декодирующей схемы и схемы сравнения 9, один из входов которой через дополнительный входной ключ W схемы коррекции соединен с ключевыми схемами коррекдни 2, а другой - с декодирующей схемой. Напряжением на декодирующей схеме 8 управляет блок 7 подбора цифрового эквивалента, соединенны с выходом схемы сравнения 9. На один вход сумматора 11 по шине 12 подается постоянное напряжение, равное половине шага квантования преобразователя, а другой вход соединен с выходом декодирующей схемы 8, причем выход сумматора через выходной ключ 13 подключен к ключам коррекции 2. Выходные цепи распределителя 14 управляют ключами коррекции 2. Один из выходов задающего генератора 15 соединен с распределителем 14 и через линию задержки 16 - с входным ключом 10, а другой выход

управляет работой выходного ключа 13.

При работе запоминающего устройства следует различать записи, считывания и коррекции хранимой информации.

iBpCMCiuio дешифратор адреса f; вырабатывает сигнал, открывающий ключ ,J заинси-считываKiiH :),ie.ieuTa памяти, соотвсчствующего адресу, предварительио занесенному в регистр ад|)еса 5, и конденсатор 1 этого элемента памяти заря/кается до папря/ксиня, )авного входному.

В режиме счптывапня запоминающее уетpoiicTiio работает аналогично, и по Н1ипе за1Л1си-(чит1 1 вапия сиимаетси иаиря/кенпе, соответстиуюп1,ее напряжению на конденсаторе / выбр.анного эле.меита памяти.

В режиме коррекипп копдеисаторы / элемегггов 11Р:Мятп поочередно подключаются к схеме коррекнни. Коррекнпя заряда каждого отде;;ьно1-о конденсатора осун,ествляется в два этана: нериод отработк и период коррекции.

Период отработки начинается после того, как оче|)едпо1 1 зшнденсатор / эле.мепта падштн подключается . распределителе 14 к ехеме коррекднн. При этом через Т5рел1я, определяемое линией задержки/(7j открываетея входной 10 схем1з1 коррекции, и иапряжеиие корректнр ем()го конденсатора / поступает на вход ехемы сравиепня 5. Выходной ключ 13 в этот Aio ieirr закрьгг, поско.тьку снгналы на выходнвкх задающего генератора 15 едвинуты во времени. Схема сравнения 9 вырабатв1вает сигнал, управляюндий блоком 7 подбора цифрового эквивалента до тех пор, пока напряжение на выходе декодирующей схе.мы 8 аналогово-и.нфрового п.реобразователя не етанет равным входно: 1у. Режим работв преобразователя вв бирается таки.м образом, что нанряженне на конденсаторе / ноддержнвае1ея еистемой коррекгии с иогре1нпостьго, не г ревышающей половину И1ггсрвала кваитоваПИЯ.

В период коррекции открывается ключ (ключ 10 закрывается), и напряжение с BBIXOда сумЛ1атора 11 поступает на соответетвуюн;нй элемент намяти. Конденсатор / нри это.м заряжается до напряжепия, равиого вв|ходио:.iy напряжению сумматора 11.

Период подключения кондесаторов / к схеме коррекции выбирается таким образом, чтобы за время подключения конденсатор не из.1енил своего заряда па велпчипу, б6лвп1ую ноло1Н1ны шага квантования.

Таким образом, ипформацця, заппсаниая в 3ai OL iHHaiOH ieM устройстве, непрерывно поддерживается между определенными дискретНВ1МИ уровнями ц может хранитвся неограниченно долгое время.

Пред м е т и з о б р е т е и и я

Запомииающее устройство для аналоговых

сигналов, содержащее пакопителв п 1е кондеисаторв, входные ключевые схемвт, ключевв1е схе.мв коррекции, дискретную следящую систему коррекции с цоеледователвнв1м опросом г:аконнтелвнв1х конденсаторов, блок выбора

адресов и аналогово-цифровой преобразователв со схемок сравнения, сумлттором li декоднруюц.1ей схемой, отличающееся тем, что, с целью его упрощепня, снстема коррекши содержит дополнительный входноГ ключ, связанпый е одним из входов схе.мы сравнення, выход которой соединен с ее вторыл входом через блок подбора цифрового эквивалента, и декодпруюнтую схему, подключенную к одному из входов сумматора, второй вход которого

соединен е неточником постояииого ианряження, сумматор через выходной ключ связан н.араллелвно с ключевыми коррекции, управляющие входы которых еоединеиы с распределителем.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ГЕОМЕТРИЧЕСКИХ НЕРОВНОСТЕЙ КОЛЕСНЫХ ПАР ПОДВИЖНОГО СОСТАВА12 | 1973 |

|

SU384711A1 |

| СЛЕДЯЩАЯ ЛИНИЯ ЗАДЕРЖКИ | 1993 |

|

RU2085026C1 |

| Устройство для контроля интегральных схем | 1985 |

|

SU1290522A1 |

| Цифроаналоговая следящая система | 1986 |

|

SU1405025A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU748511A1 |

| Запоминающее устройство | 1977 |

|

SU661610A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU864341A1 |

| Динамическое запоминающее устройство | 1976 |

|

SU714501A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

Даты

1969-01-01—Публикация