сл

о

IN СЛ

Фг/9.1

Изобретение относится к автоматике и предназначено для использования в системах с числовым программным управлением, и с электродвигателем noc тоянного тока без тахогенератора

Цель изобретения - повьшение быст- родейсТвия, статической точности гулирования и устойчивости работы системы.

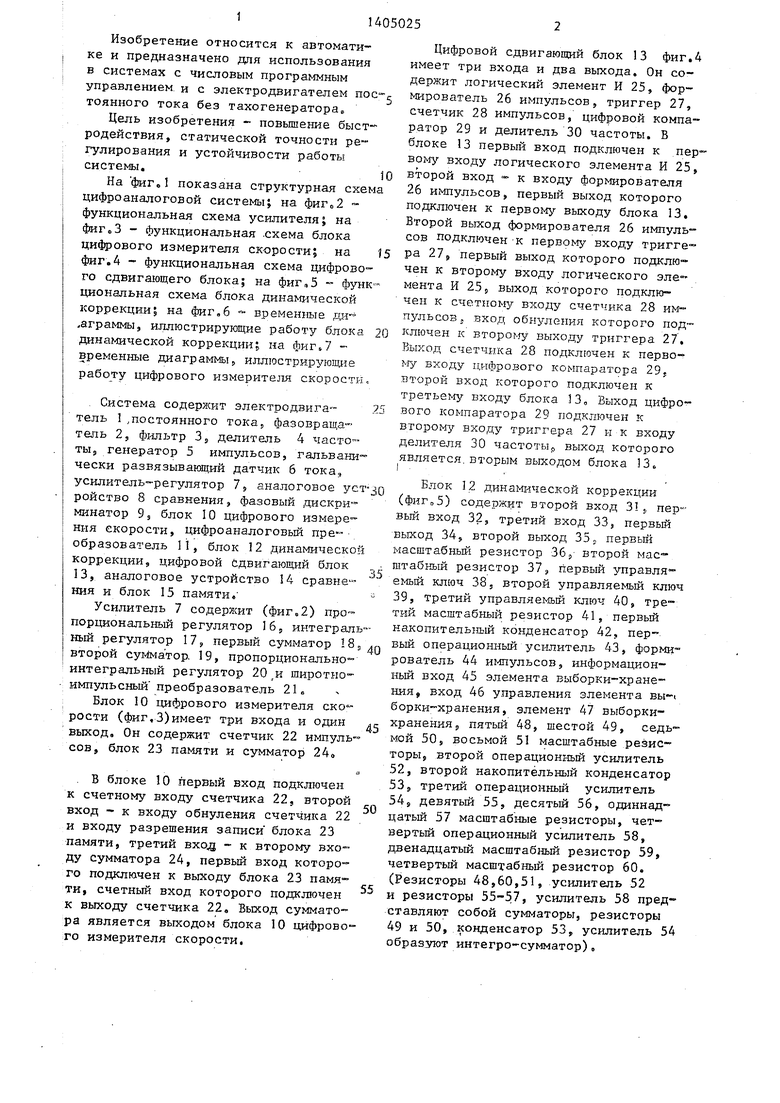

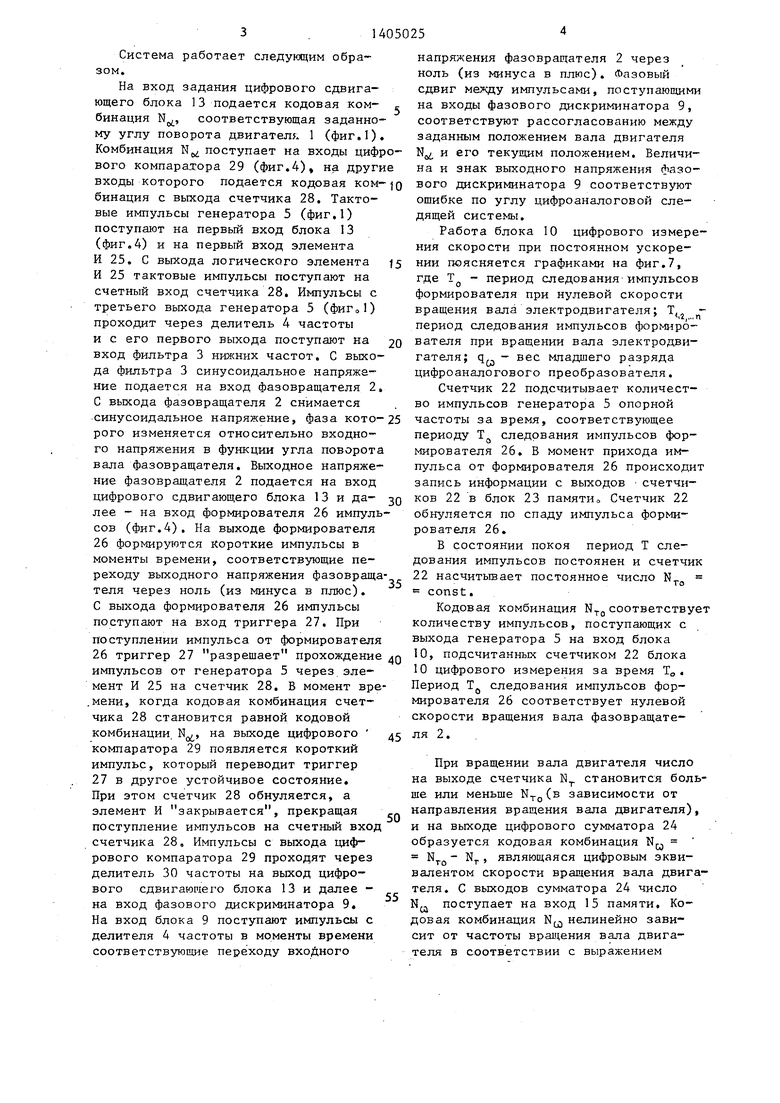

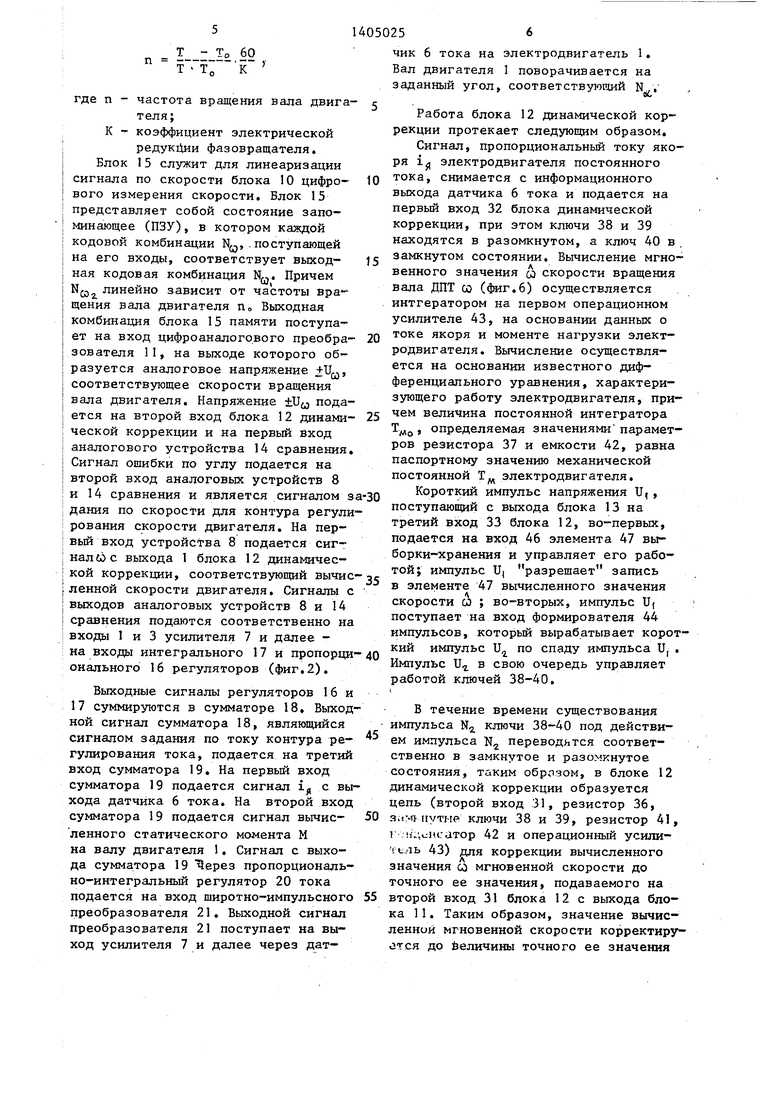

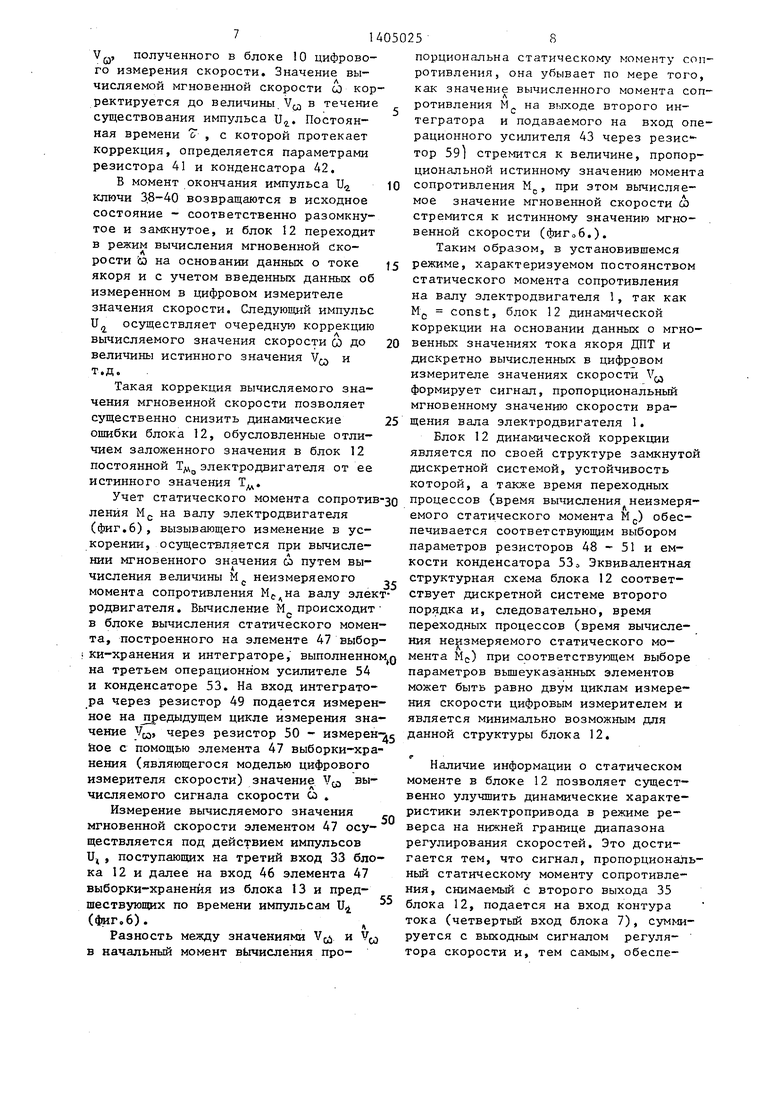

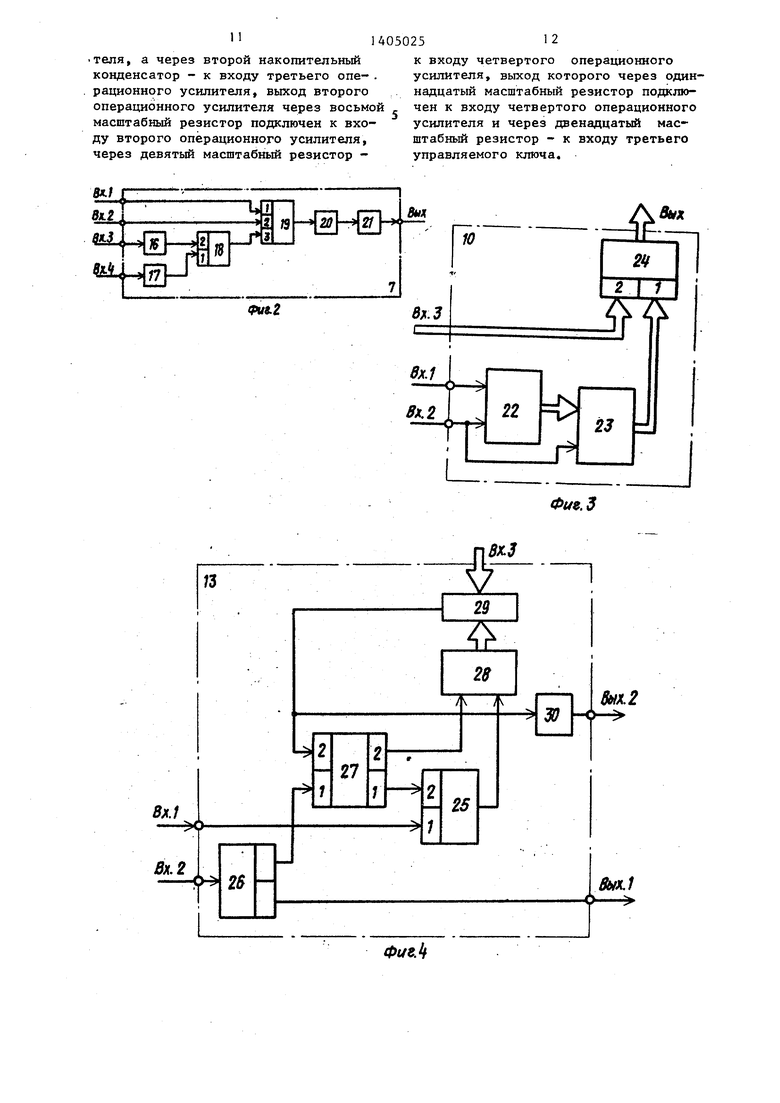

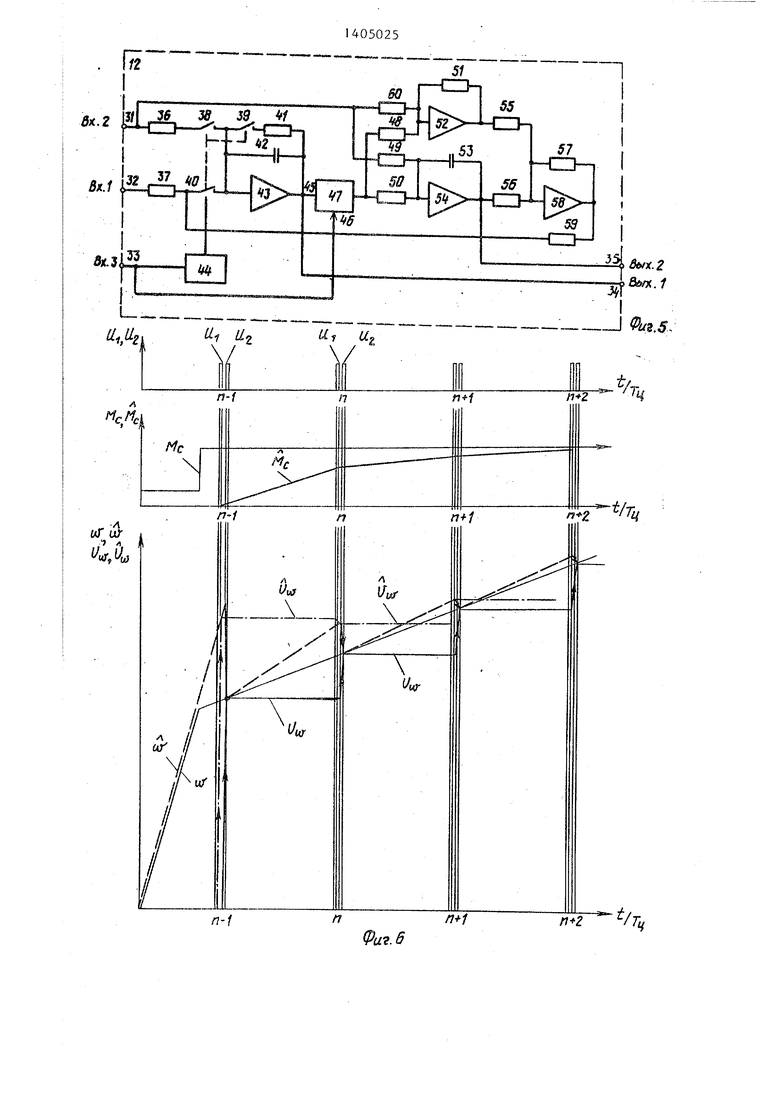

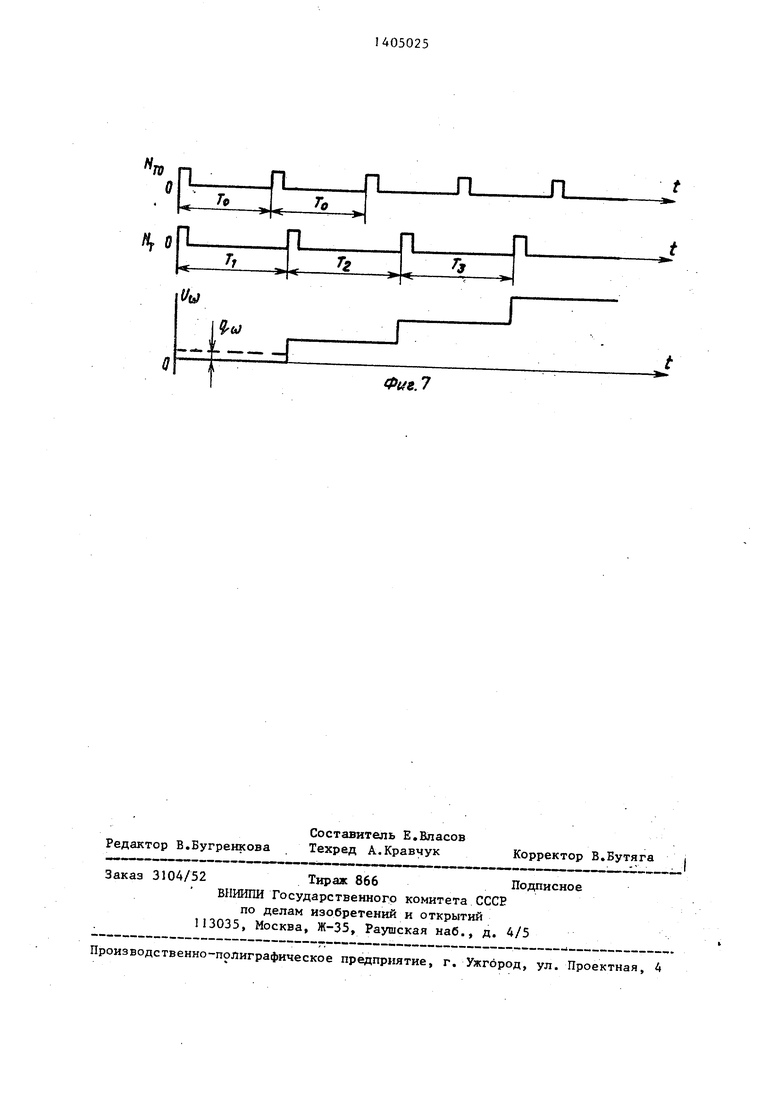

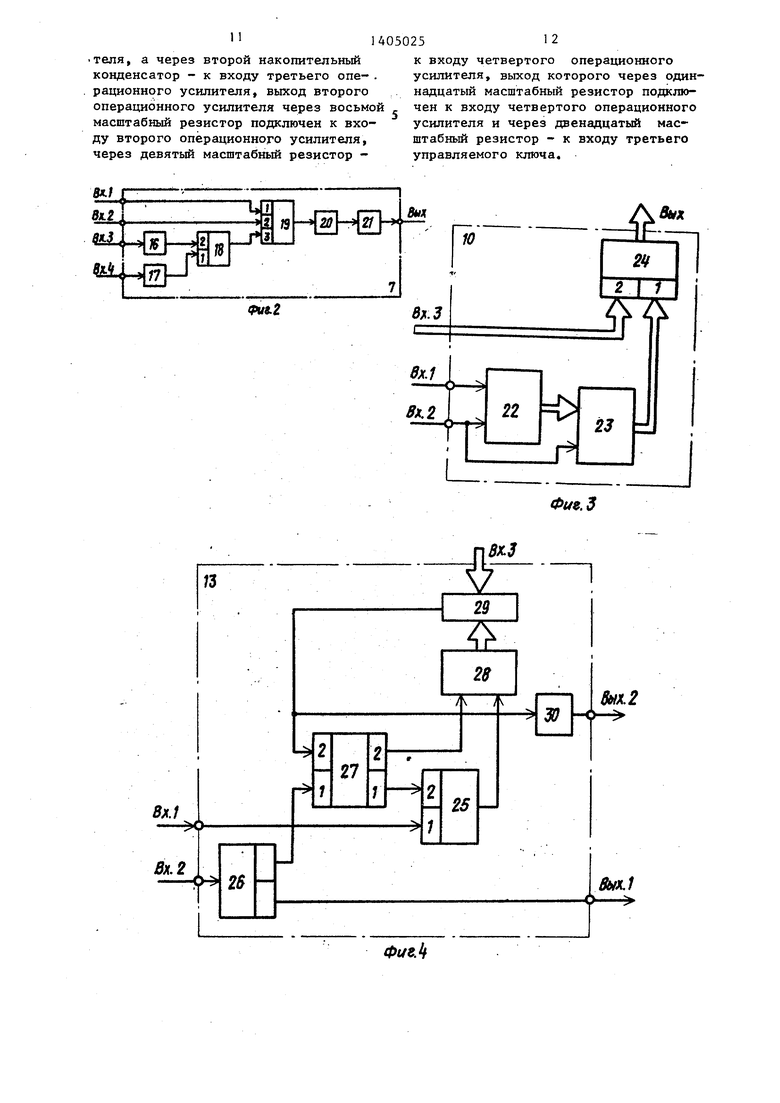

На фиго показана структурная схем цифреаналоговой системы; на фиг„2 - функциональная схема усилителя; на фиГоЗ - функциональная .схема блока цифрового измерителя скорости; на фиг.4 функциональная схема цифрового сдвигающего блока; на функциональная схема блока динамической коррекции; на фиг,б временные .аграммы, иллюстрирующие работу блока динамической коррекции; на фиг,7 -- временные диаграммы иллюстрирующие цифрового измерителя скор ости

. Система содержит электродвига- тель 1 ,постоянного тока., фазовращатель 2, фильтр Зэ делитель 4 часто- тыр генератор 5 импульсов, гальванически развязывакнций датчик 6 тока, усилитель-регулятор 1, аналоговое уст ройстБО 8 сравнения, фазовый дискриминатор 9s блок 10 цифрового измерв НИН скорости, цифроаналоговьй пре- образователь П, блок 12 динамической коррекции, цифровой Сдвигающий блок 13, аналоговое устройство 14 сравнв ния и блок 15 памяти «

Усилитель 7 содержит () пропорциональный регулятор 16, интегральный регулятор 17, первый сумматор -8s второй cyi-iMBTOp. 19, пропорционально™ интегральный регулятор 20,и широтыо- импульсный преобразователь 21

Блок 10 цифрового измерителя рости (фиг,3)имеет три входа и один выход. Он содержит счетчик 22 импуль™ сов, блок 23 памяти и сумматор 24

. В блоке 10 первый вход подключен к счетному входу счетчика 22, второй вход - к входу обнуления счетчшса 22 и входу разрешения записи блока 23 памяти, третий вход - к второму входу сумматора 24, первый вход которого подключен к выходу блока 23 памяти, счетный вход которого подключен к выходу счетчика 22. Выход суммато ра является выходом блока 10 цифрового измерителя скорости.

i-

Q

5 0

5 о .

о

0

5

Цифровой сдвигающий блок 13 фиг,4 имеет три входа и два выхода. Он содержит логический элемент И 25, формирователь 26 импульсов, триггер 27, счетчик 28 импульсов, цифровой компаратор 29 и делитель 30 частоты. В блоке 13 первый вход подключен к первому входу логического элемента И 25, второй вход « к входу формирователя 26 импульсов, первый выход которого подключен к первому выходу блока 13, Второй выход формирователя 26 импульсов подключен -к первому входу триггера 27, первый выход которого подключен к второму входу логического эле мента И 25, выход которого подклю™ чен к счетному входу счетчика 28 импульсов, вход обнуления которого подключен к втopo fy выходу триггера 27. Выход счетчика 28 подключен к первому входу цифрового компаратора 29, второй вход которого подключен к третьему входу блока 33, Выход цифрового компаратора 29 подключен к второму входу триггера 27 и к входу делителя 30 частоты,, выход которого является, вторым выходом блока 3.

Блок 12 динамической коррекции (фиг,5) содержит второй вход 31 ,, первый вход 32, третий вход 33, первый выход 34, второй выход 35 первьй масштабный резистор 36, второй мас- штабиый резистор 37, первый управляемый ключ 38 5 второй управляемьш ключ 39, третий управляемый ключ 40, третий масштабный резистор 41, первый накопитель}а1й конденсатор 42, пер- вьш операционный yci-шитель 43, формирователь 44 импульсов, информационный вход 45 элемента выборки-хранения, вход 46 управления элемента борки-хранения, элемент 47 выборки- хранения, пятый 48, шестой 49, седьмой 50, восьмой 51 масштабные резис торы, второй операционный усилитель

52,второй накопительный конденсатор

53,третий операционный усилитель

54,девятый 55, десятый 56, одиннад- цатьш 57 масштабные резисторы, четвертый операционный усилитель 58, двенадцатый масштабный резистор 59, четвертый масштабный резистор 60. (Резисторы 48,60,51, усилитель 52

и резисторы 55-57, усилитель 58 пред ставляют собой сумматоры, резисторы 49 и 50, конденсатор 53, усилитель 54 образуют интегро-сумматор) ,

Система работает следующим образом.

На вход задания цифрового сдвигающего блока 13 подается кодовая комбинация Nj, соответствующая заданному углу поворота двигателе. 1 (фиг.1). Комбинация N поступает на входы цифрвого компараюра 29 (фиг.4), на други входы которого подается кодовая KOMбинация с выхода счетчика 28. Тактовые импульсы генератора 5 (фиг.) поступают на первый вход блока 13 (фиг,4) и на первый вход элемента И 25. С выхода логического элемента И 25 тактовые импульсы поступают на счетный вход счетчика 28. Импульсы с третьего выхода генератора 5 (фиГоО проходит через делитель 4 частоты и с его первого выхода поступают на вход фильтра 3 нижних частот. С выхода фильтра 3 синусоидальное напряжение подается на вход фазовращателя 2, С выхода фазовращателя 2 снимается синусоидальное напряжение, фаза кото- рого изменяется относительно входного напряжения в функции угла поворота вала фазовращателя. Выходное напряжение фазовращателя 2 подается на вход цифрового сдвигающего блока 13 и да- лее - на вход формирователя 26 импульсов (фиг.4). На выходе формирователя 26 формируются Короткие импульсы в моменты времени, соответствующие переходу выходного напряжения фазовращателя через ноль (из минуса в плюс). С выхода формирователя 26 импульсы поступают на вход триггера 27. При поступлении импульса от формирователя

26триггер 27 разрешает прохождение импульсов от генератора 5 через элемент И 25 на счетчик 28. В момент вре,мени, когда кодовая комбинация счетчика 28 становится равной кодовой комбинации. NQ, на выходе цифрового компаратора 29 появляется короткий импульс, который переводит триггер

27в другое устойчивое состояние. При этом счетчик 28 обнуляется, а

элемент И закрывается , прекращая поступление импульсов на счетный вхо счетчика 28. Импульсы с выхода цифрового компаратора 29 проходят через делитель 30 частоты на выход цифрового сдвигающего блока 13 и далее - на вход фазового дискриминатора 9. На вход блока 9 поступают импульсы с делителя 4 частоты в моменты времени соответствующие переходу вхоДного

Q 5 0 5 0 о

5

0

5

напряжения фазовращателя 2 через ноль (из минуса в плюс). Фазовый сдаиг между импульсами, поступающими на входы фазового дискриминатора 9, соответствуют рассогласованию между заданным положением вала двигателя Nj и его текущим положением. Величина и знак выходного напряжения фазового дискриминатора 9 соответствуют ошибке по углу цифроаналоговой следящей системы.

Работа блока 10 цифрового измерения скорости при постоянном ускорении поясняется графиками на фиг.7, где Т - период следования-импульсов формирователя при нулевой скорости вращения вала электродвигателя; Т, - период следования импульсов формирователя при вращении вала электродвигателя; q - вес младшего разряда цифроаналогового преобразователя.

Счетчик 22 подсчитывает количество импульсов генератора 5 опорной частоты за время, соответствующее периоду Тд следования импульсов формирователя 26. В момент прихода импульса от формирователя 26 происходит запись информации с выходов счетчиков 22 в блок 23 памяти Счетчик 22 обнуляется по спаду импульса формирователя 26.

В состоянии покоя период Т следования импульсов постоянен и счетчик 22 насчитывает постоянное число N const.

Кодовая комбинация NT,., соответствует количеству импульсов, поступающих с выхода генератора 5 на вход блока 10, подсчитанных счетчиком 22 блока 10 цифрового измерения за время То. Период Tj, следования импульсов формирователя 26 соответствует нулевой скорости вращения вала фазовращателя 2.

При вращении вала двигателя число на выходе счетчика N становится больше или меньше N(в зависимости от направления вращения вала двигателя), и на выходе цифрового сумматора 24 образуется кодовая комбинация N N, являющаяся цифровым эквивалентом скорости вращения вала двигателя. С выходов сумматора 24 число N поступает на вход 15 памяти. Кодовая комбинация N(j нелинейно зависит от частоты вра1цения вала двигателя в соответствии с выражением

Т

f

- т

60

к

вала двига-

где n - частота вращения

теля; К - коэффициент электрической

редук1 ии фазовращателя. Блок 15 служит для линеаризации сигнала по скорости блока 10 цифро- вого измерения скорости. Блок 15 представляет собой состояние запоминающее (ПЗУ), в котором каждой кодовой комбинации N, . поступающей на его входу, соответствует выход- ная кодовая комбинация N. Причем N линейно зависит от частоты вращения вала двигателя По Выходная комбинация блока 15 памяти поступает на вход цифроаналогового преобра- зователя 11, на выходе которого образуется аналоговое напряжение +U(., соответствующее скорости вращения вала двигателя. Напряжение ±11 подается на второй вход блока 12 динами- ческой коррекции и на первый вход аналогового устройства 14 сравнения. Сигнал ощибки по углу подается на второй вход аналоговых устройств 8 и 14 сравнения и является сигналом з Дания по скорости для контура регулирования скорости двигателя. На первый вход устройства 8 подается сигнал we выхода 1 блока 12 динамической коррекции, соответствующий вычис ленной скорости двигателя. Сигналы с выходов аналоговых устройств 8 и 14 сравнения подаются соответственно на входы 1 и 3 усилителя 7 и далее - на входы интегрального 17 и пропорци онального 16 регуляторов (фиг,2),

Выходные сигналы регуляторов 16 и 17 суммируются в сумматоре 18, Выходной сигнал сумматора 18, являющийся сигналом задания по току контура ре- гулирования тока, подается на третий вход сумматора 19, На первый вход сумматора 19 подается сигнал i с выхода датчика 6 тока. На второй вход сумматора 19 подается сигнал вычис- ленного статического момента М на валу двигателя 1, Сигнал с выхода сумматора 19 lepes пропорционально-интегральный регулятор 20 тока подается на вход широтно-импульсного преобразователя 21, Выходной сигнал преобразователя 21 поступает на выход усилителя 7 и далее через датчик 6 тока на электродвигатель 1, Вал двигателя 1 поворачивается на заданный угол, соответствующий N,,,

ОС

Работа блока 12 динамической коррекции протекает следующим образом.

Сигнал, пропорциональньй току якоря i электродвигателя постоянного тока, снимается с информационного выхода датчика 6 тока и подается на первый вход 32 блока динамической коррекции, при этом ключи 38 и 39 находятся в разомкнутом, а ключ 40 в замкнутом состоянии. Вычисление мгновенного значения w скорости вращения вала ДПТ со (фиг,6) осуществляется интгератором на первом операционном усилителе 43, на основании данных о токе якоря и моменте нагрузки электродвигателя. Вычисление осуществляется на основании известного дифференциального уравнения, характеризующего работу электродвигателя, причем величина постоянной интегратора Т/ло 9 определяемая значениями параметров резистора 37 и емкости 42, равна паспортному значению механической постоянной Т, электродвигателя.

Короткий импульс напряжения U,, поступающий с выхода блока 13 на третий вход 33 блока 12, во-первых, подается на вход 46 элемента 47 выборки-хранения и управляет его рабо раэрешает

запись

той; импульс U)

в элементе 47 вычисленного значения

скорости со ; во-вторых, импульс U(

поступает на вход формирователя 44 импульсов, который вырабатывает корокий импульс и по спаду импульса U, Импульс и в свою очередь управляет работой ключей 38-40,

I

В течение времени существования импульса N. ключи 38-40 под действием импульса N переводятся соответственно в замкнутое и разомкнутое состояния, таким образом, в блоке 12 динамической коррекции образуется цепь (второй вход 31, резистор 36, SviNT} гутне ключи 38 и 39, резистор 41 г .1.;сисатор 42 и операционный усили- Htjib 43) для коррекции вычисленного значения со мгновенной скорости до точного ее значения, подаваемого на второй вход 31 блока 12 с выхода блока 11, Таким образом, значение вычисленной мгновенной скорости корректирется до йеличины точного ее значения

V, полученного в блоке 10 цифрового измерения скорости. Значение вычисляемой мгновенной скорости со корректируется до величинь. Vjj в течение существования импульса U.. Постоянная времени S , с которой протекает коррекция, определяется параметрами резистора 41 и конденсатора 42.

В момент окончания импульса U ключи 38-40 возвращаются в исходное состояние - соответственно разомкнутое и замкнутое, и блок 12 переходит в режим вычисления мгновенной скорости to на основании данных о токе якоря и с учетом введенных данных об измеренном в цифровом измерителе значения скорости. Следующий импульс

5 режиме, характеризуемом постоянством статического момента сопротивления на валу электродвигателя 1, так как М(, const, блок 12 динамической коррекции на основании данных о мгно-

и, осуществляет очередную коррекцию вычисляемого значения скорости О) до 20 венных значениях тока якоря ДПТ и величины истинного значения V и дискретно вычисленных в цифровом

измерителе значениях скорости V формирует сигнал, пропорциональный мгновенному значению скорости вра- 25 щения вала электродвигателя 1.

Блок 12 динамической коррекции является по своей структуре замкнутой дискретной системой, устойчивость которой, а также время переходных

Учет статического момента сопротив-зо процессов (время вычисления неизмеря- ленйя Mj; на валу электродвигателя емого статического момента М) обес- Сфиг.б), вызывающего изменение в ускорении, осуществляется при вьгчислет.д.

Такая коррекция вычисляемого значения мгновенной скорости позволяет существенно снизить динамические ошибки блока 12, обусловленные отличием заложенного значения в блок 12 постоянной электродвигателя от ее истинного значения Т.

НИИ мгновенного значения м путем вычисления величины М неизмеряемого

момента сопротивления валу элект родвигателя. Вычисление М происходит

35

печивается соответствующим выбором параметров резисторов 48 - 51 и емкости конденсатора 53 о Эквивалентная структурная схема блока 12 соответствует дискретной системе второго порядка и, следовательно, время

в блоке вычисления статического момен- переходных процессов (время вычисле- та, построенного на элементе 47 выбор- кия неизмеряемого статического мо- f ки-хранения и интеграторе, выполненном д мента М) при соответствующем выборе на третьем операционном усилителе 54 параметров вышеуказанных элементов и конденсаторе 53. На вход интеграто- может быть равно двум циклам измере- ра через резистор 49 подается измерен- ния скорости цифровым измерителем и нее на Jlpeдыдyщeм цикле измерения зна- является минимально возможным для чение V|, через резистор 50 - измерен-%с данной структуры блока 12, йое с помощью элемента 47 выборки-хранения (являющегося моделью цифрового измерителя скорости) значение VQ вычисляемого сигнала скорости О ,

Измерение вычисляемого значения мгновенной скорости элементом 47 осуществляется под действием импульсов

50

Наличие информации о статическом моменте в блоке 12 позволяет существенно улучшить динамические характеристики электропривода в режиме реверса на нижней границе диапазона регулирования скоростей. Это дости- Uj, поступающих на третий вход 33 бло- гается тем, что сигнал, пропорциональ- ка 12 и далее на вход 46 элемента 47 ный статическому моменту сопротивле- выборки-храненйя из блока 13 и пред- ния, снимаемый с второго выхода 35 шествующих по времени импульсам U блока 12, подается на вход контура (фиг,6),тока (четвертый вход блока 7), суммиРазность между значениями V и V руется с выходным сигналом регуля- в начальный момент вЬгчисления про- тора скорости и, тем самым, обеспе

50258

порциональна статическому моменту сопротивления, она убывает по мере того, как значение вычисленного момента сопл

ротивления Mj, на выходе второго интегратора и подаваемого на вход операционного усилителя 43 через резис тор 59| стремится к величине, пропорциональной истинному значению момента

10 сопротивления М, при этом вычисляемое значение мгновенной скорости со стремится к истинному значению мгновенной скорости (фиГоб.).

Таким образом, в установившемся

5 режиме, характеризуемом постоянством статического момента сопротивления на валу электродвигателя 1, так как М(, const, блок 12 динамической коррекции на основании данных о мгно-

20 венных значениях тока якоря ДПТ и дискретно вычисленных в цифровом

Чивается уменьшение времени реверса системе.

ормула изобретения

10

15

20

25

1. Цифроаналоговая следящая . система, содержа1йая усилитель-регулятор, блок динамической коррекцииj цифро-- аналоговый преобразователь, электродвигатель, на выходном валу которого установлен фазовращатель, информационный электрический вход которого соединен с выходом фильтра подключен™ 1ЮГО входом к первому выходу делите я частоты, второй выход которого одк лючен к первому входу фазового дискриминатора, а вход - к первому 3 ыходу генератора импульсов, второй 1.ЫХОД которого подключен к первому иходу цифрового сдвигшощего блока; I торой вход которого подключен к 1ЫХОДУ фазовращателя, второй выход 11ИФРОВОГО сдвигающего- блока подключен к второму входу фазового Лискриминатора, а первый выход - к тактовому входу блока цифрового измерения скорости, счетный вход которого подключен к третьему выходу те- г:ератора импульсов, первый выход блока динa шчecKoй коррекции подклю- ен к первом входу первого анапого- BJoro устройства сравнения, второй вход которого подключен к выходу фазового дискриминатора3 а выход - к первому входу усилителя-регулятора, выход которого подключен к входу гальванически развязывающего датчика тока, первый силовой выход которо- Г|О подключен к входу электродвигате™ дп , а второй информационньш выход - к EJepBOMy входу блока динамической кор- р1екции и второму входу усилителя- регулятора, выход цифроаналоговог- о п|рео6разователя подключен к второму . В1ХОДУ блока динамической коррекцииs чающаяся тем, что с целью повышения быстродействия, статической точности регулирования и устойчивости работы cncTei-ibi, в н1ее введены второе аналоговое устрой отво сравнения и блок йамяти, вход которого подключен к выходу блока п|ифрового измерения скорости s а выход - к :входу цифроаналогового преобразователя, выход которого подклю- ч1ен к первому входу второго аналогового устройства сравнения, второй в1ход которого подключен к выходу фа405025. 10

зового дискриминатора, а выход - к третьему входу усилителя-регулятора, четвертый вход которого подключен к второму выходу блока динамической коррекции, третий вход которого подключен к перво1 Гу выходу цифрового сдвигающего блока

2, Система по п.1, отличающаяся теМр что блок динамической коррекции содержит четыре операционных усилителя,, элемент выборки-хранения фop шpoвaтeль импзшьсов, три управляемых ключаэ J двенадцать масштабных резисторов, два накопительных кон денсатора, причем первый вход блока динамической коррекции через иторой масштабный резистор соединен с входом третьего управляемого ключа подключенного выходом к входу первого опера

35

50

55

динамической коррекции последов тельно соединенные первый масштабный резистор и первь:й управля емый ключ подключен к входу первого операционного усилителя 5 через четвертый масштабный резистор - к вход-у БТО- рсго операционного усилителя, через четвертьй масштабный резистор - к входу второго операциокного з снлкте- ля и через шестой масштабный резистор - к входу третьего опера1;;ионкО - го усилителя 3 третий ЕХОД блока динамической коррекции подключен к входу управления элемента выборки- хранения и через формирователь импульсов - к управляющим входам первого р, второго и третьего управляемых ключейsпервый выход блока динамической коррекции подключен к выходу первого операционного усилителя, подключенного через первый накопитель ный конденсатор и последовательно соединенные третий масштабный резистор н второй управляе-г-йш ключ к входу первого операционного усилителя, а непосредственно - к информационно- му входу элемента выборки-хранения, выход которого через пятый масштабный резистор подключен к входу второго операционного усилителя, а через седь мой масштабный резистор - к входу третьего операционного усилителя, вто рой выход блока динамической коррекции подключен к выходу третьего операционного усилителя, подключенного через дерятьш масштабный резистор к входу четвертого операционного усили

2, Система по п.1, отличающаяся теМр что блок динамической коррекции содержит четыре операционных усилителя,, элемент выборки-хранения фop шpoвaтeль импзшьсов, три управляемых ключаэ J двенадцать масштабных резисторов, два накопительных конденсатора, причем первый вход блока динамической коррекции через иторой масштабный резистор соединен с входом третьего управляемого ключа подключенного выходом к входу первого опера5

п

5

0

5

динамической коррекции последова тельно соединенные первый масштабный резистор и первь:й управля емый ключ подключен к входу первого операционного усилителя 5 через четвертый масштабный резистор - к вход-у БТО- рсго операционного усилителя, через четвертьй масштабный резистор - к входу второго операциокного з снлкте- ля и через шестой масштабный резистор - к входу третьего опера1;;ионкО - го усилителя 3 третий ЕХОД блока динамической коррекции подключен к входу управления элемента выборки- хранения и через формирователь импульсов - к управляющим входам первого р, второго и третьего управляемых ключейsпервый выход блока динамической коррекции подключен к выходу первого операционного усилителя, подключенного через первый накопительный конденсатор и последовательно соединенные третий масштабный резистор н второй управляе-г-йш ключ к входу первого операционного усилителя, а непосредственно - к информационно- му входу элемента выборки-хранения, выход которого через пятый масштабный резистор подключен к входу второго операционного усилителя, а через седь мой масштабный резистор - к входу третьего операционного усилителя, второй выход блока динамической коррекции подключен к выходу третьего операционного усилителя, подключенного через дерятьш масштабный резистор к входу четвертого операционного усили

теля, а через второй накопительный конденсатор - к входу третьего one- рационного усилителя, вькод второго операционного усилителя через восьм масштабный резистор подключен к входу второго операционного усилителя, через девятый масштабный резистор

5

12

к входу четвертого операционного усилителя, выход которого через одиннадцатый масштабный резистор подключен к входу четвертого операционного усилителя и через двенадцатый масштабный резистор - к входу третьего управляемого ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электропривод | 1987 |

|

SU1453569A1 |

| Устройство для моделирования @ -фазного вентильного электродвигателя | 1990 |

|

SU1797133A1 |

| Вентильный электродвигатель | 1989 |

|

SU1767638A1 |

| Устройство для управления скоростью вращения электродвигателя постоянного тока | 1985 |

|

SU1564590A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин с мультипликативной автокоррекцией | 1984 |

|

SU1185604A1 |

| Электропривод | 1988 |

|

SU1656652A1 |

| Устройство для контроля деградации МДП-структур | 1990 |

|

SU1783454A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Электропривод | 1985 |

|

SU1309232A1 |

| Аналого-цифровое делительное устройство | 1979 |

|

SU886017A1 |

Изобретение относится к автоматике и предназначено для использования в системах с числовым программным управлением и с электродвигателем постоянного тока без тахогенера- тора. Целью изобретения является по- вьшгение быстродействия, статической точности регулирования и устойчивости работы системы. Система содержит электродвигатель 1, фазовращатель 2, фильтр 3, делитель частоты 4, генератор импульсов 5, гальванически развязывающий датчик тока 6, усилитель- регулятор 7, аналоговые устройства сравнения 8,14, фазовый дискриминатор 9,блок цифрового измерения скорости 10,цифроаналоговый преобразователь 11,блок динамической коррекции 12, цифровой сдвигающий блок 13, блок памяти 15. Введением в систему устройства сравнения 14 блока памяти 15 и выполнением определенным образом блока динамической коррекции 12 достигается расширение полосы пропускания системы и улучшение ее динамических характеристик. 1 з.п, ф-лы, 7 ил. (О (Л

Фие.

Фие.

. f

BA.Z

B..i

flx.3

n-1

wT ur

ii

/72/

Фа.6

л.

П

| Цифро-аналоговая следящая система | 1978 |

|

SU750434A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР № 1154652, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-06-23—Публикация

1986-07-28—Подача