1

Изобретение относится к анологовой вычислительной и измерительной технике и может быть использовано в многоканальных аналоговых к цифровых информационно-измерительных системах.

Известно аналоговое запоминающее устройство (ЗУ)f содержащее, накопители на конденсаторах и узлы коррекции для многоуровневой стабилизации напряжения на конденсаторах. Конденсаторы поочередно подроединяются к узлам коррекции с помощью ключей 1 .

Недостатком такого устройства является малое быстродействие, так как необходима большая емкость накопительных конденсаторов, поскольку компараторы узлов коррекции подклю.чаются непосредственно к накопительным конденсаторам и входной ток компараторов оказывает дестабилизирующее действие на напряжение конденсаторов .

Наиболее близким по технической сущности к изобретению является многоканальное ЗУ, содержащее запоминающие емкости, ключи, аналогоцифровой преобразователь (АЦП), управляемой источник тока я блок

управления,состоящий из счетчика и дешифратора 2.

Недостатками этого устройства являются сложность конструкции, обусловленная применением АЦП и управляемого источника тока, и малое быстродействие.

Целью изобретения является повышение быстродействия ЗУ.

0

Поставленная цель достигается тем, что в ЗУ; содержащее основные ячейки памяти, состоящие из последовательно соединенных ключа записи, запоминающей емкости и ключа считы5вания, элемент ИЛИ, подключенный к блоку управления, соответствующие выходы которого соединены с управляющими входами ключей записи и считывания, источник напряжения, введеoны дополнительная ячейка памяти, сортоящая из последовательно соединенных ключа записи, запоминающей емкости и ключа считывания, и блок задания масштаба, входы которого соединены с

5 выходом ключей считывания основных и дополнительной ячеек памяти. Один вход ключа считывания дополнительной ячейки памяти соединен с выходом элемента ИЛИ, а соответствующие входы

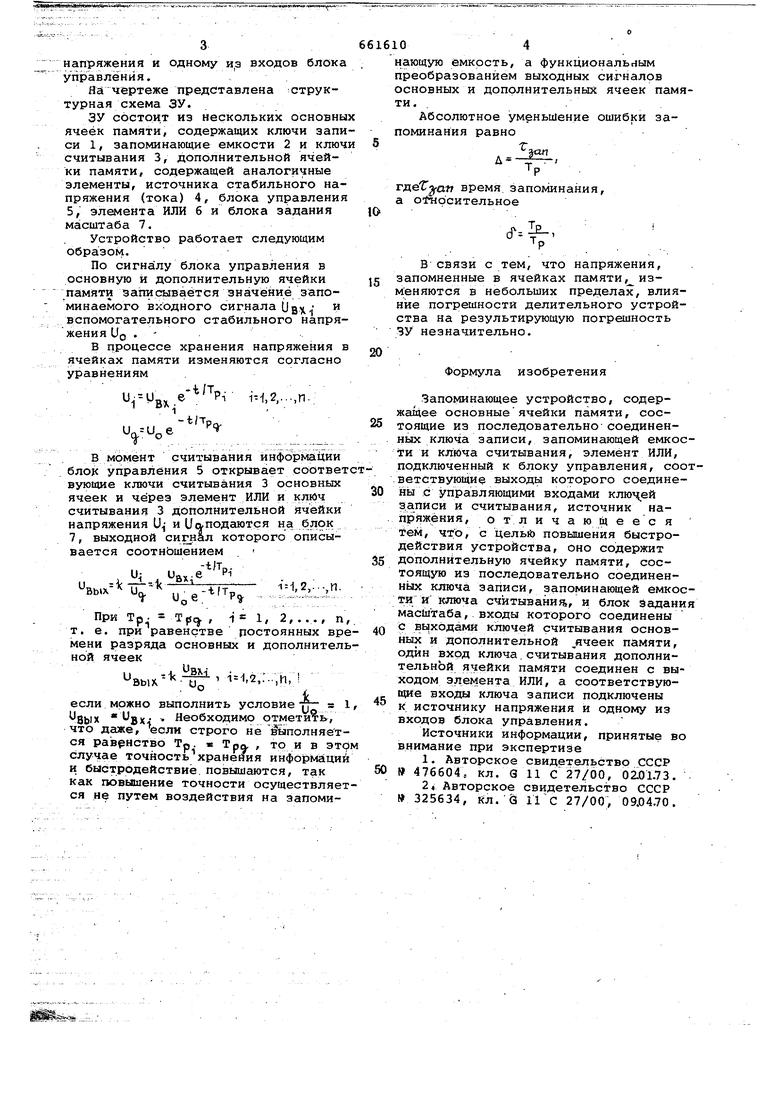

0 ключа записи подключены к источнику напряжения и одному из входов блока управления. на чертеже представлена структурная схема ЗУ. ЗУ состоит из нескольких основны ячеек памяти, содержащих ключи запи си 1, запоминающие емкости 2 и ключ считывания 3, дополнительной ячейки памяти, содержащей аналогичные элементы, источника стабильного напряжения (тока) 4, блока управления 5, элемента ИЛИ 6 и блока задания масштаба 7. Устройство работает следующим образом. По сигналу блока управления в основную и дополнительную ячейки памяти записывается значение запоминаемого входного сигнала и вспомогательного стабильного напря женин UQ . В процессе хранения напряжения ячейках памяти изменяются согласно уравнениям РТ iM,2,...,n. I-Sx. U,U.e-. В момент считывания информации блок управления 5 открывает соотве вующие ключи считывания 3 основных ячеек и через элемент ИЛИ и ключ считывания 3 дополнительной йчейки напряжения и U а подаются на блок 7, выходной сигнал которого описывается соотнЬшением . . , Ui , ,2,;.., п. Вых U g-ifTp При Тр. 1- 1, 2,..., п 1 т. е. при равенстве постоянных вр мени разряда основньах и дополнител ной ячеек Md выл i если можно выполнить условие ig- 8ЫХ вх Необходимо отметить, что даже, если строго не Шполняет ся равенство Тр. « Тра. , то и в зт случае точность хранения информаци и быстродействие повышаются, так как повышение точности осуществляе ся не путем воздействия на запоми04ающую емкость, а функциональным реобразованием выходных сигналов сновных и дополнительных ячеек памяи .. Абсолютное уменьшение ошибки заоминания равно , Eis Д -f-Г-/ время, запоминания, а о ирсительное Р. В связи с тем, что напряжения, запомненные в ячейках памяти, изменяются в небольших пределах, влияние погрешности делительного устройства на результирующую погрешность ЗУ незначительно. Формула изобретения Запоминающее устройство, содержащее основныеячейки памяти, состоящие из последовательно соединенных ключа записи, запоминающей емкости и ключа считывания, элемент ИЛИ, подключенный к блоку управления, соответствующие выходы которого соедине1Й1Ы с управляющими входами ключ.ей э аписи и считывания, источник напряжёния, отличающееся тем, что, с целыь повышения быстродействия устройства, оно содержит дополнительную ячейку памяти, состоящую из последовательно соединенных ключа записи, запоминающей емкости и ключа считывание, и блок задания масштаба, входы которого соединены с вьаходами ключей считывания основных и дополнительной ,ячеек памяти, один вход ключа.считывания дополнительнЬй ячейки памяти соединен с выходом 31лемента ИЛИ, а соответствующие входы ключа записи подключены к источнику напряжения и одному из входов блока управления. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 476604, кл. Q 11 С 27/00, OZ01.73. 2 Авторское свидетельство СССР №325634, Кл. Q 27/00, 09.04.70.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора и обработки информации | 1982 |

|

SU1057950A2 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015445A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

| Анализатор амплитудно-временных параметров случайных сигналов | 1990 |

|

SU1758576A1 |

| ЦИФРОВОЙ ТЕЛЕФОННЫЙ СИНТЕЗАТОР РЕЧИ | 1992 |

|

RU2106754C1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| ТЕРМОМОНИТОР | 1999 |

|

RU2155941C1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| Способ регистрации однократных импульсных сигналов наносекундного диапазона | 1974 |

|

SU752401A1 |

Авторы

Даты

1979-05-05—Публикация

1977-05-18—Подача