Предложение относится к автоматике и вычислительной технике.

Известно заиомииаюи1,ее устройство, выполненное на трайсфлюксорах, уиравляемых неограниченными токами, содержащее обмотки блокировки, разблокировки и запрета.

Предложенное устройство отличается тем, что в нем адресные числовые шины заииси пропуи;ены последовательно через большие и малые отверстия всех элементов иамяти каждого числа и охватывают средние иеремычки т)ансфлюксоров, адресные разрядные шины запрета ироиуихены последовательно через малые отверстия элементов памяти одноименных разрядов всех чисел, а адресными числовыми шинами разблокировки служат секиии числовых обмоток записи, проходящие через малые отверстия трансфлюксоров, и тем, что адресные разрядные шины записи охват1)1вают последовательно средние иеремычки элемеитои памяти одноименных разрядов всех чисел, адресные разрядн1 1е шины разблокировки, которыми служат соответствуюпдие секции разрядных обмоток заипси, ироходят последовательно через .малые отверстия трансфлюксоров и адресные числовые шины запрета проходят через малые отверстия элементов памяти всех разрядов каждого числа.

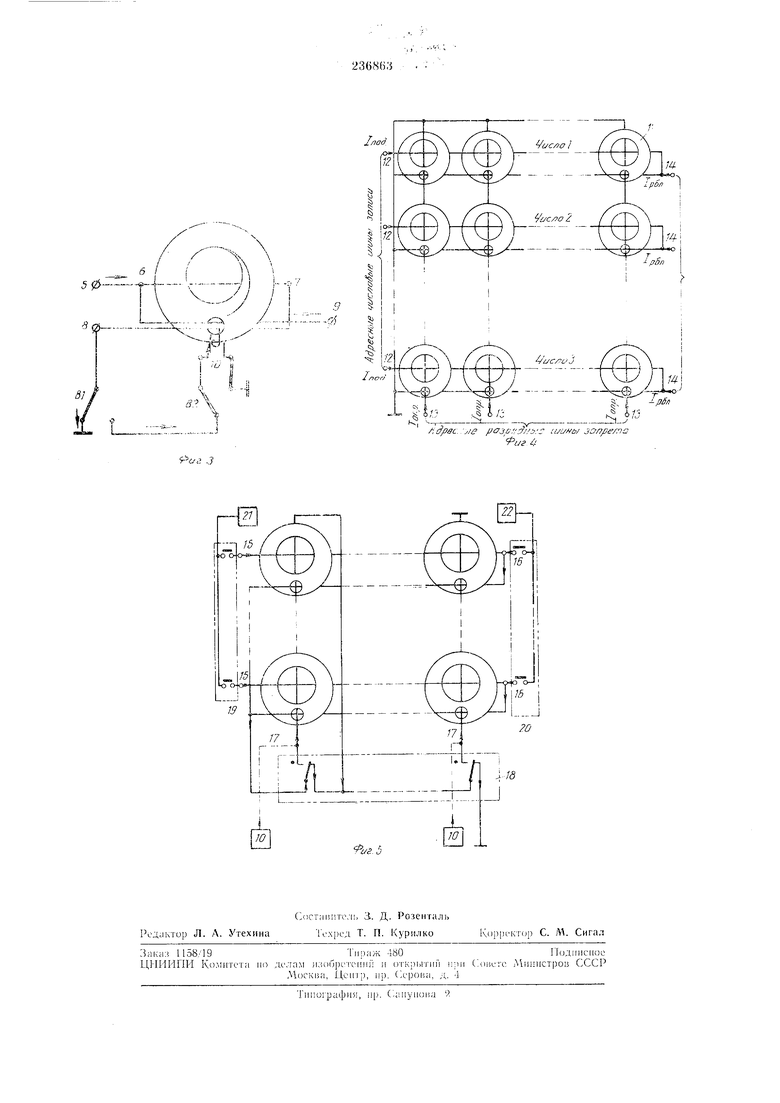

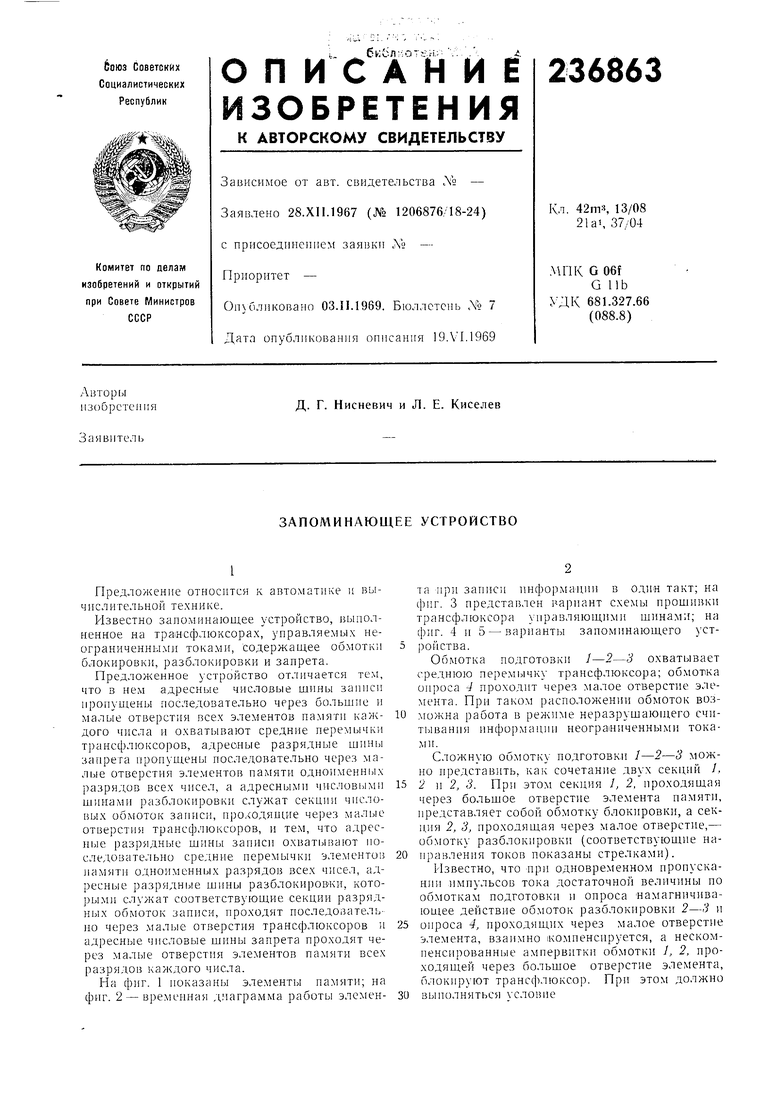

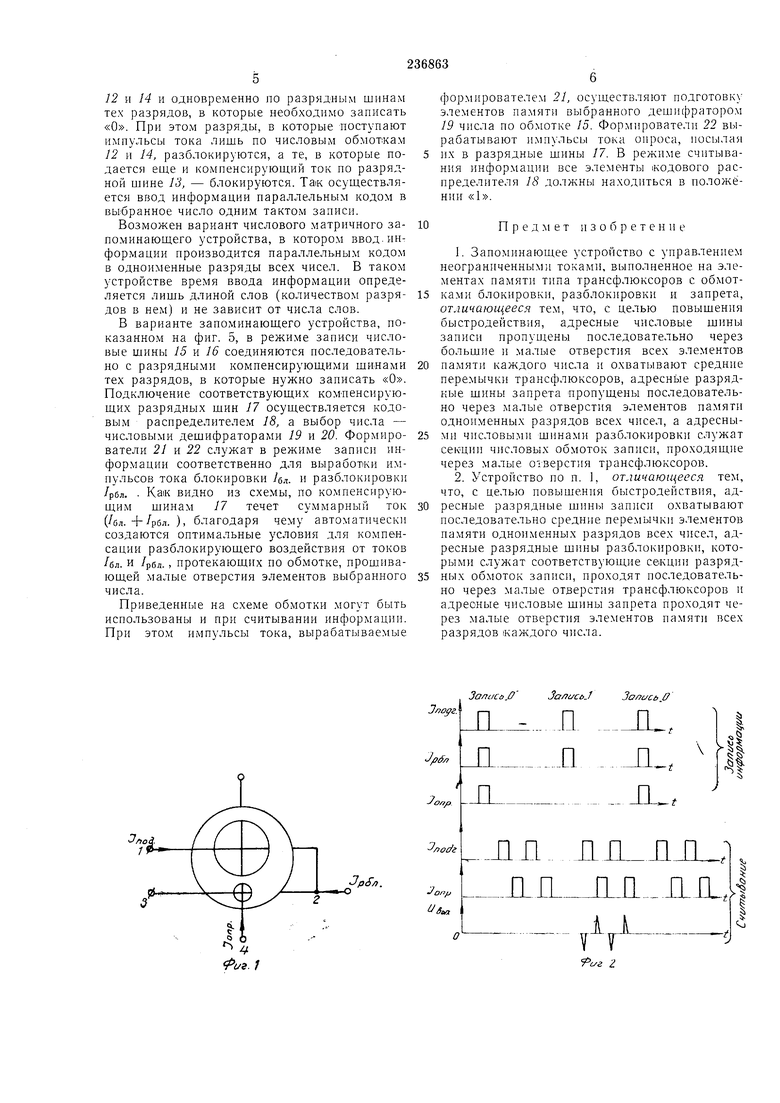

та при заиисп информации в одни такт; на фиг. 3 представлен вариант схемы прошивки трансфлЕОксора управляющими шинами; на фиг. 4 и 5 - варианты запоминающего стройства.

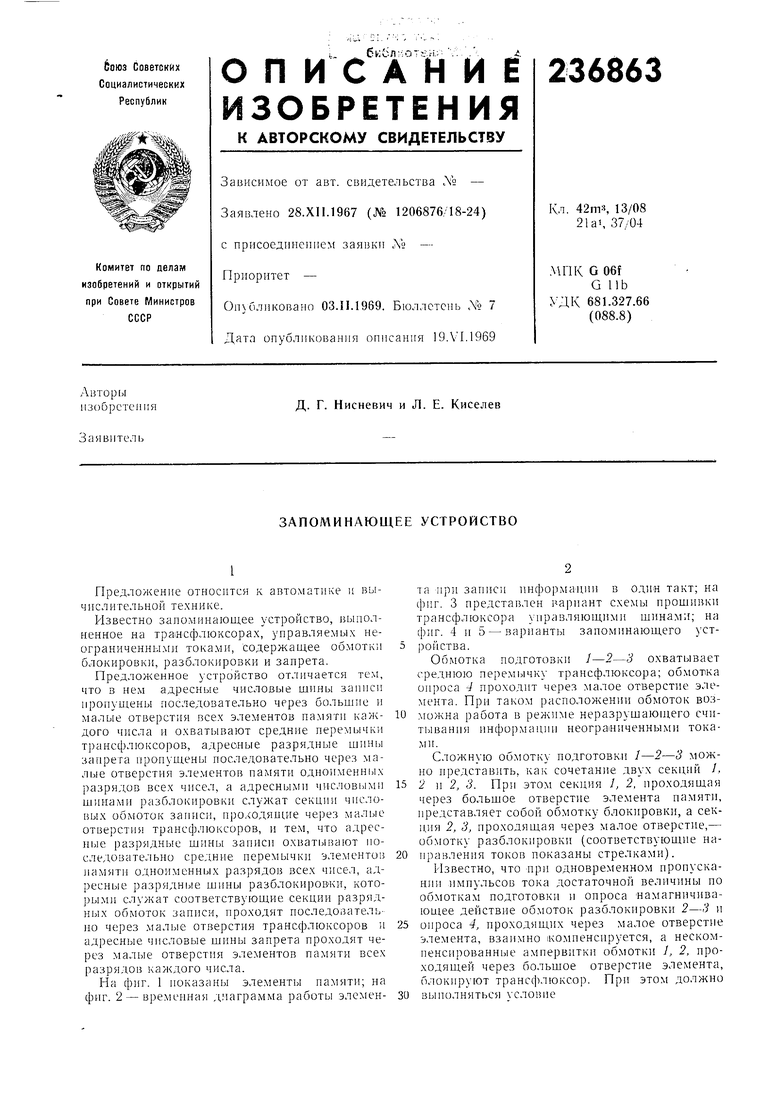

Обмотка подготовки /-2-3 охватывает {реднюю пере.мычку трансфлюксора; обмотка опроса J проходпт через малое отверстие элемента. При таком расположении обмоток возможна работа в режиме неразрушаюихего считывания информации неограаиченны.ми токаЛ1П.

Сложную обмотку подготовки /-2-3 можно представить, как сочетание двух секций /,

2 и 2, 3. При этом секция /, 2. проходящая через большое отверстие элемента памяти, иредставляет собой обмотку блокировк, а секп,ия 2, 3, проходящая через малое отверстие,- обмотку разблокировки (соответствующие направления токов показаны стре.тками).

Известно, что ири одновременном пропускании импульсов тока достаточной величины по обмоткам подготовки и опроса яамагничпвающее действие обмоток разблокировки 2-3 и

оироса 4, ироходящих через малое отверстие элемента, взаимно компенсируется, а нескомиенсированные ампервитки обмотки /, 2, проходящей через большое отверстие элемента, блокируют трансфлюксор. При этом должно

/ Jl- oilp. / ; У полг. / бл. 1

где /Worip. ; / подг.; /№бл. - соответственно амперннткн опроса, 11одгото1 1чп и блоклровки.

Одновременно пропускание импульсов тока но обмоткам подготовки /, 2, 3 и разблокировки 2, 3 )азблокнрует трапсфлюксор. При этом на.магнпч11ваюп1,ая спла, создаваемая нмнулвсом тока подготовки (/„од. ) по обмотке 1, 2, 3 II ра.чб;1ок11|)овк11 (/рбл.) по обмотке 2, 3, проходяп1,ей через малое отверстие трансфлюксора, определяется суммарнв1мн ампервпткамн.

(/подг. Г /рбл. )1 2,3 ,

где U2,.3 --- число витков секиип 2, 3.

Для того, 4To6i i осуп:ествить блокировку элемента при одновременном возде1 |ствпп импульсов тока подготовки и разблокировки, необходпмо пропустить по обмотке опроса 4 тока /опр. . который счкомиенспровал бы намагничивающее воздействие разблокпруюпам 1 секнпи 2, 3 обмотки подготовки /, 2, /i, т.е.

/Oiip.t .3 .-- (подг. + /рбл. ) Vt2,3 J

где W4 - число витков обмотки опроса.

В рассмотренном режиме работы ин(|)ормац1111 в запоминаюп|,ее устройст О можно производить в один такт. При этом рассматрива.чась ко.миенсадия разблок11)у1О1цего де1 ствни (K MOTiKH 2, 3 амнервнткамн, создаваемыми обмоткой онроса 4.

Это возможно, так как запнсь ннф() и считывание ее по обмоткам /, 2, 3 н 4 иронсходнт в разные моменты времени. При этом сокращается чпсло управляющн.х проводов.

Возможен вариант прошивки, ири котором имеются специальные обмоткн занрета и записи, соответственно идентичные обмоткам опроса и подготовки.

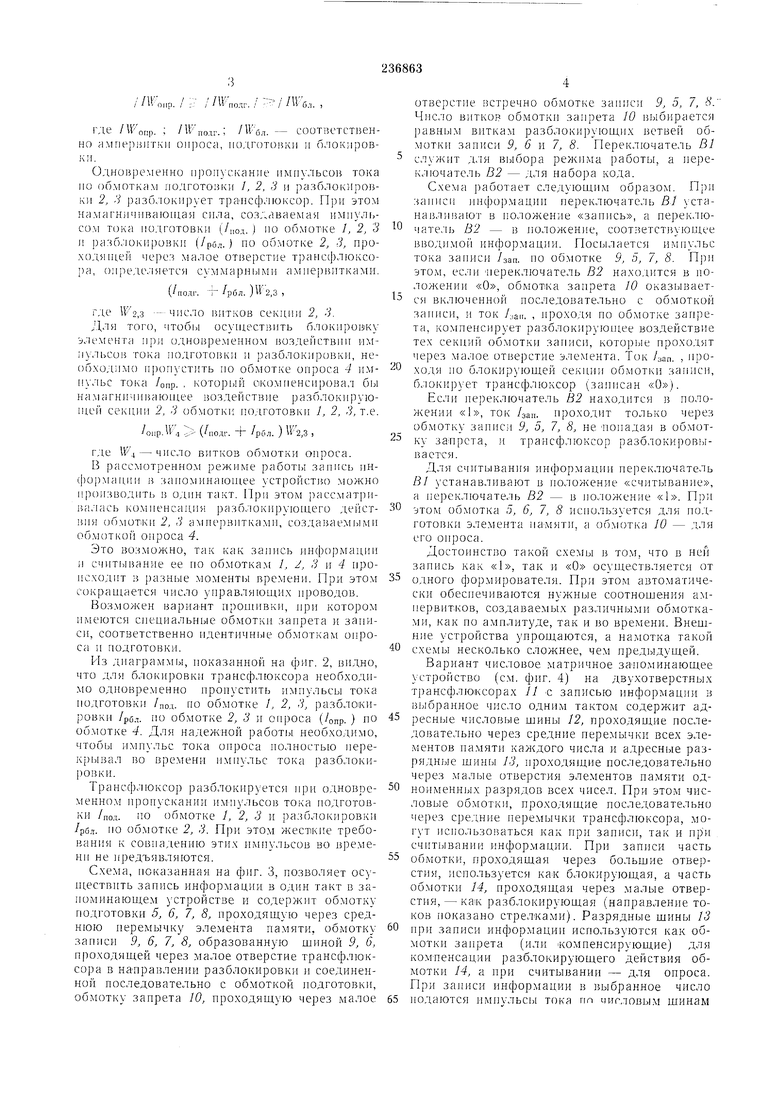

Из днаграммы, показанной на фиг. 2, видно, что для блокировки трансфлЕоксора необходнмо одновременно нронустить импульсы тока подготовки /под. по обмотке /, 2, 3, разбло1кировки /рб.,. ио обмотке 2, 3 и оироса (/опр. ) но обмотке 4. Для надежной работы необходимо, чтобы импульс тока онроса полностью нерекрывал во времени импульс тока разблокировки.

Трансфлюксор разблокируется нрн одновременном нропускании импульсо) тока подготовки /ПО.Д. ио обмотке /, 2, 3 и разблокпровки /рб.ч. ио обмотке 2, 3. Прн этом жест1кие требования к совиаденню этих нмпу.тьсов во временн не н)едъявляются.

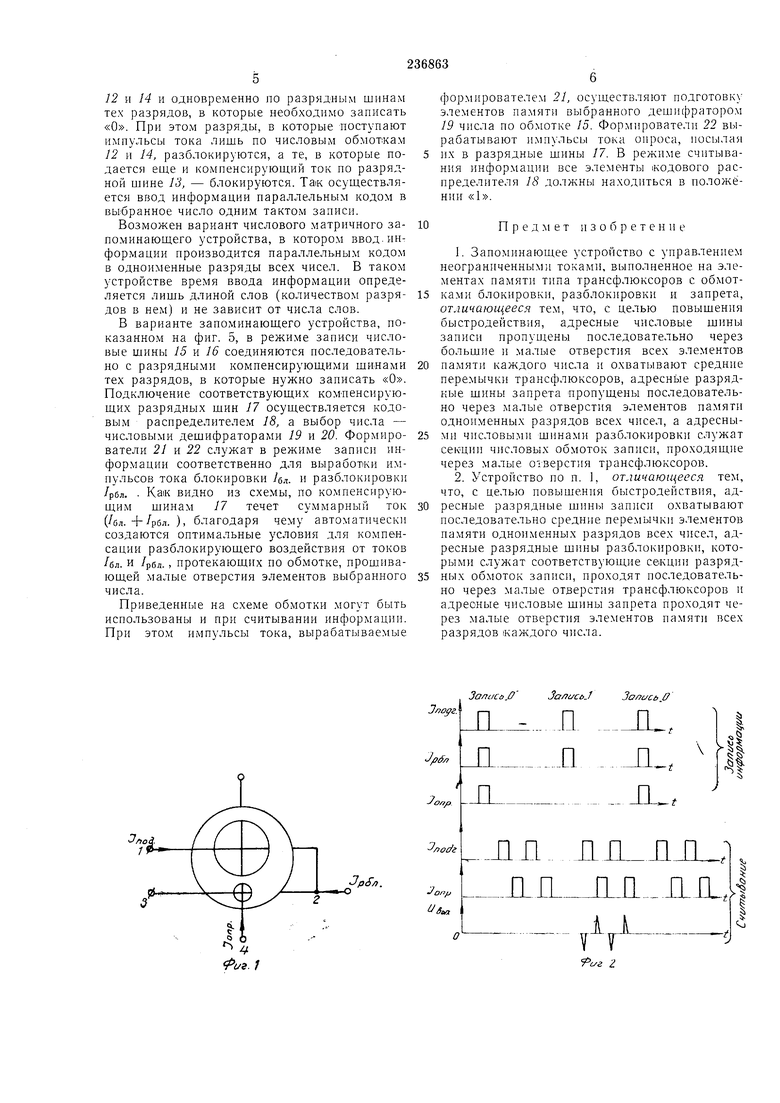

Схема, наказанная на фиг. 3, позволяет осуН1,еств11ть запись информации в один такт в заиоминающем устройстве и содержит обмотку подготовки 5, 6, 7, 8, нро.ходящую через среднюю неремычку элемента памяти, обмотку записи 9, 6, 7, 8, образованную шиной Я G, проходящей через малое отверстие трансфлюксора в направлении разблокировки н соединенной последовательно с обмоткой нодготовкн, обмотку занрета 10, нроходящую через малое

отверстие встречно обмотке записи 9, 5, /, 8. Чпсло витков обмотки запрета 10 выбирается равным виткам разблокирующих ветвей обмотки заинси 9, 6 н 7, 8. Переключатель В1 служит для Bi)i6opa режима работы, а переключатель В2 - для набора кода.

Схема )аботает следующим образом. заииси инфор.мадни переключатель В1 устана15ливают в положение «заннсь, а перек.тючатель В2 - в положение, соответствующее вводи.мой информации. Посылается импульс тока записи /зап. ио обмотке 9, 5, 7, 8. При этом, еслп Переключатель В2 нахо.и1тся в иоложении «О, обмотка запрета 10 оказывается включенной последовательно с обмоткой заннсн, и ток . , проходя ио обмотке запрета, компенсирует разблокир)ющее воздействие тех секций обмотки записи, которые проходят через малое отверстие элемента. Ток /зап. , проходя ио блокирующей секции обмотки записи, блок11)ует трансфлюксор (за111 сан «О).

Если переключатель В2 находится в положении «1, ток /зап. проходит ТОЛЬКО через об.мотку заннс.и 9, 5, 7, 8, не поиадая в обмотку за нрета, и трансфлюксор разбдокировывается.

Для считывания информации иереключатель устанавливают в положение «считывание, а ие)еключатель В2 - в положение «1. При этом обмотка 5, 6, 7, 8 исиользуется для подготовки элемента иамяти, а обмотка JO - для его оироса.

Достоинство такой схемы в том, что в ней занись как «1, так и «О осуществляется от одного формирователя. При это.м автоматически обеспечиваются нужные соотнощения амиервнт.ков, создаваемых различными обмотками, как но амнлитуде, так и во времени. Внешние устройства упрощаются, а намотка такой схемы несколько сложнее, чем предыдущей.

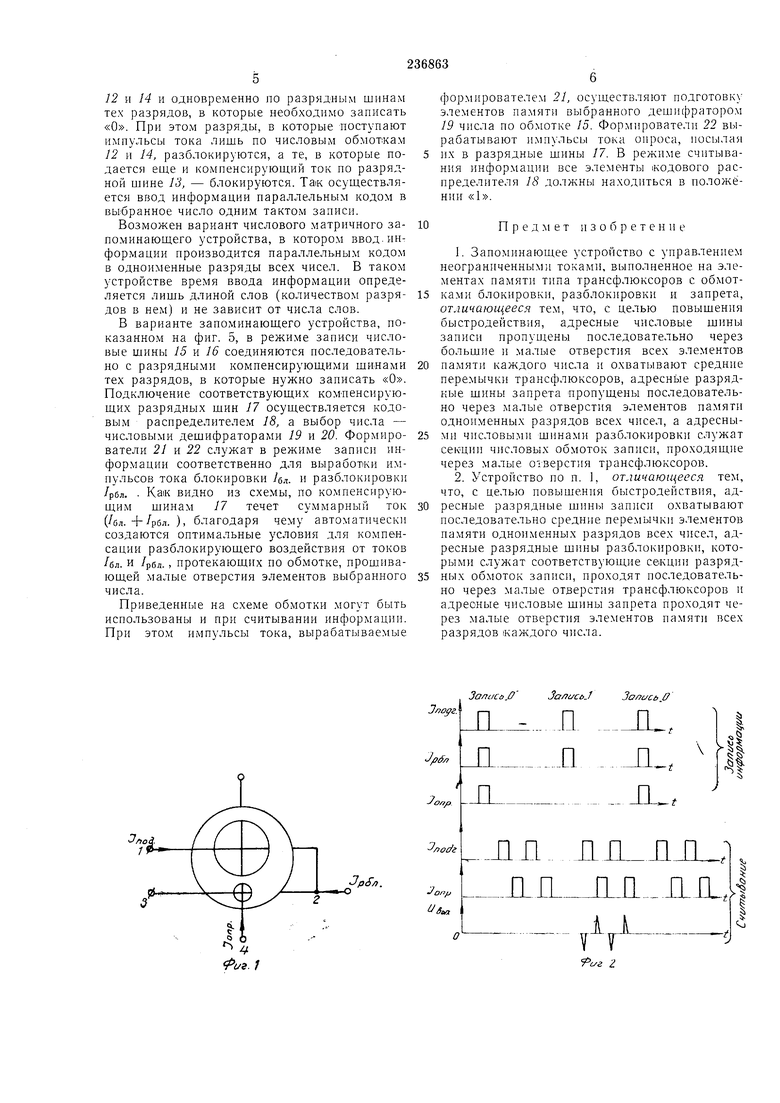

Вариант числовое матричное зано.минающее устройство (см. фцг. 4) на двухотверстных трансфлю1ксорах // € записью информации в выбранное число одним тактом содержит адpecHijie числовые щнны 12, проходящие последовательно через средние перемычки всех элементов намятн каждого чнсда н адресные разрядные щины /J, нроходящне последовательно через .малые отверстия элементов памяти одноименных разрядов всех чисел. При это.м чнсловые обмотки, нро.кодящие последовательно че|)ез средние иеремычки трансфлюксора, могут иснользоваться как при заннс, так и при счнтыванни информации. Прп записи часть об мотки, проходящая через большие отверстия, используется блокирующая, а часть обмотки 14, проходящая через малые отверстия,- как разблокцрующая (нанравленне токов показано стрелками). Разрядные щины 13 нри записи информации используются как обмоткн занрета (или компенсирующие) для комненсации разблокирующего действия обмоткн 14, а нрц считывании - для онроса. При заннси информации в выбранное число иодаются ИМПУЛЬСЫ тока пп чигловым щинам

12 и 14 и одновременно по разрядным шинам тех разрядов, в которые необходимо записать «О. Прп этом разряды, в которые поступают импульсы тока лишь по числовым обмоткам 12 и 14, разблокируются, а те, в которые подается еще и компенсируюш,ий ток по разрядной шине 13, - блокируются. Так осуществляется ввод информации параллельным кодом в выбранное число одним тактом записи.

Возможен вариант числового матричного запоминающего устройства, в котором ввод.информации производится параллельным кодом в одноименные разряды всех чисел. В таком устройстве время ввода информации определяется лишь длиной слов (количеством разрядов в нем) и не зависит от числа слов.

В варианте запоминающего устройства, показанном на фиг. 5, в режиме записи числовые шины 15 и 16 соединяются последовательно с разрядными компенсирующими шинами тех разрядов, в которые нужно записать «О. Подключение соответствующих компенсирующих разрядных шин 17 осушествляется кодовым распределителем 18, а выбор числа - числовыми дешифраторами 19 и 20. Формирователи 21 и 22 служат в режиме записи информации соответственно для выработки импульсов тока блокировки /бл. и разблокировки /рбл. . Как видно из схемы, по компенсирующи1М шинам 17 течет суммарный ток (л.. ), благодаря чему автоматически создаются оптимальные условия для компенсации разблокирующего воздействия от токов бп. и /рбл., протекающих по обмотке, прощивающей малые отверстия элементов выбранного числа.

Приведенные на схеме обмотки .могут быть использованы и при считывании информации. При этом импульсы тока, вырабатываемые

формирователем 21, осуществляют подготовку элементов памяти выбранного дешифратором 19 числа по обмотке /5. Формирователи 22 вырабатывают импульсы TOiKa опроса, посылая их в разрядные шины 17. В режиме считывания информации все элементы 1кодового распределителя 18 должнЕз на.ходиться в положении «1.

Предмет изобретение

1.Запоминающее устройство с управлением неограниченными токами, выполненное на элементах памяти типа трансфлюксоров с обмотками блокировки, разблокировки и запрета, отличающееся тем, что, с целью повышения быстродействия, адресные числовые шины записи пропущены последовательно через большие и малые отверстия всех элементов

памяти каждого числа и охватывают средние перемычки трансфлюксоров, адреснь1е разрядные щины запрета пропущены последовательно через малые отверстия элементов памяти одноименных разрядов всех чисел, а адресными числовыми шинами разблокировк служат сек-цип числовых обмоток записи, проходящие через малые отверстия трансфлюксоров.

2.Устройство по п. 1, отличающееся тем, что, с целью повышения быстродействия, адресные разрядные шины записи охватывают последовательно средние пере.мычкп эле.ментов памяти одноименных разрядов всех чисел, адресные разрядные щины разблокировки, которыми служат соответствующие секции разрядных обмоток записи, проходят последовательно через малые отверстия трансфлюксоров и адресные числовые шины запрета проходят через малые отверст я элементов памяти всех разрядов каждого числа.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU236862A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU254205A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU300890A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU335719A1 |

| Запоминающее устройство | 1973 |

|

SU446108A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1967 |

|

SU216795A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU341083A1 |

| Устройство дискретной обработки информации | 1980 |

|

SU884140A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОВС.'СОгООНАЯр jc|JiHO иХ^Ш^^- БИБЛИОТЕНА | 1972 |

|

SU332500A1 |

| Логическое запоминающее устройство | 1976 |

|

SU631989A1 |

-О

Jo/Tf/CuJ

Залисо.О

Запись ff

UnOffS.

Л.П

-L,

.1 .Jl,

it

J..

(

.„л -JI, Jonfl

лд

Jf)S/.

.й..Л11.

S

V

Авторы

Даты

1969-01-01—Публикация