Изобретение относится к автоматике и вычислительной технике.

Известно запоминающее устройство (ЗУ) по основном авт. св. N° 206903 на т/рансфлюксорах, содержащее числовые щины записи «О и «1, разрядные шины запрета «О и «1, кодовый распределитель. Общая точка всех числовых щин записи «1 матрицы ЗУ через кодовый распределитель подключена к щинам запрета первого разряда, а выходы запретных шин каледого разряда объединены в общую точку, подключенную через кодовый распределитель к шинам «запрета следующего разряда.

Однако такие ЗУ имеют больщое число внешних по отношению к матрице проводов, идущих от общей точки выхода щин запрета каждого разряда на кодовой раснределитель. Эти дополнительные провода не связаны непосредственно с элементами памяти и обеспечивают последовательность цепи записи из шин запрета через кодовый распределитель. В результате увеличивается сопротивление цепи .записи и межпроводная «паразитная емкость, повыщается требуемая мощность импульсов .записи и искажается форма импульсов.

проходят встречно через элементы памяти смежных разрядов каждого чис.1а.

Благодаря такой прошивке концы шин запрета смежных разрядов объединяются з рбщую точку либо непосредственно на матрице ЗУ, либо только на кодовом распределителе.

В такой схеме число дополнительных про,водов, не связанных непосредственно с эле,ментами намяти, либо сокращается вдвое (ЗУ на двухотверстных тра-вофлюксдрах, фиг. 1), либо полностью исключается (ЗУ на четырехотверстных трансфлюксорах, фиг. 2 и 3). Благодаря этому снижается «паразитная емкость монтал а, уменьщается сопротивление цепи записи н, как следствие, мощность источника импульсов записи. Надежность таких схем выще по сравнению с известными, технология изготовления проще, а себестоимость ниже.

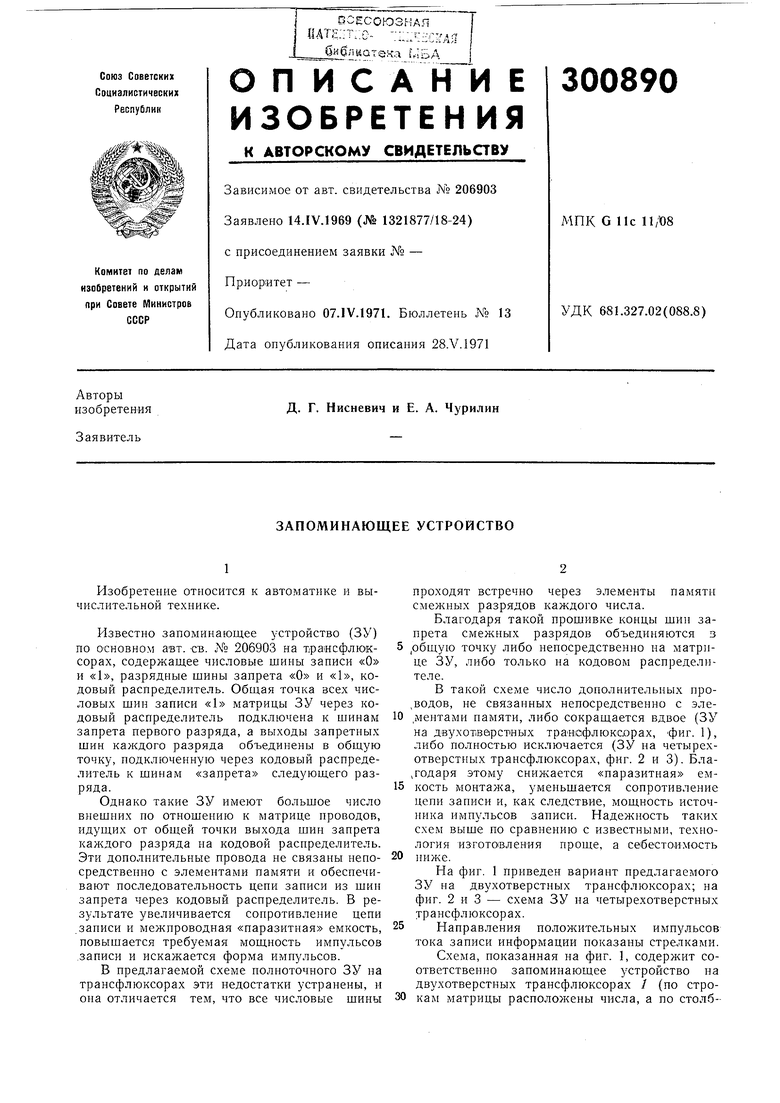

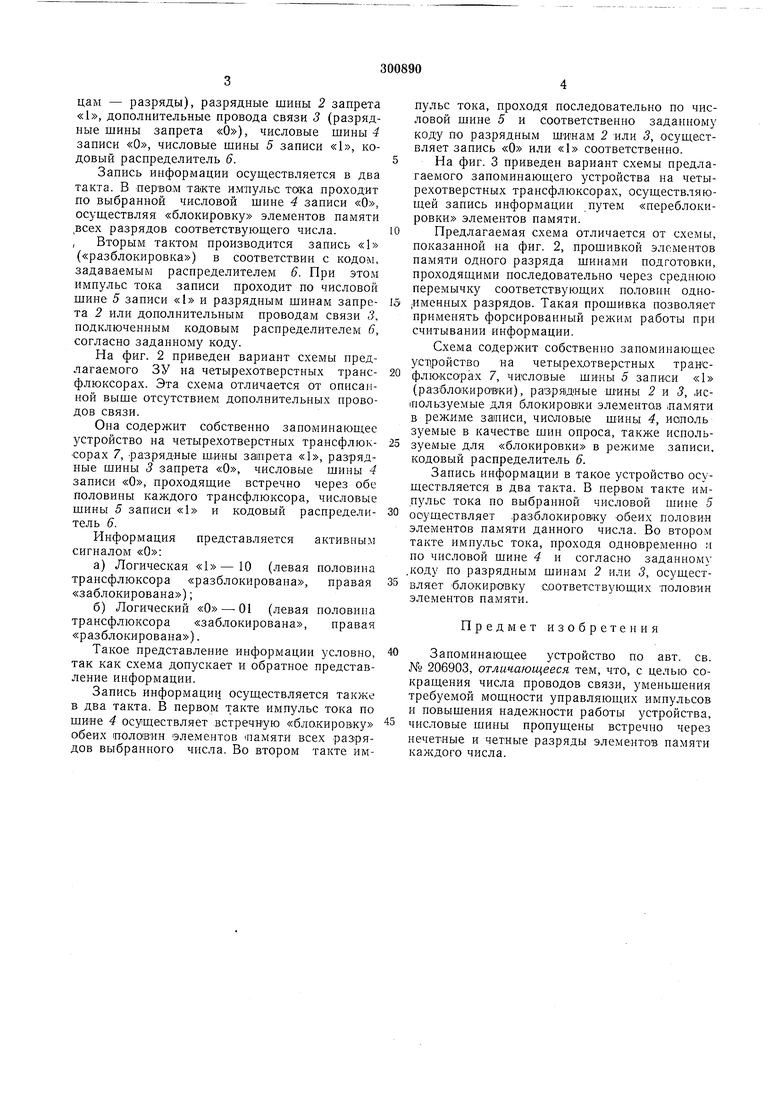

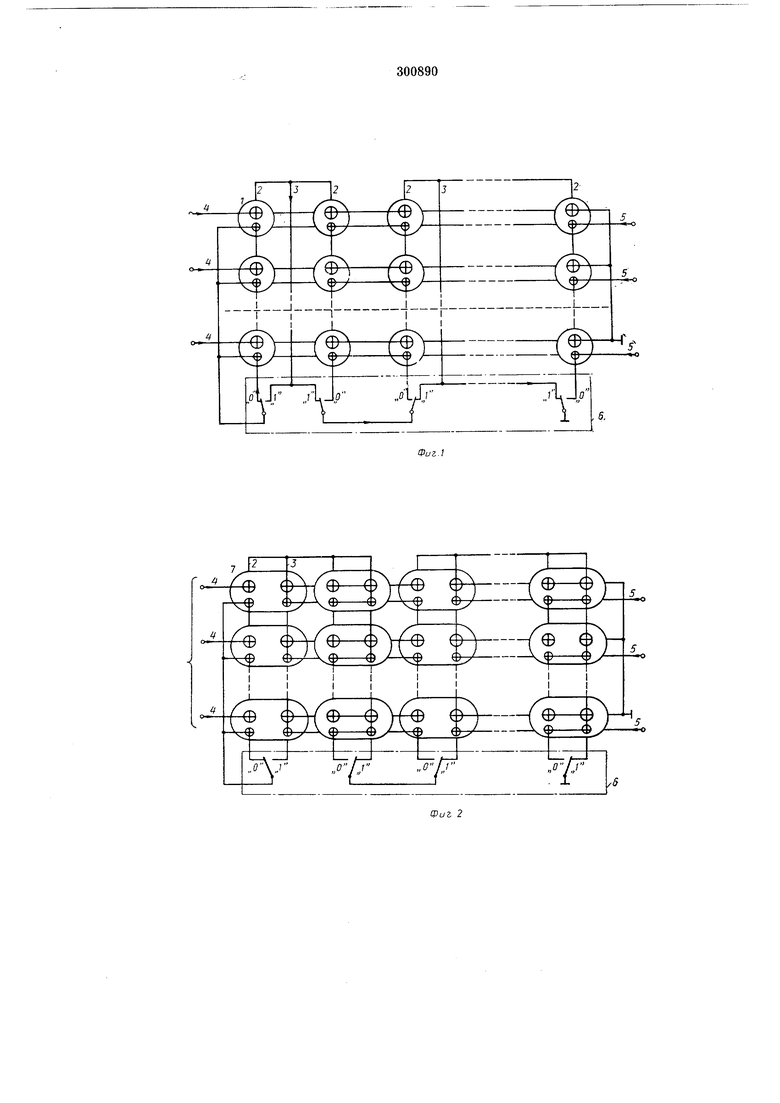

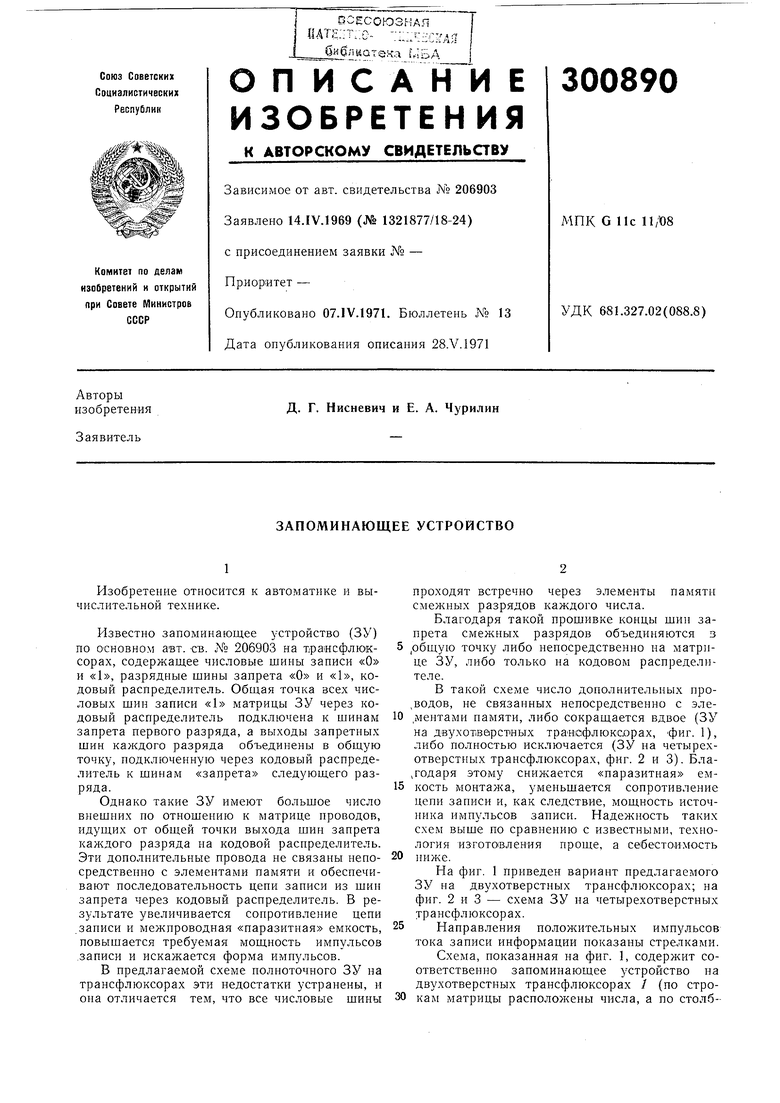

На фиг. 1 приведен вариант предлагаемого ЗУ на двухотверстных трансфлюксорах; на фиг. 2 и 3 - схема ЗУ на четырехотверстных трансфлюксорах.

Направления положительных импульсов тока записи информации показаны стрелками.

дам - разряды), разрядные шины 2 запрета «1, дополнительные провода связи 3 (разрядные шины запрета «О), числовые шины 4 записи «О, числовые шины 5 записи «1, кодовый распределитель 6.

Запись информации осушествляется в два такта. В лерВ0:М такте импульс тока проходит по выбранной числовой шине 4 записи «О, осушествляя «блокировку элементов памяти ,всех разрядов соответствуюшего числа.

Вторым тактом производится запись «1 («разблокировка) в соответствии с кодом, задаваемым распределителем 6. При этом импульс тока записи проходит по числовой шине 5 записи «1 и разрядным шинам запрета 2 или дополнительным проводам связи 3, подключенным кодовым распределителем 6, согласно заданному коду.

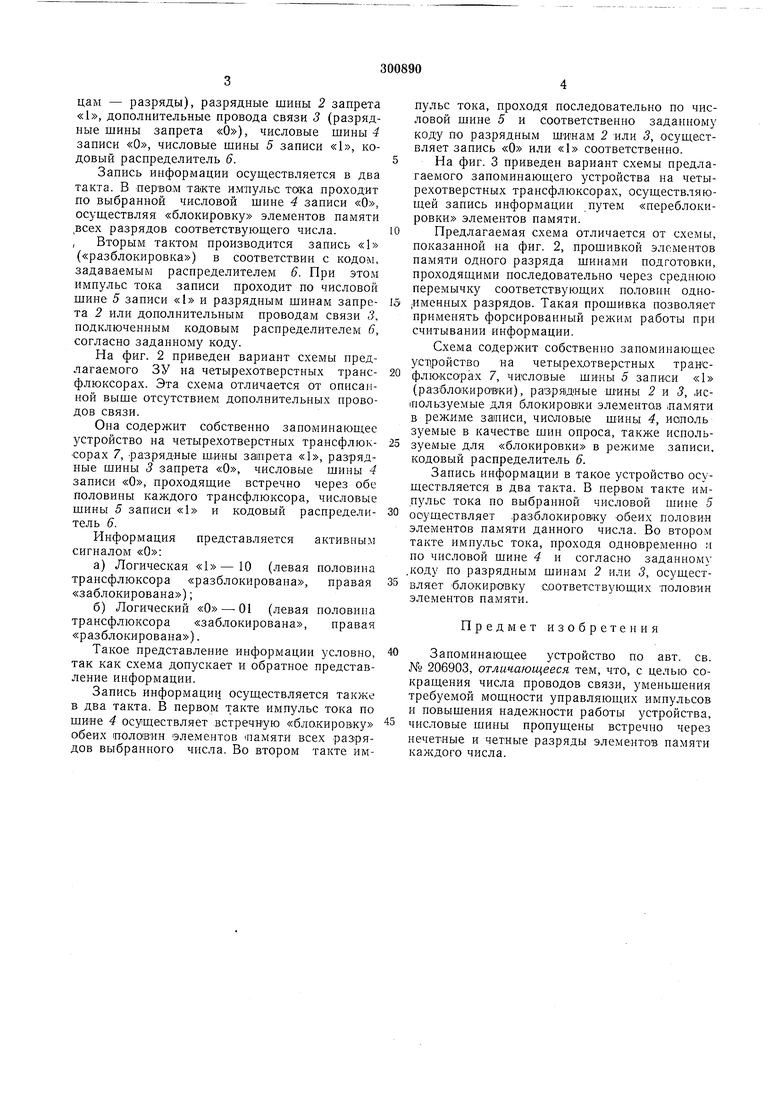

На фиг. 2 приведен вариант схемы предлагаемого ЗУ на четырехотверстных трансфлюксорах. Эта схема отличается от описанной выше отсутствием дополнительных проводов связи.

Она содержит собственно запоминаюш.ее устройство на четырехотверстных трансфлюксорах 7, разрядные шй-ны запрета «Ь, разрядные шины 3 запрета «О, числовые шины 4 записи «О, проходяшие встречно через обе половины каждого трансфлюксора, числовые шины 5 записи «1 и кодовый распределитель 6.

Информация представляется активным сигналом

а)Логическая (левая половина трансфлюксора «разблокирована, правая «заблокирована);

б)Логический «О - 01 (левая половина трансфлюксора «заблокирована, правая «разблокирована).

Такое представление информации условно, так как схема допускает и обратное представление информации.

Запись информации осушествляется также в два такта. В первом такте импульс тока по шине 4 осушествляет встречную «бло.кировку обеих половин элементов памяти всех разрядов выбранного числа. Во втором такте импульс тока, проходя последовательно по числовой шине 5 и соответственно заданному коду по разрядным шинам 2 или 3, о-существляет запись «О или «1 соответственно.

На фиг. 3 приведен вариант схемы предлагаемого запоминаюшего устройства на четырехотверстных трансфлюксорах, осушествляюшей запись информации путем «переблокировки элементов памяти.

Предлагаемая схема отличается от схемы, показанной на фиг. 2, прошивкой элементов памяти одного разряда шинами подготовки, проходяшими последовательно через среднюю перемычку соответствуюших половин одно(Именных разрядов. Такая прошивка позволяет применять форсированный режим работы при считывании информации.

Схема содержит собственно запоминаюшее УСТ1РОЙСТВО на четырехотверстных трансфлЮКсорах 7, числовые ши-ны 5 записи «1 (разбло1КирОВ1Ки), ра3ряд1ные Шины 2 и 5, .используемые для бло-кировки элементо,в памяти в режиме записи, числовые шины 4, иополь зуемые в качестве шин опроса, иснользуемые для «блокировки в режиме записи, кодовый распределитель 6.

Запись информации в такое устройство осушествляется в два такта. В первом такте импульс тока по выбранной числовой шине 5

осуществляет .разблокировку обеих половин элементов памяти данного числа. Во втором такте импульс тока, проходя одновременно м по числовой шине 4 и согласно заданному .коду по разрядным шинам 2 или 3, осушествляет блокировку с.оответствуюших половин элементов намяти.

Предмет изобретения

Запоминаюшее устройство по авт. св. Лз 206903, отличающееся тем, что, с целью сокрашения числа проводов связи, уменьшения требуемой мошности управляюших импульсов и повышения надежности работы устройства,

числовые шины нропушены встречно через нечетные и четные разряды элементов намяти каждого числа.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU236863A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU254205A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU236862A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1967 |

|

SU216795A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1968 |

|

SU206903A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU341083A1 |

| МАГНИТНЫЙ НАКОПИТЕЛЬ | 1973 |

|

SU385315A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU335719A1 |

| СПОСОБ ЗАПИСИ И СЧИТЫВАНИЯ ИНФОРМАЦИИ В ЧЕТЫРЕХОТВЕРСТНОМ ТРАНСФЛЮКСОРЕ | 1971 |

|

SU297996A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU388299A1 |

.J:

Даты

1971-01-01—Публикация