Изобретеине относится к aвтo aтикe и пычислительио технике.

Известно заноминающее устройство, вынолненное на элементах - траисфлюксорах, содержащих обмотки блокировки, разблокировки и занрета, подготовки и опроса, включающее адресный дешифратор и кодовый распределитель.

Предложенное устройство отличается тем, что в нем разрядные шины блокировки нроходят последовательно через элементы памяти одноименных разрядов всех чисел, а разрядные шины разблокировки охватывают носледовательно средние иеремычки элементов памяти одноименных разрядов всех чисел, начала шин разблокировки подключены к адресному разрядному дешифратору, а концы этих ншн объединены н подключены к началу HcpBoii числовой шииы запрета, охватывающей иоследовательно средние перемычки элементов памяти всех разрядов каждого числа, конец нервой обмотки запрета через числовой кодовый распределитель подключен к началу следующей числовой обмотки запрета, адресные разрядные шнны разблокировки проходят последовательно через малые отверстия элементов одноименных разрядов всех чисел и адресные разрядные шины подготовки охватывают последовательно средние перемычки элементов памяти одноименных разрядов всех чнсел, а

адресные числовые Н1ины (мтроса проходят последовательно через малые отверстия элементов памятн каждого чпсла.

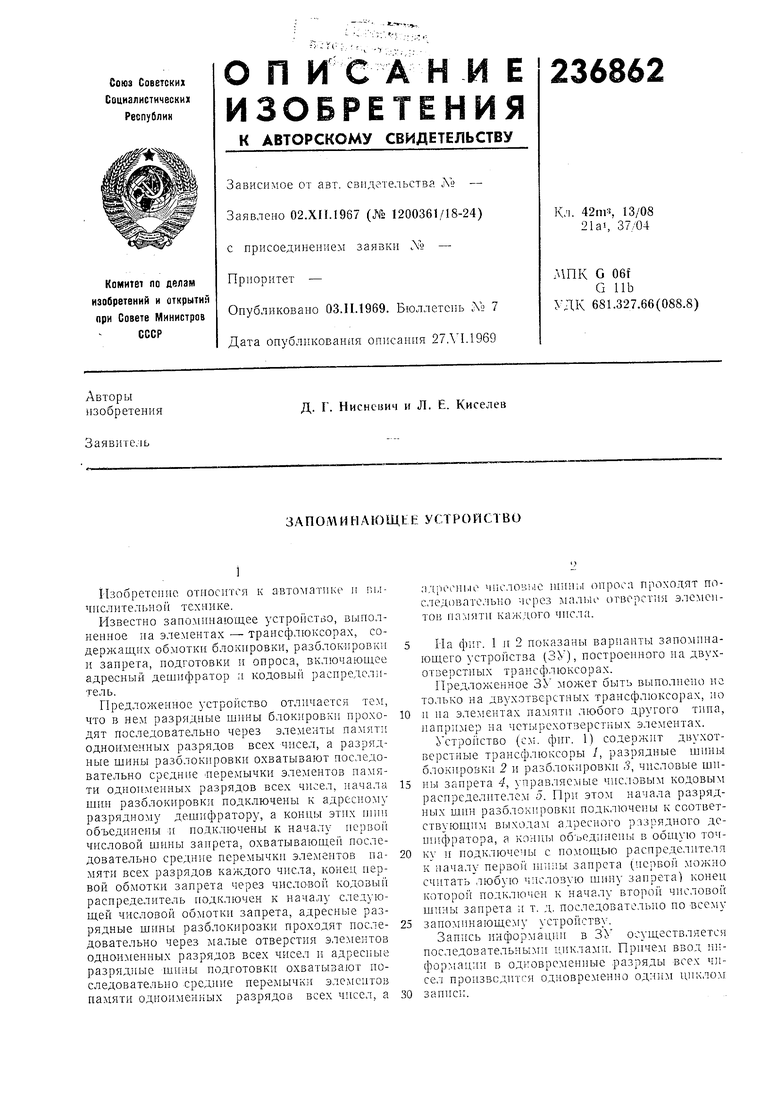

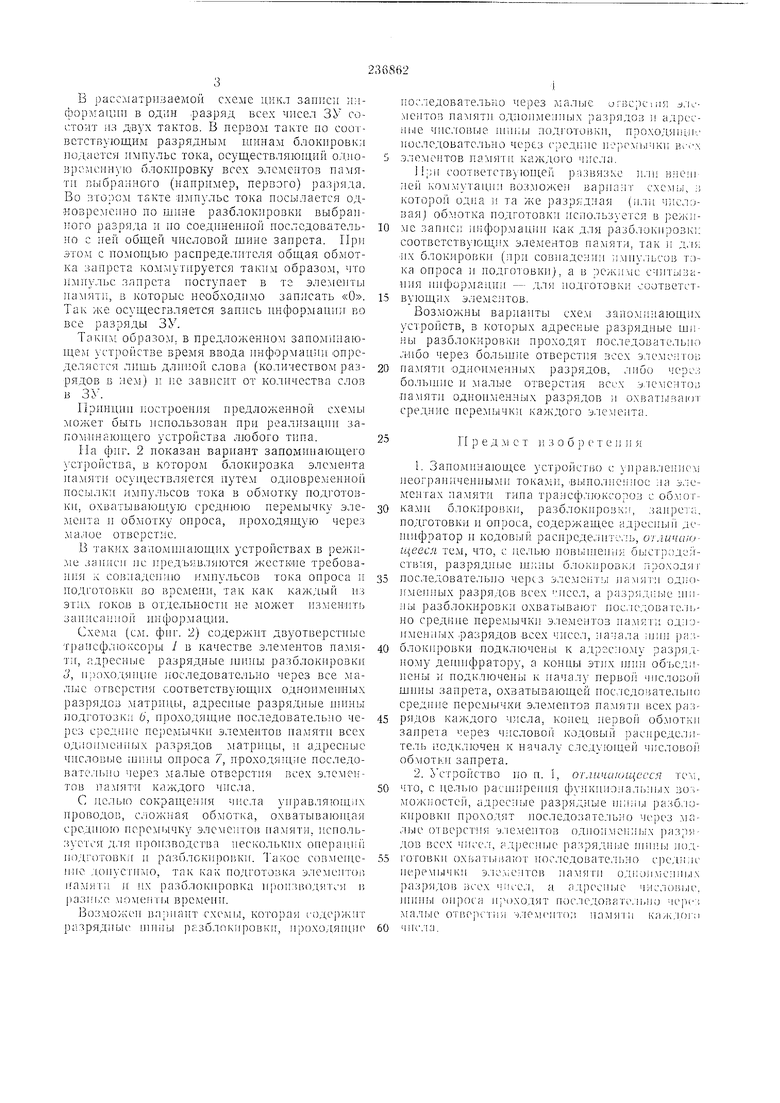

На фиг. 1 н 2 показаны варианты запоминающего устройства (ЗУ), построенного на двухотверетпых трансфлюкеорах.

Предложенное ЗУ может быть выполнено не только на двухотверстных трансфлюкеорах, но н на элементах памяти любого другого типа, например на четырехотзерстных элементах.

Устройство (см. фиг. 1) содержнт двухотверетные трансфлюксоры /, разрядные шнны блокировки 2 и разблокировки ., числовые шины запрета 4, управляел1ые чиеловым кодовым раснрсделителем 5. Прн этом начала разрядиых шин разблокировки подключены к соответствующим выходам адресного разрядного деишфратора, а концы объединены в общую точку и подключены с помощью распределителя к началу первой ншны запрета (первой можно считать любую числовую шипу запрета) конец которой подключен к началу второй числовой шины заирета и т. д. последовательно по всему запоминающему устройству.

Запись информации в ЗУ осуществляется последовательными циклами. Причем ввод инфор.ации в одковременпые разряды всех чнсел пропзводится одновременно одним циклом записи.

В рассл1атрн7заемой схеме цикл записи ;i;iформации в один .разряд всех чисел ЗУ состоит из двух тактов. В первом такте по соответствующим разрядным шинам блокировки подается импульс тока, осуществляющий ол.новрс:мсмн ю блокировку всех элемситов памятп пыбраииого (например, первого) разряда. Во зто:)см такте 51дгпульс тока посылается одHOBpe},ieiino по шине разблокировки выбраппого разряда и ио соединепной последовательно с пей общей числовой шине запрета. При этом с помощью распределителя общая обмотка запрета коммутируется таким образол, что шпгульс запрета поступает в те эле: 1епты памяти, в которые необходимо записать «О. Так же осуществляется запись пнформаипи во все разряды ЗУ.

Такил1 образом, в предложенном запоминающем устройстве время ввода пнформапии определяегся лишь длиной слова (количеством разрядов в нем) и не зависит от количества слов в ЗУ.

Принцип ноетроения предложепной схемы л о/кет быть использован при реализации запоминающего устройства любого типа.

На фиг. 2 показан вариант запоминающего устройства, в котором блокировка элемепта нал1яти осуи1,ествляется путем одиовременной по/сылки импульсов тока в обмотку подготовки, охватывающую среднюю перемычку эле.А1епта и обмотку опроса, проходящую через малое отверстие.

В таких заломпиающпх устройствах в режи,ie занисп пс предъявляются жесткие требоваиия к совпадению кмпульсов тока опроса и подготовки во времени, так как каждый из этих roKOiB в отдельности не может изменцт.ь заиисаиио инфор.лшции.

Схема (с.м. фиг. 2) содержнт двуотверстпыс т|)аисфлюксоры 1 в качестве элементов пал1яти, адресные разрядные шины разблокировки J, п;,оходяпи е последовательно через все малые отверетия соответствующих однопмениых разрядов матрппы, адреспые разрядпые пшны подготовки 6, проходящие последовательно через средние пе)емычкн элемептов памяти всех одноименных разрядов атрицы, и адрееные числовые илины опроса 7, проходяи;ие последовате.тьио через малые отверс1Т1я всех злеме тов па:ляти каждого чиела.

С иелыо сокращения числа унравляюидих нроводов, сложная обмотка, охватываюнтая среднюю нерсм1 чку элемеитОВ памяти, исполь.зуетчя для нроизводства нескольких операннй иодг1УГ()вк; и разблокироики. Гакое совмеи1еппе лопусгпмо, так как подготовка элементоп каммти и их разблокировка п1)оизв(Хипси li ,:е MO eriTf,i времени.

3озлгожен в,1;)нант схемы, которая 1одсржит разрядные П1ННЫ разблокировк, 1гроход,яп1,ио

последовательно через Л1алые игвсрси1Я ;,чментов памяти однонмениых и ад)есHiiie чиеловые нгины п()ДГ{), проходяп1,пс последовательно через среднпе 1г ремычки ъ.. элементов памяти каждого чис.та.

соответствующей р;13вязке 1ли внеш ;1ей KOAiMyTaiuiH возможен вариант cxeMiji, з которой одна и та же разрядная (}1л-и числэзая) обмотка подготовки используется в реж)ме записи информации как для разблокировк ; соответствующих элементов памяти, так и для их блокировки (при еовнадении имиульсов тока опроса и иодготоБКИ), а в режиме сч1пъ зання инфор.мапин - для нодготовки соответствующих элемситов.

Возможны варианты схем загюминающих устройств, в которых адрееные разрядные шины разблокировки ироходят последователыго ЛИбо через больпл е отверетия всех элементов

памяти одноп.менньгх разрядов, лнбо через болынне 1 малые отверстия всех Э1ементо.; памяти одноил;ен,ньгх разрядов и охвать зак)т средние перемычки ка/1сдого элемента.

. Заномннающее устройство с улравленнсм иеогранг1чениыми токами, еыполиенное на элементах намятн тина транефлюксороз с обмогкамн блокировки, разблокировкг:, зан)ег;;, подготовки и опроса, содержащее алресныГ дсншфратор и кодовый расиределитель, отличающееся те.м, что, с ие.чью новьпнення быстроде; ствия, разрядные шины блскчировк.ч п: эхоля

последовательно через элел;енты намягн однои.меииых разрядов всех |исел, а разрял, nniны разблокировки охватывают иоследовате.и,но среднпе перемычки элементов иа.д1яти однэнме.нных разрядов всех чисел, на-1ала шин р; :;блокировки подключены к адресному разрядному дегппфратору, а копны этих )пии обьединены и подключены к началу nepBOii числово шпны занрета, охватывающей последозате шно средние перели(чки элементов памятп веехразрядов каждого , конец первой об.моткн занрета через Ч;1е.товой кодовый распределитель по.т,ключен к началу следующей числово1 обмоткн занрета.

2. Устро ство по п. 1, отличшощссся тем,

что, с и.е.иио расншрення фун аиго;1альн1 1х зозможностс, адресные разрядные нкшы разблокнровкн нрохолят ноеледозательно через : iajuiie о1ве 1ст-ия -элементов однон 1ени1; х |)а:{рядов всех чнсел, Дре( разрядн 1е ншны иодготовкн охваплиаюг носледовательно средние нерем1) 3:ie.;eHTOii нал;яти одноименных разряд(Н5 iicex чп1-ел, а. ал 1есиые MHCHOIUJIC, HiHHF) онроса нр1)ходят пocлeдoзятeлlJH;J черм/ч мал.ле от11е|1стия -),те.(чггоз памяш Ka/i;;iorii

чнсма.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU236863A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU254205A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU341083A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU300890A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU335719A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1967 |

|

SU216795A1 |

| Логическое запоминающее устройство | 1972 |

|

SU442512A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Запоминающее устройство | 1973 |

|

SU446108A1 |

| АССОЦИАТИВНО-АДРЕСНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU336697A1 |

Даты

1969-01-01—Публикация