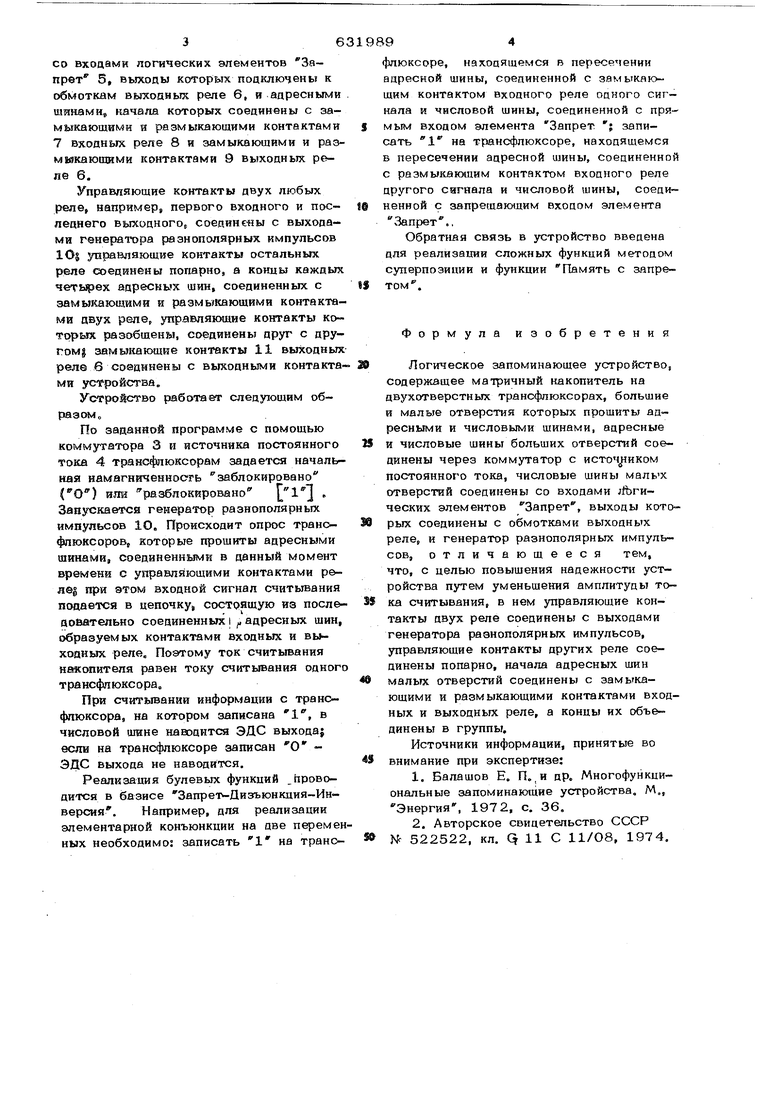

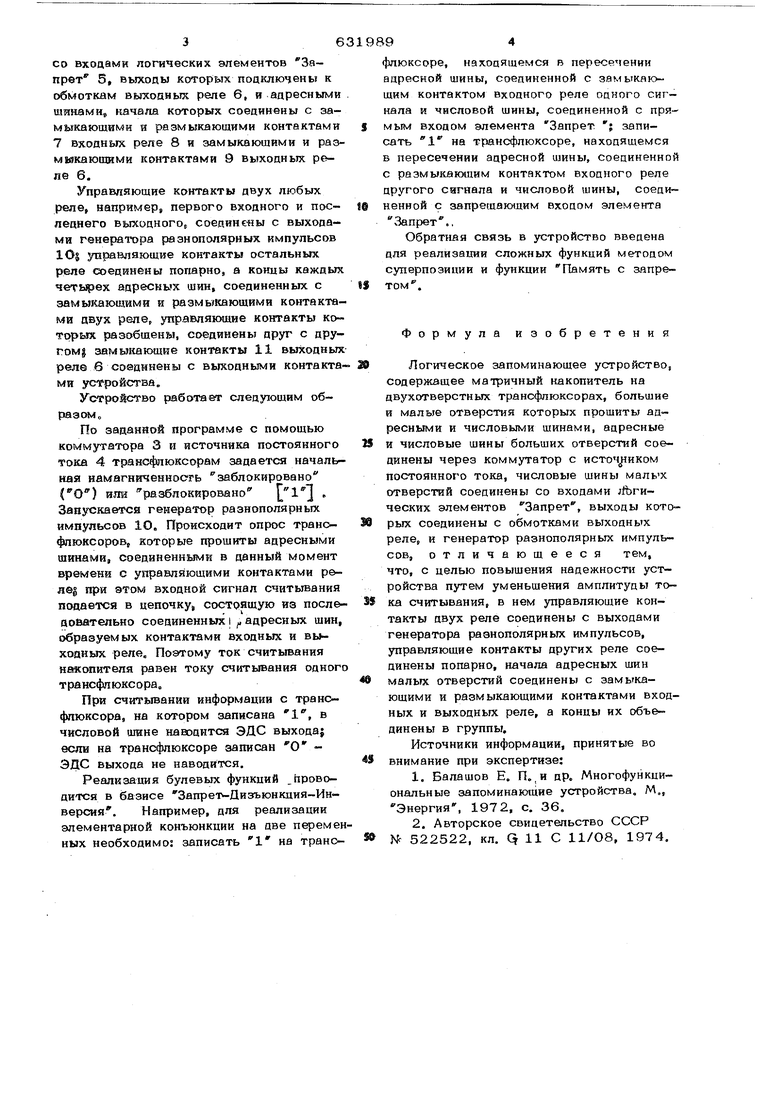

Изобретение относится к автоматике и может быть использойачо в качестве универсального логического автомата для автоматизированных систем управления, Известны логические запоминающие устройства, содержащие матрицу не цвух отверстных трансфлюксорах, большие и малые отверстия которых прошиты вертикальными и горизонтальными шинами f В этих устройствах реализация логических функций организована сложным образом и требует специального програм много управляющего блока. Наиболее близким по технической сущ ности к изобретению является логическо запоминающее устройство, содержащее матричный накопитель иа двухотверютных трансфлюксорах, большие и малые отверстия кгторых прошиты адресными и числовыми шинами, адресные и числовые шины больших отверстий соединены через коммутатор с источником постоянно тока, числовые шины малых отверстий соединены со входами логических элементов Запрет, выходы которых соединены с обмотками выходных реле, и генератор разнополярных импульсов Г21. Целью изобретения является повышение надежности устройства путем уменьшения амплитуды тока считывания. Эта цель достигается тем, чт-о в устройстве управляющие контакты двух реле соединены с выходами генератора разнополярных импульсов, управляющие контакты других реле соединены попарно, начала адресных шин малых отверстий соединены с замыкающими и размыкающими контактами входных и выходных реле, а концы их объединены в группы. На чертеже представлена принципиальная электрическая схема устройства. Устройство содержит матричный накопитель 1 на двухотверстных трансфлюк- сорах 2. Большие отверстия трансфлюксоров прошиты адресными (вертикальнььми) и числовыми (горизонтальными) шинами, подключенными через коммутатор 3 к источнику 4 постоянного тока. Малые отверстия трансфлюксорон; прошиты числовыми ишиами, соединенными 6 CO входами логических элементов Запрет 5, выходы которых подключены к обмоткам выхонных реле 6, и адресными шинамИе качала которых соединены с замыкаюшими и размыкающими контактами 7 входных реле 8 и замыкающими и размикающими контактами 9 выходных репе 6. Управляющие контакты двух любых реле, например, первого входного и последнего выходного соединены с выходами генератора разнополярных импульсов 1О| уЕравляющие контакты остальных реле соединены попарно, а концы каждых четьфех адресных шин, соединенных с эамы1Шющими и размыкающими контактами двух релОр управляющие контакты ко тррьпс разобщены, соединены друг с цругом| замыкающие контакты 11 выходных реле 6 соединены с выходными контакта ми устройства. Устройство работает следующим образом „ По заданной программе с помощью коммутатора 3 и источника постоянного тока 4 трансфлюксорам задается начальная намагниченносгь заблокировано (О) или разблокировано Запускаетси гекерагор разнополярных импульсов 10, Происходит опрос трансфлюксоров, которые прошиты адресными шинами, соединенными в данный момент времени с управляющими контактами релв| при этом входной сигнал считывания подается в цепочку, сострящую из послейовательно соединенных l адресных шин, образуемых контактами входных и выходных реле. Поэтому ток считывания накопителя равен току считывания одного траисфлюксора, При считывании информации с трансфпюксора, на котором записана , в числовой шине наводится ЭДС выхода; если на трансфлюксоре записан О ЭДС выхода не наводится. Реализация булевых функций hpoBoдится в базисе Запрет Дизъюнкция-Инверсия. Например, для реализации элементарной конъюнкции на две перемен ных необходимо: записать 1 на трано94флюксоре, назсоцящемся в пересечении ацресной шины, соеаиненной с замыкающим контактом Входного одного сигнала и числовой шины, соецкненной с прямым входом элемента Запрет ; записать 1 на трансфлюксоре, находящемся в пересечении адресной шины, соециненной с размыкающим контактом входного реле другого сигнала и числовой шины, соединенной с запрешаклдим входом элемента хЗапрет., Обратная связь в устройство введена для реализации сложных функций методом суперпозиции и функции Память с запретом. Формула изобретения Логическое запоминающее устройство, содержащее матричный накопитель на двухотверстных трансфлюксорах, большие и малые отверстия которых прошиты адресными и числовыми шинами, адресные и числовые шины больших отверстий соединены через коммутатор с источ 1иком Постоянного Toita, числовые шины мальх отверстий соединены со входами jfbrHческих элементов Запрет, выходы которых соединены с обмотками выходных реле, и генератор разнополярных импупьсов, отличающееся тем, что, с целью повышения надежности устройства путем уменьшения амплитуды тока считывания, в нем управляющие контакты двух реле соединены с выходами генератора раэнополярных импульсов, управляющие контакты других реле соединены попарно, начала адресных шин отверстий соединены с замыкающими и размыкающими контактами входных и выходных реле, а концы их объединены в группы. Источники информации, принятые во внимание при экспертизе: 1.Балашов Е. П.,и др. Многофункциональные запоминающие устройства. М., Энергия, 1972, с. 36, 2.Авторское свидетельство СССР № 522522, кл. Q 11 С 11/О8, 1974, .WS4w ill I IIi I hill It M и и -i

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое программное устройство | 1974 |

|

SU522522A1 |

| Логическое программное устройство | 1976 |

|

SU643881A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU335719A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU236863A1 |

| МАГНИТНЫЙ НАКОПИТЕЛЬ | 1973 |

|

SU385315A1 |

| Запоминающее устройство | 1973 |

|

SU446108A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1967 |

|

SU216795A1 |

| Логическое устройство | 1972 |

|

SU527016A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1976 |

|

SU634373A1 |

| Логическое полноточное запоминающее устройство | 1974 |

|

SU470861A1 |

Авторы

Даты

1978-11-05—Публикация

1976-09-27—Подача