Изобретение относится к области вычислительных устройств, обрабатывающих частотноимпульсную информацию. Оно может быть использовано в качестве автономного математического узла либо в сочетании с частотноимпульсиыми моделями.

В известных устройствах подобного иазначения управление 1мпульсно-потенциальной схемой совпаден1ия, регулируюш,ей поступление одной из частот, осуществляется только входным триггером. Это ириводит к существенному ограничению выходного параметра скважности импульсов в пределах не более 0,5 и при использовании этих устройств в частотно-импульсных .моделях замкнутого типа снижает диапазон их работы и ограничивает круг реи аемых задач умножением, делением и возведением в квадрат.

Цель описываемого изобретения заключается в расширении диапазона одного из входных аргументов, т. е. в изменении скважности в П:ределах О-1, что в свою очередь позволяет расширить возможности существующих моделей и выполнять с их помощью операции извлечения корня квадратного, решения алгебраических уравнений второй степени и т. д.

Указанная цель достигается иутем постановки дешифратора, связанного с одноименными выходами входного и выходного триггеров, уоравляющего распределением входной частоты

через две импульсно-потенциальные схемы совпадения.

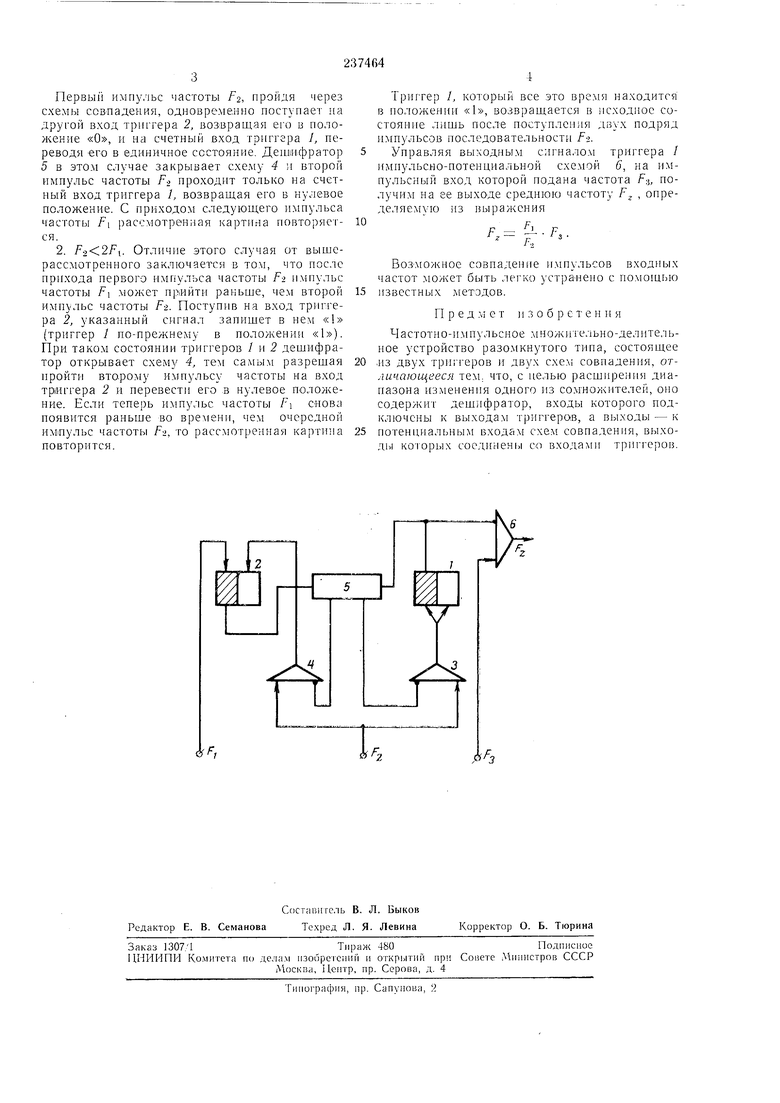

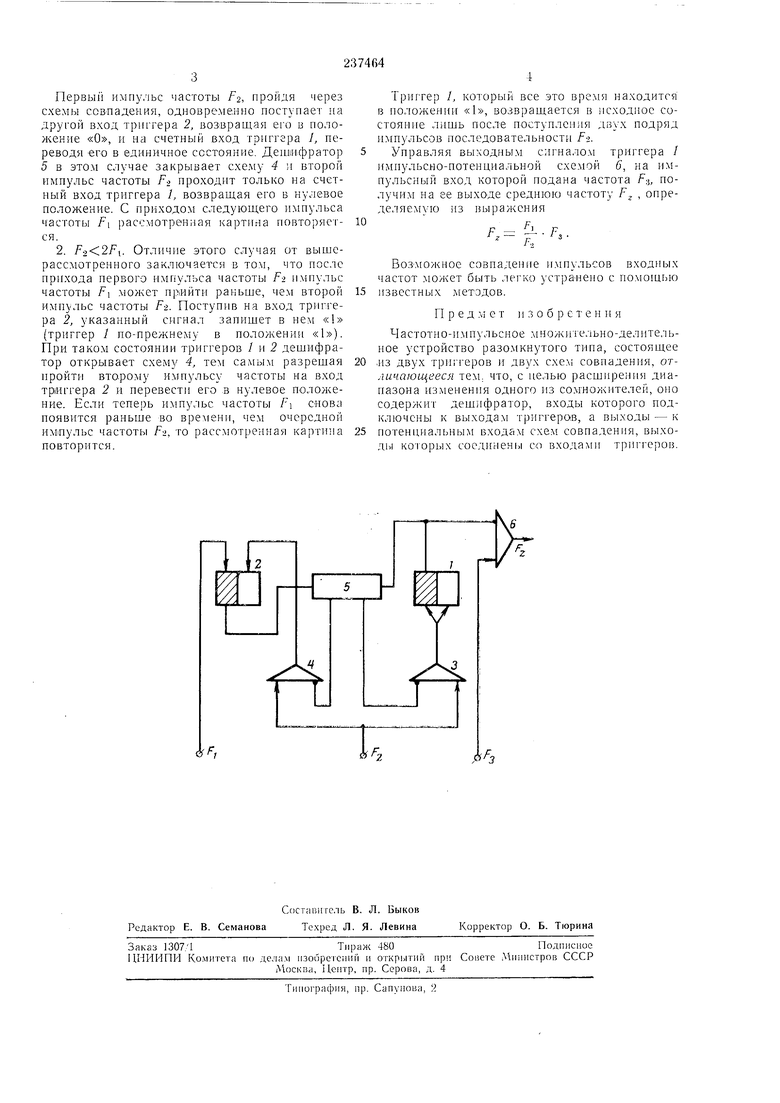

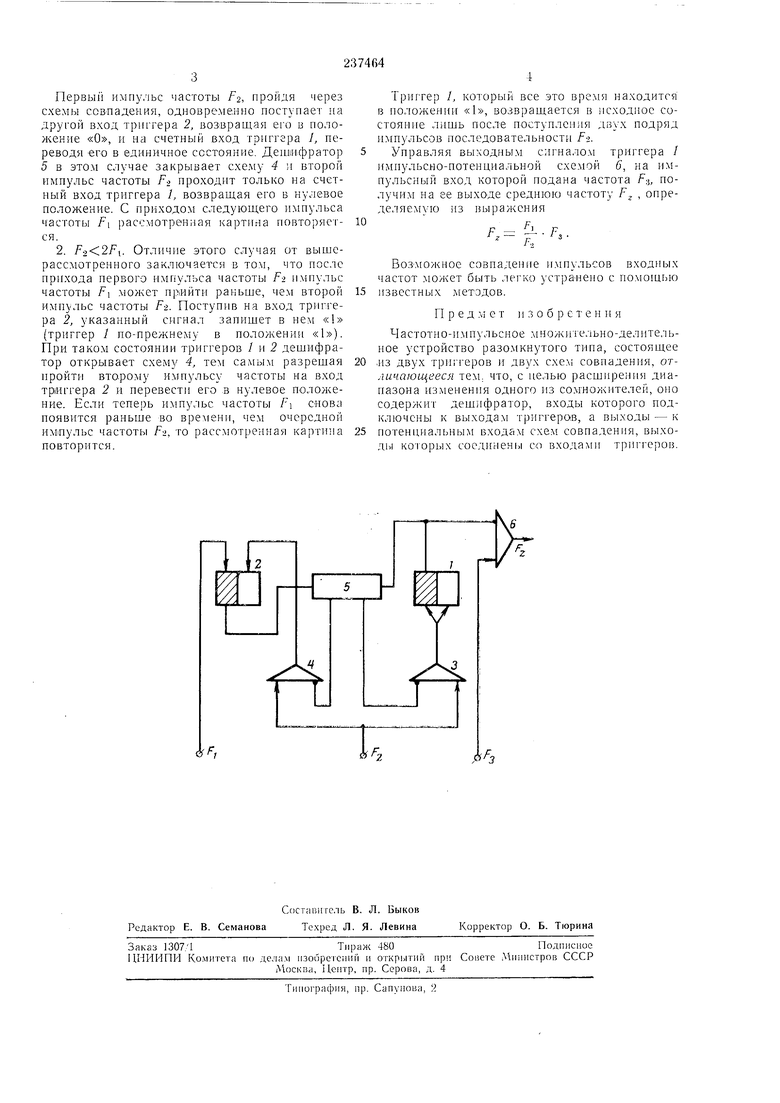

На чертеже иредставлеиа блок-схема устройства.

стройство состоит из двух триггеров / и 2, двух импульсно-потенциальных схем 3 и 4 совпадения и дешифратора 5. Выход триггера / соединен с потенциальным входом импульснопотенциальной схемы 6. на второй вход которой подается входная переменная.

Две другие переменные подаются на установочный вход триггера 2 и импульсные входы схем 3 и 4 совпадения соответственно. Основным узлом, определяющим логику работы описывае.мого устройства, является дешифратор, уп)авляющий имиульсно-потенциальными схемами 3 и 4 в зависимости от состояния триггеров 1 и 2. Рассмотрим работу устройства для двух характерных случаев, определяемых cooTHOuieниям:и входных частот .Fi и р2.

I. FZ 2/i. В исходный момент времени триггеры 1 п 2 находятся в нулевом положении. В соответствии с логикой работы выходные сигналы дешифратора обеспечивают закрытое состояние схем 3 и 4.

После поступления иервого импульса частоты F на вход триггера 2 и записи в нем «1 дешифратор 5 открывает одновременно схемы

Первый импульс частоты F, пройдя через схемы совпадения, одновремелпо поступает па другой вход трпггера 2, возвращая его в положение «О, и па счетный вход трпгггра 1, переводя его в единичное состояние. Дешифратор 5 в этом случае закрывает схему 4 и второй импульс частоты -F проходит только на счетный вход триггера /, возвращая его в нулевое положение. С приходом следующего нмиульса частоты F рассмотренная картина иовторяется.

2. р2.2р1. Отличие этого случая от вышерассмотренного заключается в том, что после прихода первого импульса частоты F-2 импульс частоты FI может пр1ийти раньше, чем второй имиульс частоты F. Поступив на вход триггера 2, указанный сигнал запищет в нем «1 (триггер / по-прежнему в положении «1). При таком состоянии триггеров / и 2 дешифратор открывает схему 4, тем самым разрешая иройти вто.рому импульсу частоты на вход триггера 2 и иеревести его в нулевое положение. Если теперь импульс частоты F снова появится раньше во времени, чем очередной имлульс частоты F-2, то рассмотренная картина повторится.

Триггер /, который все это время находится в положении «1, возвращается в исходное состояиие лишь после иоступлсиия двух подряд импульсов последовательности F-2.

Уиравляя вылодны.м сигналол триггера / импульсно-потенциальной схемой 6, на импульсный вход которой иодаиа частота f.-j, иолучим на ее выходе среднюю частоту F , определяемую из выражения

f,

F,

F -

F.,

Воз гожнос совнадение и.мпульсов входных частот может быть легко устра иено с по.мощью известных методов.

Пред м е т и з о б р с т е н и я

Частотно-импульсное множительн о-делительное устройство разомкнутого типа, состоящее

.из двух триггеров и двух cxe.i совпадения, отличающееся тем. что, с целью расширения диаиазоиа измеиения одного из сомножителей, оно содержит дешифратор, входы которого подключены к выходам триггеров, а выходы - к

потенциальным входам схем совпадения, выходы которых соединен) со входами триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ИМПУЛЬСНОЕ ВЫЧИТАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU423125A1 |

| ОДТЕНТНО-ТЕХНН-Г- :^':и|БИБЛИОТЕКА | 1970 |

|

SU287404A1 |

| Детектор разности частот | 1987 |

|

SU1518874A1 |

| Реле частоты | 1980 |

|

SU951456A1 |

| ПРОЦЕНТНЫЙ ВРЕМЯ-ИМПУЛЬСНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1971 |

|

SU429526A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО РАЗОМКНУТОГО ТИПА | 1970 |

|

SU276519A1 |

| Частотно-импульсное множительноделительное устройство | 1976 |

|

SU574717A1 |

| Импульсный синхронизатор | 1983 |

|

SU1141510A2 |

| Устройство для сравнения частот сигналов | 1985 |

|

SU1323973A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ВРЕМЕННОГО ИНТЕРВАЛА | 1973 |

|

SU368584A1 |

Даты

1969-01-01—Публикация