Предложенное устройство относится к области вычислительной техники.

Известны устройства двухиредельного сравнения чисел, содержащие схемы сравнения, логические схемы, шины ввода чисел, шины опроса, анализаторы, схемы ввода и вывода чисел, запоминаюш,ие устройства.

Предлагаемое устройство отличается от известных тем, что в нем выходы вентилей ввода чисел «верхнего и нижнего пределов сравнения объединены, выходы шин разрешения «.верхнего и нижнего пределов подключены к противопололсным выходам управляющего триггера, а выходы поразрядных щин «больше схем сравнения соединены с собирательными схемами первой группы, с первыми входами вторых вентилей поразрядного сравнения, вторые входы которых соединены с шиной ввода числа «нижнего предела. Кроме того, эти же шины схем сравнения через дноды и инверторы подключены к первым входам схем «ИДИ-НЕ, выходы которых через интегрирующие цеиочки, собирательные схемы подключены к шинам опроса вентилей ввода младщих разрядов чисел и через диоды соединены со входами инверторов.

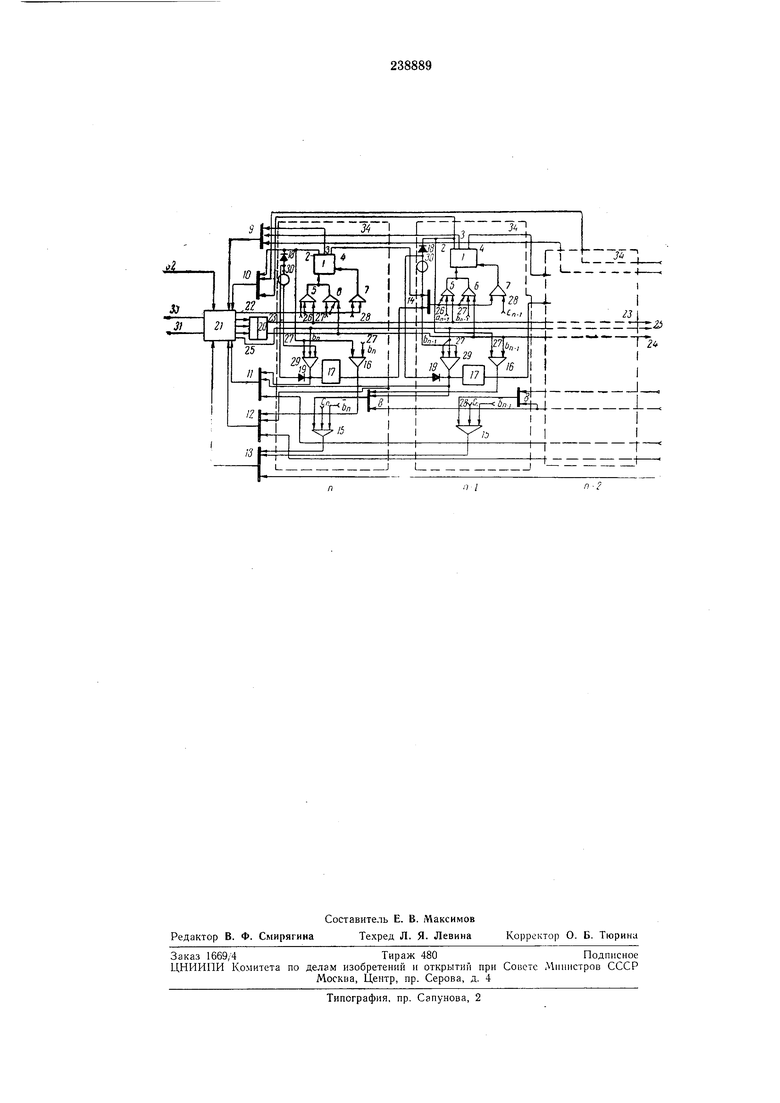

Она содержит логические схемы сравнения / разрядов двух двоичных чисел, включающие выходы поразрядных шии «больше 2, «меньще 3, «равно 4; вентили ввода чисел 5-л собирательные схемы 8; первую 9, 10 и вторую 11-13 группу собирательных схем, третью группу собирательных схем М; первые 15 и вторые 16 вентили поразрядного сравнения, интегрирующие цепочки 17, диоды 18, 19; управляющий триггер 20, анализатор 21, шины 22 опроса вентиля ввода разрядов чисел, шины разрешения ввода чисел «верхний предел 23 и «нижний предел 24, щину «установки нуля 25, щины параллельного ввода чисел «верхний предел 26, «нижний предел 27 и «сравниваемое число 28 в логические схемы поразрядного сравнения, схемы «ИЛИ-НЕ 29, инверторы 30, шины команд «не совпало 31, «сравнивай 32, «совпало 33, логический узел 34.

Устройство работает следующим образом.

По команде «сравнивай, постуиающей по шине 32, анализатор 21 формирует сигнал опроса, который опращивает входные вентили ввода 5-7 п,-ных разрядов (где п-иоме. старшего разряда) чисел.

дел (aj и «сравниваемого числа (С). Схема У в зависимости от соотношения указанных разрядов формирует один из выходных сигналов: «больше 2, «меньше 3 или «равно 4. При этом сигнал «равно служит командой опроса для вентилей ввода 5-7 младших разрядов указанных чисел, сигнал «меньше через собирательную схему 9 поступает в анализатор 21, а сигнал «больше через собирательную схему 10 - в анализатор 21.

На второй вход вентиля 16 по шине 27 параллельного ввода поступает значение п-ого разряда (Ь„) числа «нижний предел. Оно же поступает через диод 18 и инвертор 30 на вход схемы ««ИЛИ-НЕ 29, второй вход которой соединен с шиной «установки нуля 25, а третий - с шиной параллельного ввода разряда Ь„ числа «нижний предел 27.

Если , то на выходе вентиля 16 формируется сигнал, поступающий через собира тельную cxeiMy 12 в анализатор 21, который формирует при этом ответ «не совпало 31. Если указанный сигнал с выхода вентиля 16 формируется не в ге-ном логическом узле 34, например в п-1, то он поступает не только в анализатор 21, но и через собирательные схемы 8 на входы вентилей 15 всех старших разрядов, на другие входы которых по шинам параллельного ;ввода иоступают значения соответствуюпдих р азрядов чисел «нижний предел и «сравниваемое число.

Еслн на входах хотя бы одного из опрашиваемых вентилей 15, имеется комбииация значений разрядов такая, что С, 1, Ь, 0, где К . то на выходе вентиля 15 нри этом формируется сигнал, иостунаюший через собирательную схему 13 в аиализатор 21, формирующий в данном случае ответ «совпало 33.

Если значение разряда Ь„ (или любого другого 1-го) числа «нижний предел такое, что , то сигнал «больше, ноступающий через инвертор 30 на вход схемы «ИЛИ-НЕ 29, онрашивает последнюю, и на ее выходе при этом фор.мируется сигнал, поступающий в цепи опроса вентилей 15 (аналогично сигналу с вентилей 16) через интегрирующую цепочку 17 (на чертеже дальше связи не указаны), собирательную схему 14 в шину 22 опроса вентилей ввода младших разрядов, через собирательную схему // в анализатор 21, а также через диод 19 на вход инвертора 30.

Если ни один из опрашиваемых вентилей 16 не вырабатывает выходной сигнал, то анал затор 21 формирует посылку, устанавливающую триггер 20 в состояние, при котором разрешающий потенциал подается по соответствующей шине 24 на вентили 6 ввода разрядов числа «нижний предел. К моменту фиксирования указанного состояния сигнал с выхода интегрирующей цепочки 17 опрашивает вентили ввода младших разрядов 5-7, при этом в логической схеме / (соответствующего узла 34) сравниваются разряды числа «нижний предел и «сравнивае.мое число.

Сигналы «больше или «.меньше через собирательные с.хемы 10 и 9 соответственно поступают в аиализатор 21, формующий в нерво.м случае ответ ;не сознало, а во втором «совпало. Сигнал «равно служит сигналом опроса вентилей ввода младших разрядов 5-7.

Предмет изобретения

Устройство для двухнредельного сравнения п-разрядных двоичных чисел, содержащее анализатор, соединенный с шиной опроса, с шина.ми команд, управляющи.м триггером, первой, второй группами собирательных схем, схемы сравнения с выходами «больше, «равно и «меньше, соединенные с нервой и третьей группа.ми собирательных схем и с вентилями ввода чисел, интегрирующие цепочки, соединенные непосредственно с собирательными схемами, первые вентили поразрядного сравнения связаны со второй группой собирательных схем, схемы «ИЛИ-НЕ, инверторы, отличающееся тем, что, с целью повышения быстродействия устройства, в нем выходы вентилей ввода чисел «верхнего и нижнего пределов сравнения объединены, выходы шин разрешения «верхнего п нижнего нределов нодключены к противоноложны.м выходам управляющего триггера, а выходы поразрядных шин «больше схе.д сравнения соединены с собирательными схемами первой группы, с нервы.ми входами вторых вентилей

5 поразрядного сравнения, вторые входы которых соединены с шиной ввода числа «нижнего предела, кроме того, эти же шины схем сравнения через диоды и инверторы подключены к первым входам схем «ИЛИ-НЕ, выходы

которых через интегрирующие цепочки, собирательные схемы нодключены к шинам опроса вентилей -ввода младших разрядов чисел и через диоды соединены со входами инверторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРО-АНАЛОГОВОЕ УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ | 1970 |

|

SU266363A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| СТРУЙНОЕ УСТРОЙСТВО для ПОСЛЕДОВАТЕЛЬНОГО ПОРАЗРЯДНОГО СРАВНЕНИЯ ДВУХ ДВОИЧНЫХ ЧИСЕЛ | 1973 |

|

SU404074A1 |

| УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВУХ ДВОИЧНЫХ ЧИСЕЛ | 1968 |

|

SU218529A1 |

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКИХи | 1971 |

|

SU316086A1 |

| Устройство для сравнения " " дискретных величин | 1970 |

|

SU366472A1 |

| Цифровые электронные часы | 1978 |

|

SU779967A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU269216A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ т-РАЗРЯДНЫХ ДЕСЯТИЧНЫХ ЧИСЕЛ НА ОДНОРАЗРЯДНОЕ ДЕСЯТИЧНОЕ | 1973 |

|

SU392497A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

Даты

1969-01-01—Публикация