Изобретение относится к устройствам, выполняющим обработку чисел с повышенной точностью и входящим в состав цифровых вычислительных машин.

Известно устройство для умножения чисел, представленных .в обратном коде, со сдвигом частных произведений вправо, анализом множителя, начиная с младших разрядов и с учетом знака, сохранением младшей части произведения в регистре множителя и с автоматическим исправлением младшей части произведения.

Однако недостатком этого устройства является непременное двузначное представление нуля в -сумматоре. Очень часто сумматор арифметического устройства помимо обработки числовой информации используется для выполнения арифметических и логических операций над адресной информацией вычислительной машины. В этих случаях двузначное представление нуля вызывает существенные трудности при реализации названных операций.

Известное же устройство умножения невозможно реализовать при использовании сумматора обратных кодов с блоки1ровкой отрицательного нуля.

Таким образом, целью изобретения являет:я автоматическое исправление значения младшей части произведения, т. е. повыщение точности умножения при использовании любой Схемы сумматора обратных кодов.

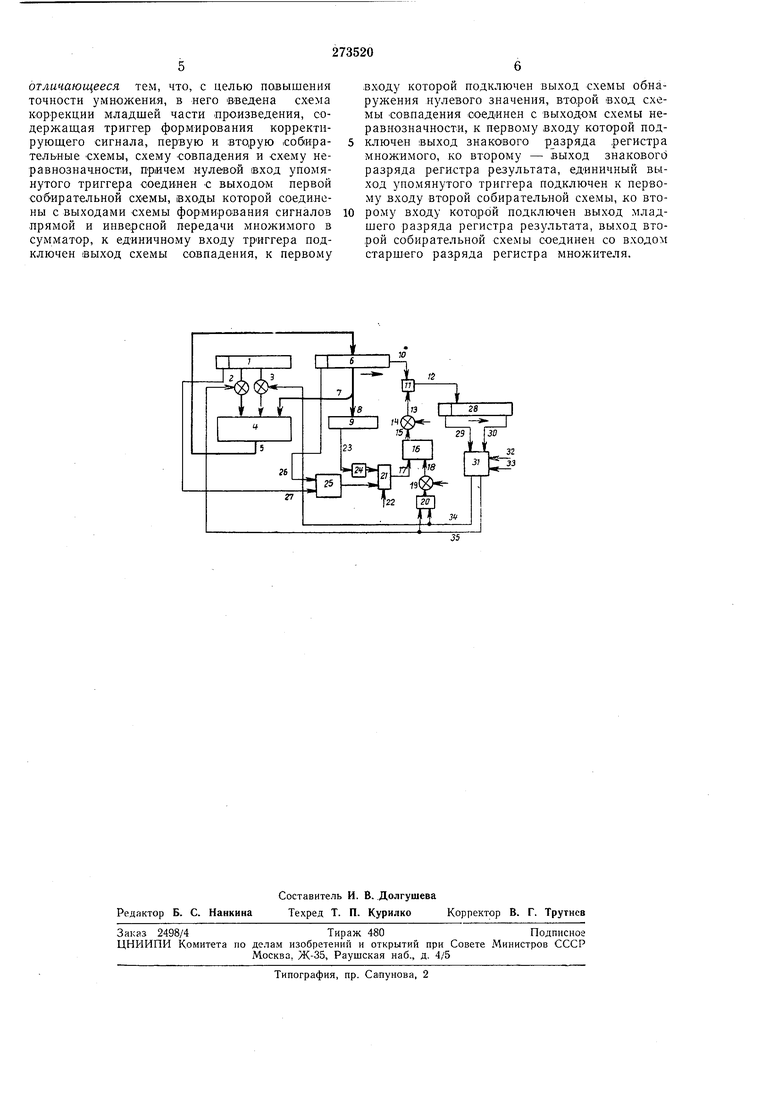

Сущность изобретения состоит в том, что вводится логическая схема, осуществляющая корректирование значения разряда, сдвигаемого из регистра результата в регистр мнол ителя, непосредственно на входе старшего разряда регистра множителя. На чертеже изобрал-сена блок-схема описываемого устройства умножения, содержащая следующие узлы и цепи:

/ - регистр для хранения мнол имого; 2 и 3 - вентили для прямой и инверсной передачи множимого в сумматор; 4 - параллельный

сумматор обратных кодов; 5 - шины для передачи частного произведения из сумматора в регистр результата 6; 6 - регистр результата для хранения и сдвига частных произведений; 7 - шины передачи частного произведения на вход сумматора; 8 - шины передачи кода регистра результата на вход схемы 9 обнарул ения нулевого значения; 10 - шина передачи значения сдвигаемого младшего разряда регистра результата 6 в старший разряд

регистра мнол ителя; 11-собирательная схема; 12 - шина передачи скорректированного значения сдвигаемого младшего разряда регистра результата 6 в старший разряд регистра мнол ителя; 13 - шина передачи корректирую14 - вентиль стробирования выдачи корректирующего сигнала; 15 - выходная шина с единичного плеча триггера /6 формирования корректирующего сигнала; 17 - шина установки единицы в триггере формирования корректирующего сигнала; 18 - шина установки нуля в триггере 16 формирования корректирующего сигнала; 19 - вентильная схема стробирования сигнала установки нуля ,в триггере 16; 20 - собирательная схема для управляющих сигналов прямой и инверсной передачи множимого на вход сумматора; 21 - схема совпадения для формирования сигнала установки триггера 16 в единицу; 22 - шина стробироваиия сигнала установки единицы в триггере 16; 23- шина передачи -сигнала со схемы 9 обнаружения нулевого значения; 24 - инвертор; 25-схема неравнозначности; 26 - шина передачи значения знакового разряда регистра результата 6 на вход схемы неравнозначности 25; 27 - шина передачи значения знака множимого на вход схемы неравнозначности 25; 28 - сдвигающий регистр множителя; 29 - шина передачи значения знакового разряда регистра множителя 28 на вход схемы формирования 31 сигналов прямой и инверсной пер едачи мнол-симого на вход сумматора; 30 - шина передачи значения младшего разряда регистра множителя 28 на вход схемы формирования 31; 32 - шина сигнала начала формирования сигналов прямой или инверсной передачи множимого; 33 - шина сигнала окончания формирования сигналов прямой или инверсной передачи множимого; 34 - шина инверсной передачи множимого «а вход сумматора; 35 - шина прямой передачи множимого на вход сумматора.

Умножение .в данном устройстве выполняется следующим образом.

Множимое хранится в регистре 1. В подготовительном цикле операции умной ;ения с приходом сигнала по шине 22 нроизводится установка триггера 16 в единичное состояние лишь в том случае, если схема неравнозначности 25 выдаст единичный уровень на вход схемы совпадения 21 и схема 9 обнаружения нулевого значения выдаст на шине 23 уровень, соответствующий не нулевому значению кода регистра результата, где во время подготовительного цикла находится множитель. В конце подготовительного цикла множитель был нереписан из регистра результата 6 в регистр множителя 28. Множитель хранится в сдвигающем регистре 28. В сдвигающем регистре 6 хранится частное произведение (старшая часть). В каждом цикле умножения схема формирования 31 на основании анализа значений младш,его и знакового разрядов формирует с помощью сигналов управления, поступающих по шинам 32 и 33, сигналы передачи мнолшмого. При равенстве абсолютного значения анализируемого разряда множителя нулю формирование сигналов нередачи множимого не производится. На второй вход сумматора 4 по шинам 7 поступает частное произведение, хранимое в регистре 6 и полученное в нредыдущих циклах умножения. Сформированная сумма по шинам 5 передается из сумматора 4 в регистр 6, где сдвигается на один разряд вправо. Выпадающий за пределы разрядной сетки регистра 6 разряд частного произведения по шине 10 поступает на собирательную схему 11, где производится корректирование его значения, а затем по шине 12-

на вход старшего разряда регистра множителя 28. Этот разряд был освобожден при сдвиге множителя в регистре 28 на один разряд внраво, выполненном одновременно с суммированием в сумматоре.

Триггер 16 находится в состоянии «единица до тех нор, пока схема формирования не выдаст первого сигнала прямой или инверсной передачи множимого на вход сумматора по шине 35 или 34, который, пройдя собирательную схему 20 и вентильную схему стробирования 19, установит его в нулевое состояние. В каждом цикле умножения сигнал сдвига в регистре 6 поступает по шине на вентиль 14 стробирования выдачи корректирующего

сигнала, и, если триггер 16 находится в единичном состоянии, сигнал корректирования логически суммируется на собирательной схеме 11 со значением сдвигаемого из регистра ; разряда частного произведения. Скорректированное значение этого разряда по шине 12 поступает: на вход старшего разряда регистрами. Таким образом, если знаки сомножителей разные, т. е. нроизведение отрицательно, и абсолютные значения группы младших разрядов

множителя равны нулю, то поскольку регистр 6 находится в нулевом состоянии, .сдвигаемые разряды имеют нулевые значения И заполнение младшей части произведения, формируемой в регистре 28, единицами осуществляется

с помощью триггера 16 до тех пор, пока с анализом первого же разряда множителя, по абсолютному значению, не равному нулю, этот триггер не установится в нулевое состояние. Если длина упомянутой группы младших

разрядов простирается на всю длину множителя, т. е. множитель равен нулю, то уровень на выходе схемы 9 не позволит установить триггер 16 в «единицу и младшая часть произведения будет равна старшей или положительному нулю.

Применение данного устройства умножения позволяет повысить точность умножения чисел в обратном коде до 2 (где л -разрядность операндов) независимо от вида схемы

сумматора обратных кодов.

Предмет изобретения

Устройство для умножения чисел в обратном коде, содерл ащее сумматор обратных кодов, регистры множимого, множителя и результата, схему формирования сигналов прямой ,и инверсной передачи множимого в сумотличающееся тем, что, с целью повышения точности умножения, в него введена схема коррекции младшей части произведения, содержашая триггер формирования корректнруюшего сигнала, нервую и вторую собирательные схемы, схему совпадения и схему неравнозначности, причем нулевой вход упомянутого триггера соединен с выходом первой собирательной схемы, входы которой соединены с выходами схемы формирования сигналов прямой и инверсной передачи множимого в сумматор, к единичному входу триггера подключен выход схемы совпадения, к первому

входу которой подключен выход схемы обнаружения нулевого значения, второй вход схемы совпадения соединен с выходом схемы неравнозначности, к первому входу которой подключен выход знакового р азряда регистра множимого, ко второму - выход знакового разряда регистра результата, единичный выход упомянутого триггера подключен к первому входу второй собирательной схемы, ко второму входу которой подключен выход младшего разряда регистра результата, выход второй собирательной схемы соединен со входом старшего разряда регистра множителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1969 |

|

SU242499A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1972 |

|

SU357561A1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для ускоренного умножения двоичных чисел, представленных в обратном коде | 1974 |

|

SU522498A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения | 1985 |

|

SU1252774A1 |

Авторы

Даты

1970-01-01—Публикация