Предложенное устройство относится к области вычислительной техники.

Известны устройства для обнаружения ошибок, содержащие регистры сдвига, формирователи импульсов и cxBiMy контроля.

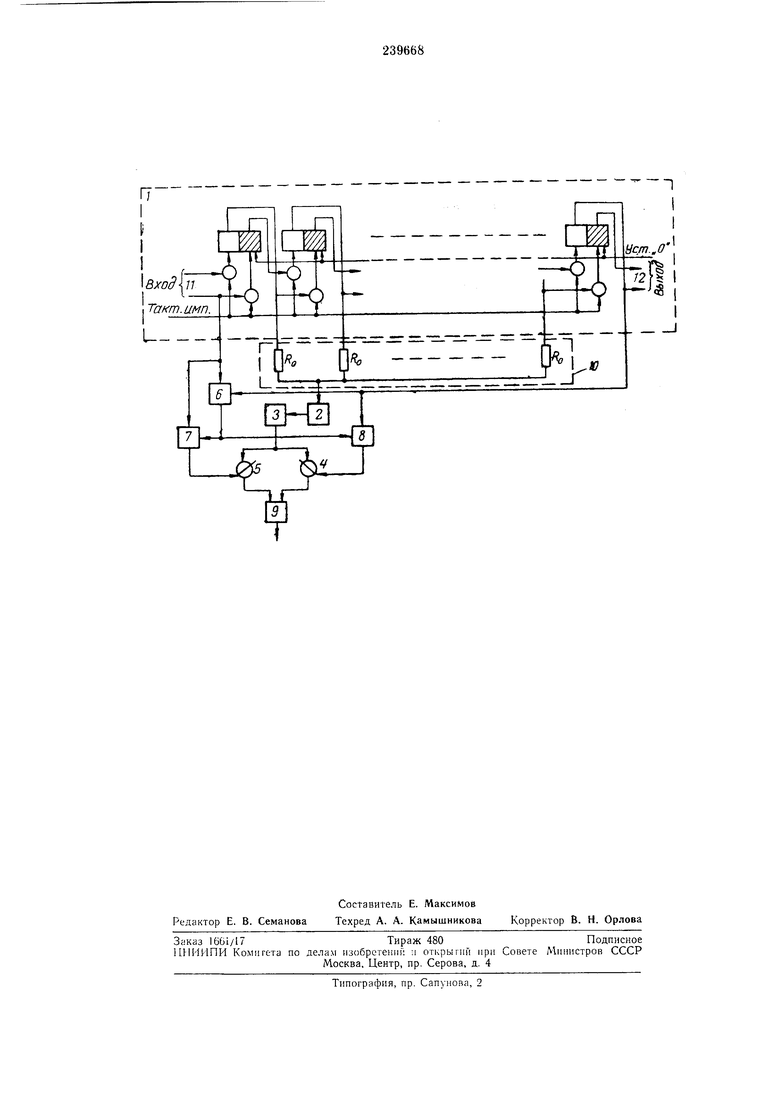

Предложенное устройство отличается от известных тем, что оно содержит сумматор по модулю два, логические схемы «И, «ИЛИ, дифференцирующую цепь, две схемы запрета. Первые входы первой схемы «И и сумматора подключены к соответствующей входной шине регистра, второй вход сумматора подключен к первому входу второй схемы «И и к соответствующей выходной щине регистра, а выход сумматора подключен ко вторым входам указанных схем «И, выходы которых подключены к запрещающим входам первой и второй схем запрета соответственно, причем вторые ьходы последних объединены и подключены к дифференцирующей цепи, а выходы схем запрета через схему «ИЛИ подключены к шине сигнала ошибки. На чертеже представлена схема описываемого устройства. Устройство содержит импульсно-потенциальный регистр 1, эмиттерный повторитель 2, дифференцирующую цепь 3, схемы запрета 4 и 5, сумматор 6 по модулю два, схе.мы «И 7 и 8 и схему «ИЛР 9, декодирующий преобразователь 10, входные Ни выходные 12 щины.

Устройство позволяет обнаружить ошибки при проверке следующей закономерности работы регистра: число единиц, записанное в нем после каждой операции сдвига, либо сохраняется, либо увеличивается на единицу (при последовательном вводе информации), либо уменьшается на единицу. В случае параллельного ввода информации число единиц после каждого такта может только уменьщаться на

0 единицу.

В качестве контролируемого регистра взят обычный импульсно-потенциальный регистр 1 на статических триггерах. Декодирующий преобразователь 10 в целях

5 максимального упрощения реализован в виде цифровых управляемых сопротивлений. Принцип действия такого преобразователя заключается в том, что если к каждому из весовых сопротивлений подключен генератор напряжения с выходным сопротивлением, равным нулю, и с напряжением 0s или Уов в зависимости от значения соответствующего разряда, то выходное напряжение преобразователя 10 всегда будет пропорционально взвешенной схмме в.ходных сигналов

n-l Ч

вых огде

Л; -значение 1-го разряда; У - проводимость весового соиротиБлення (-го входа преобразователя.

В схеме роль ключей, переключающих входы преобразователя W с напряжением Ов на напряжение УО, выполняют сами триггеры регистра /. Так как триггеры не являются идеальными генераторами напряжения за счет конечности выходного сопротивления, и кроме того, выходные наиряжения всех триггеров имеют некоторый разброс, то в результате этого точность такого преобразователя оказывается невысокой- бЬвых 0., где -вых-относительная погрешность выходного напряжения.

Сравнительно низкая точность декодирующего преобразователя вполне оправдывается простотой реализации и отсутствием жестких гребований на весовые сопротивления RQ.

С целью избежания запрета сигналов, вызванных многократными ошибками в регистре /, схемы « I 7 и S .можно за.менить схема.ми сравнения, пороговые уровни которых управляются сигналами Z и Z так, что при отсутствии порогового уровня напряжения ,

а при наличии напряжения l,5ft -5,

где UQ - опорное напряжение; п - число разрядов регистра.

Для случая параллельного ввода информации запрещающий вход очевидно не нужен, так как полол ительных импульсов с выхода дифференцирующей цепи при правильной работе гакого регистра быть не должно.

Число разрядов регистра 1, которое можно контролировать с помощью одного декодирующего преобразователя W из условия надельного срабатывания схем «PI 7, составляет 15- 20 разрядов.

Выход декодирующего преобразователя Ю нагружен на каскад с больщим входным сопротивлением и малой входной емкостью (эмиттерный повторитель 2). Эмиттерный повторитель позволяет получать коэффициент передачи преобразователя 10 около единицы и

i 10 же время не снижает быстродействия схемы контроля.

Далее выходное напряжение эмиттерного ЮБТорителя дифференцируется цепью 3 и поступает на две схемы запрета 4 н 5. Положительные импульсы поступают на схе.му запрета 5, а отрицательные - на схему запрета 4.

С выхода схе.м запрета сигналы поступают на схему «ИЛИ 5, на выходе которой появляется сигнал ощибки.

Запрещающие потенциалы снимаются с двухвходОВЫХ схем «И 7 и S. На входы схем «И 7 подаются сигналы со входа регистра 1 и сигнал с выхода сумматора 6, а на входы схемы «И 8 подаются сигнал с выхода регистра и с выхода того же сумматора 6. Входами сумматора по модулю два являются вход и выход контролируемого регистра.

Задержка запрещающих сигналов 2 и Zg ia длительность дифференцированных импульсов происходит за счет естесгвенной задержки в схеме сумматора 6 и схемах «И 7 и 8.

Предмет изобретения

Устройство для обнаружения ошибок в регистре сдвига, выполненное на импульсно-потенциальных элементах, содержащее регистр сдвига, поразрядные выходы которого через декодирующий преобразователь подключены

к эмиттерному повторителю, отличающееся тем, что, с целью повышения эффективности контроля, оно содержит сумматор по .модулю два, логические схемы «И, «ИЛИ, дифференцирующую цепь, две схемы запрета, причем первые входы первой схемы «И и сумматора подключены к соответствующей входной щи.не регистра, второй вход су.мматора подключен к перво.му входу второй схемы «И и к соответствующей выходной шине регистра, а

иыход сумматора подключен ко вторым входам указанных схем «И, выходы которых подключены к запрещающим входам первой и второй схем запрета соответственно, причем вторые входы последних объединены и подключены к дифференцирующей цепи, а выходы схем запрета через схе.му «ИЛИ подключены к щине сигнала ощибки.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК В РЕГИСТРЕ СДВИГА | 1973 |

|

SU399862A1 |

| Устройство для контроля регистраСдВигА | 1979 |

|

SU813434A1 |

| МНОГОКАНАЛЬНАЯ АППАРАТУРА ПЕРЕДАЧИ ДВОИЧНЫХСИГНАЛОВ | 1971 |

|

SU313302A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Устройство для контроля регистров сдвига | 1980 |

|

SU924759A1 |

| БИБЛ'ИОТЩ^ | 1973 |

|

SU365708A1 |

| Устройство для отображения параметров импульса на экране осциллографа | 1984 |

|

SU1169011A1 |

| @СЕСОЮЗН*.Я | 1973 |

|

SU378919A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2003 |

|

RU2244311C1 |

Даты

1969-01-01—Публикация