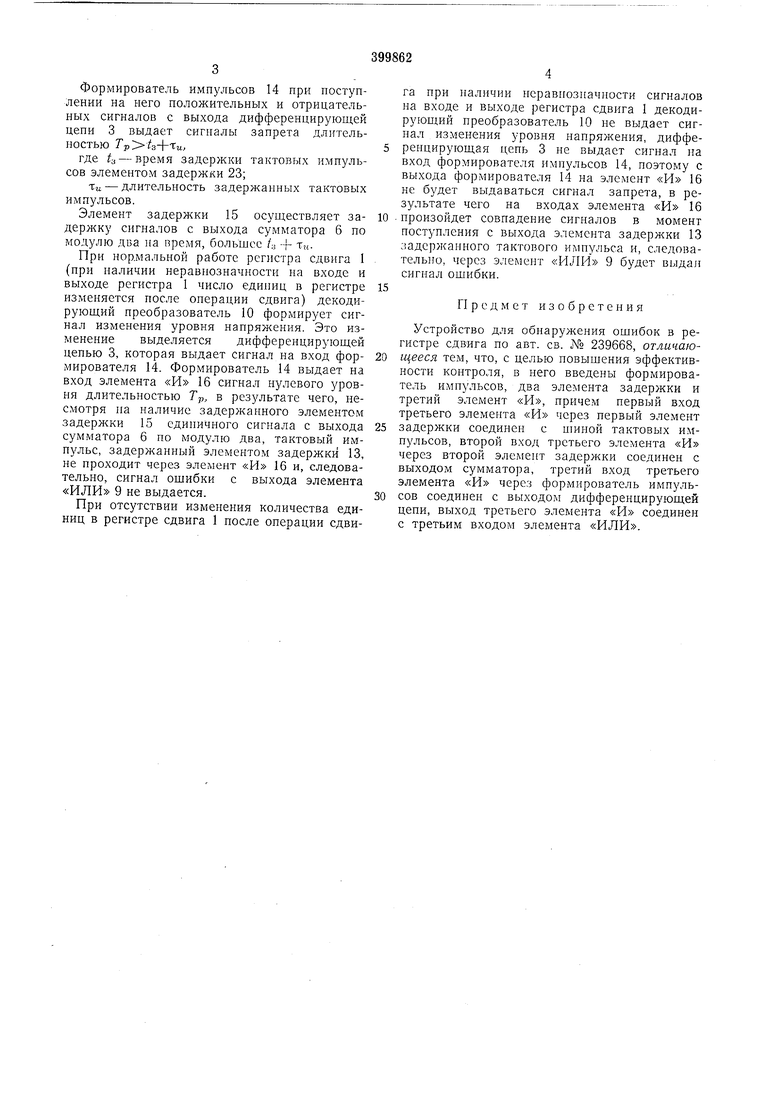

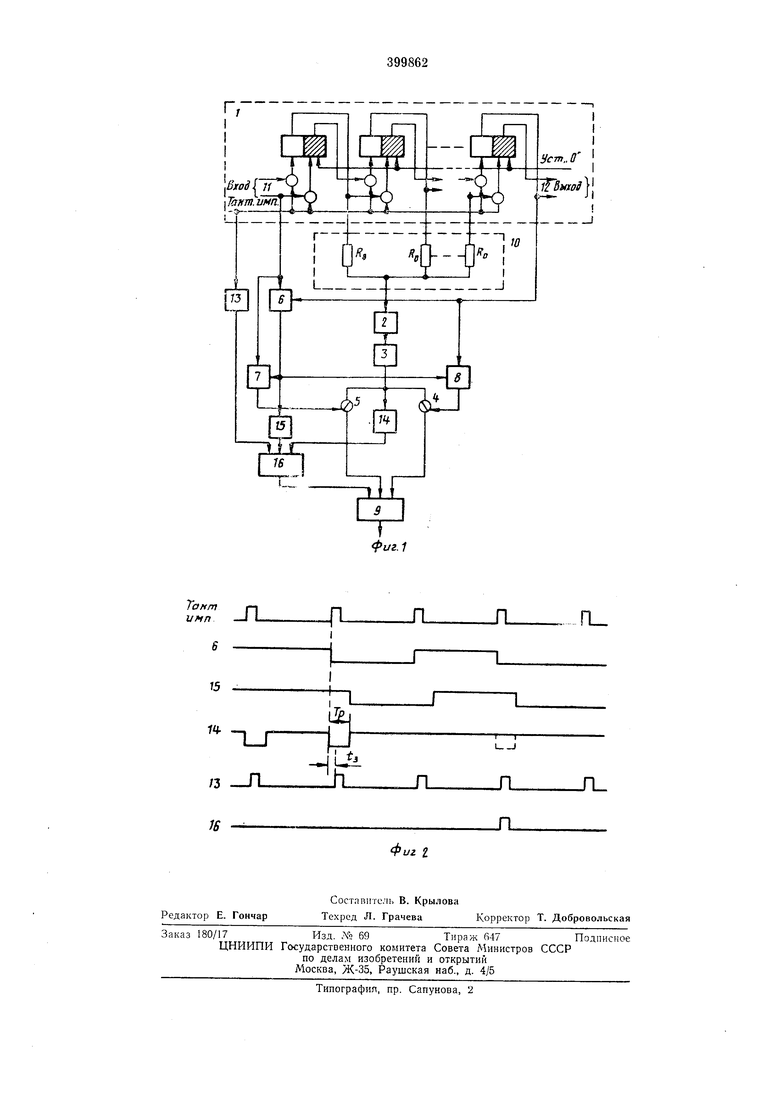

Изобретение относится к вычислительной технике, в частности к устройствам контроля функциональных электрических узлов. Известно устройство для обнаружения ошибок в регистре сдвига по авт. св. № 239668. Однако, применяя его невозможно обнаружить ошибки, заключающиеся в том, что число единиц в регистре (при наличии неравнозначности на входе и выходе регистра) остается неизменным после операции сдвига. Для повышения эффективности контроля предлагаемого устройства в него введены третий элемент «И, формирователь импульсов, два элемента задержки, один из которых служит для задержки тактовых импульсов, а другой--сигналов с выхода сумматора по модулю два, причем выход элемента «И подключен к дополнительному входу элемента «ИЛИ, один из входов третьего элемента «И через схему задержки подключен к выходу сумматора по модулю два, другой вход третьего элемента «И через формирователь импульсов подключен к выходу дифференцирующей цепи; а третий вход третьего элемента «И подключен к выходу элемента задержки, на вход которой поступают тактовые импульсы. На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2 - временная диаграмма. Устройство состоит из контролируемого регистра сдвига 1, эмиттерного повторителя 2, дифференцирующей цепи 3, схемы запрета 4, 5, сумматора 6 по модулю два, элементов «И 7 и 8, элемента «ИЛИ 9, декодирующего преобразователя 10, входных шин 11 регистра 1, выходных шин 12 регистра , элемента задержки 13, формирователя импульсов 14, элемента задержки 15 и элемента «И 16. Выход элемента «И 16 подключен к одному из в.ходов элемента «ИЛИ 9, входы элемента «И 16 соединешя со входами элемента задержки 13, формирователя импульсов 14 и элемента задержки 15, вход формирователя импульсов 14 подключен к выходу дифференцирующей цепи 3, вход элемента задержки 15 подключен к выходу сумматора 6 по модулю два, а на вход элемента задержки 13 подаются тактовые импульсы регистра сдвига 1. Элемент задержки 13 осуществляет заержку тактовых импульсов па время где t - суммарное время переключения элементов регистра сдвига 1, декодирующего преобразователя 10, эмиттерного повторителя 2 и дифференцирующей цепи 3.

Формирователь импульсов 14 при поступлении на него положительных и отрицательных сигналов с выхода дифференцирующей цепи 3 выдает сигналы запрета длительностью ,

где t-j - время задержки тактовых импульсов элементом задержки 23;

Тк - длительность задержанных тактовых импульсов.

Элемент задержки 15 осуществляет задержку сигналов с выхода сумматора 6 по модулю два на время, больщее /з + Ти.

При нор.мальной работе регистра сдвига 1 (при наличии неравнозначности на входе и выходе регистра 1 число единиц в регистре изменяется после операции сдвига) декодирующий преобразователь 10 формирует сигнал изменения уровня напрян ения. Это изменение выделяется дифференцирующей цепью 3, которая выдает сигнал на вход формирователя 14. Формирователь 14 выдает на вход элемента «И 16 сигнал нулевого уровня длительностью Тр, в результате чего, несмотря на наличие задержанного элементо.м задержки 15 единичного сигнала с выхода сум.матора 6 по модул о два, тактовый импульс, задержанный элементом задержки 13, не проходит через элемент «И 16 и, следовательно, сигнал ощибки с выхода элемента «ИЛИ 9 не выдается.

При отсутствии изменения количества единиц в регистре сдвига 1 после операции сдвига при наличии неравнозначности сигналов на входе и выходе регистра сдвига 1 декодирующий преобразователь 10 не выдает сигнал изменения уровня напряжения, дифференцирующая цепь 3 не выдает сигнал на вход формирователя импзльсов 14, поэтому с выхода формирователя 14 на элемент «И 16 не будет выдаваться сигнал запрета, в результате чего на входах элемента «И 16 произойдет совпадение сигналов в момент поступления с выхода элемента задержки 13 задержанного тактового импульса и, следовательно, через элемент «ИЛИ 9 будет выдан сигнал ошибки.

Предмет изобретения

Устройство для обнаружения ошибок в регистре сдвига но авт. св. AI 239668, отличающееся тем, что, с целью повышения эффективности контроля, в него введены формирователь импульсов, два элемента задержки и третий элемент «И, причем первый вход третьего элемента «И через первый элемент задержки соединен с шиной тактовых импульсов, второй вход третьего элемента «И через второй элемент задержки соединен с выходом сумматора, третий вход третьего элемента «И через формирователь импульсов соединен с выходом дифференцирующей цепи, выход третьего элемента «И соединен с третьим входом элемента «ИЛИ.

IE

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля регистров сдвига | 1980 |

|

SU924759A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК В РЕГИСТРЕСДВИГА | 1969 |

|

SU239668A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Пороговый декодер сверточного кода | 1989 |

|

SU1667264A1 |

| Устройство для исследования оперативной памяти | 1986 |

|

SU1404059A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

фиг.1

Авторы

Даты

1973-01-01—Публикация