Изобретение относится к автоматике и вычислительной технике, может быть использовано в устройствах циф-. ровой обработки сигналов, амплитудно- временного анализа и системах сжатия данных и является дополнительным к авт.св. № 1345349.

Цель изобретения - расширение функциональных возможностей за счет определения амплитудно-временных параметров двухполярного сигнала в моменты изменения знака его производной.

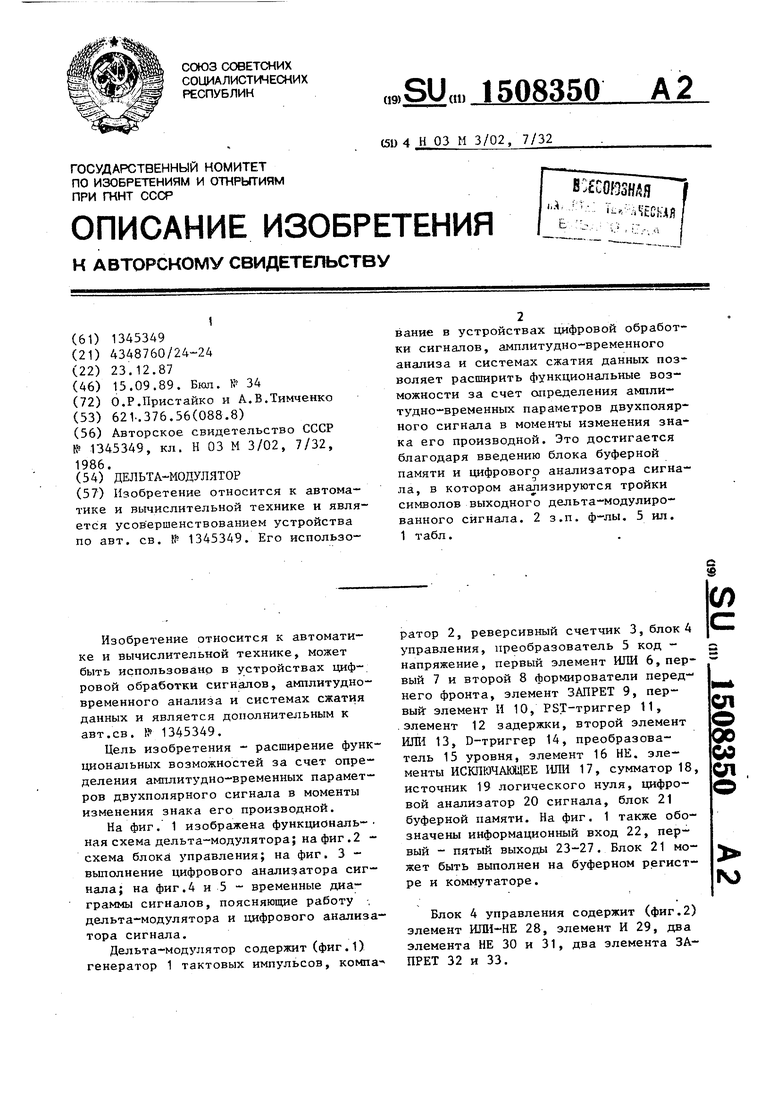

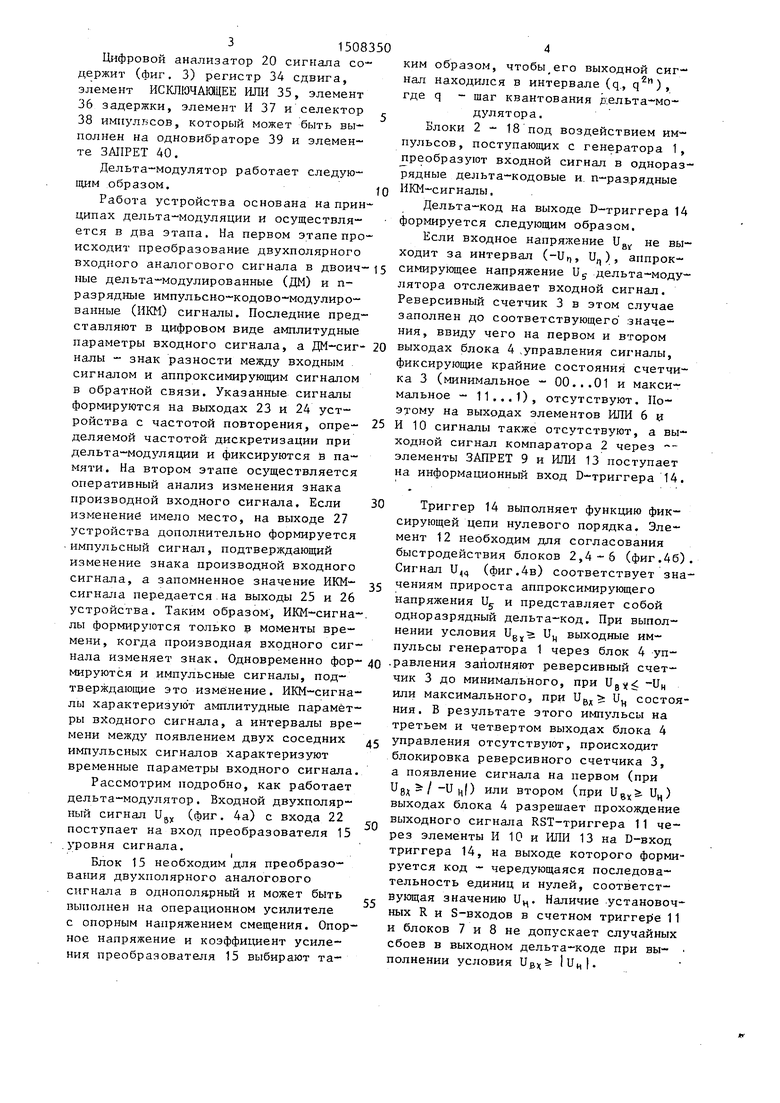

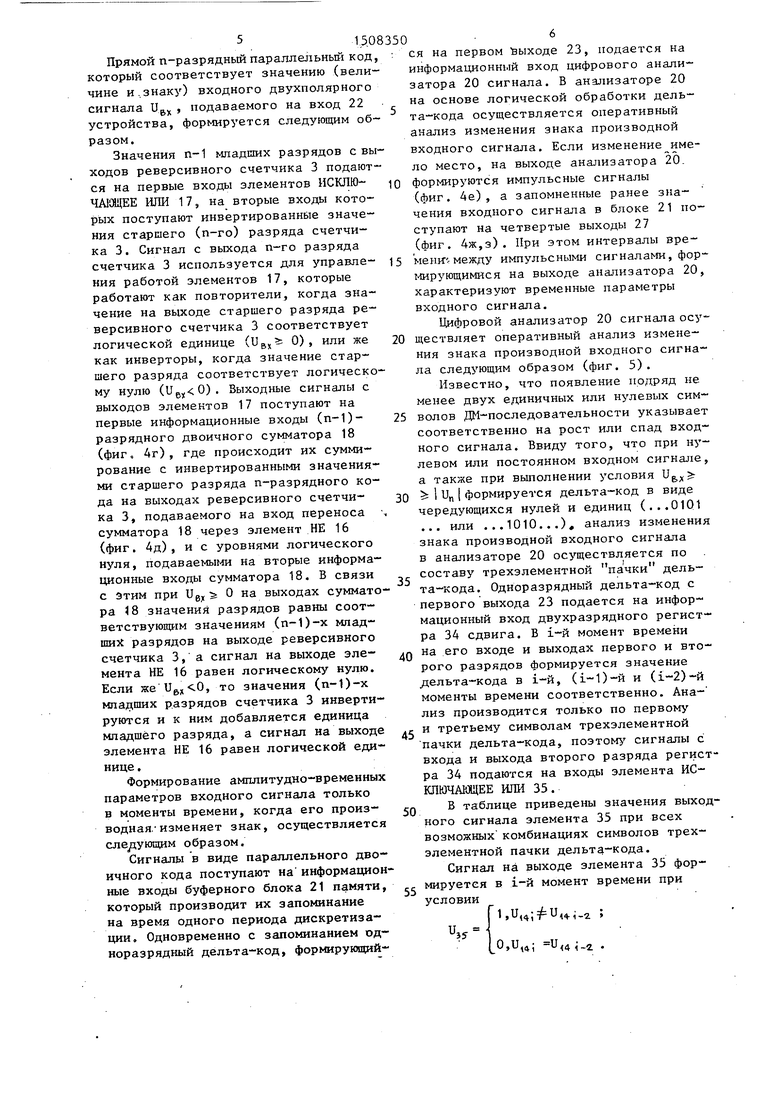

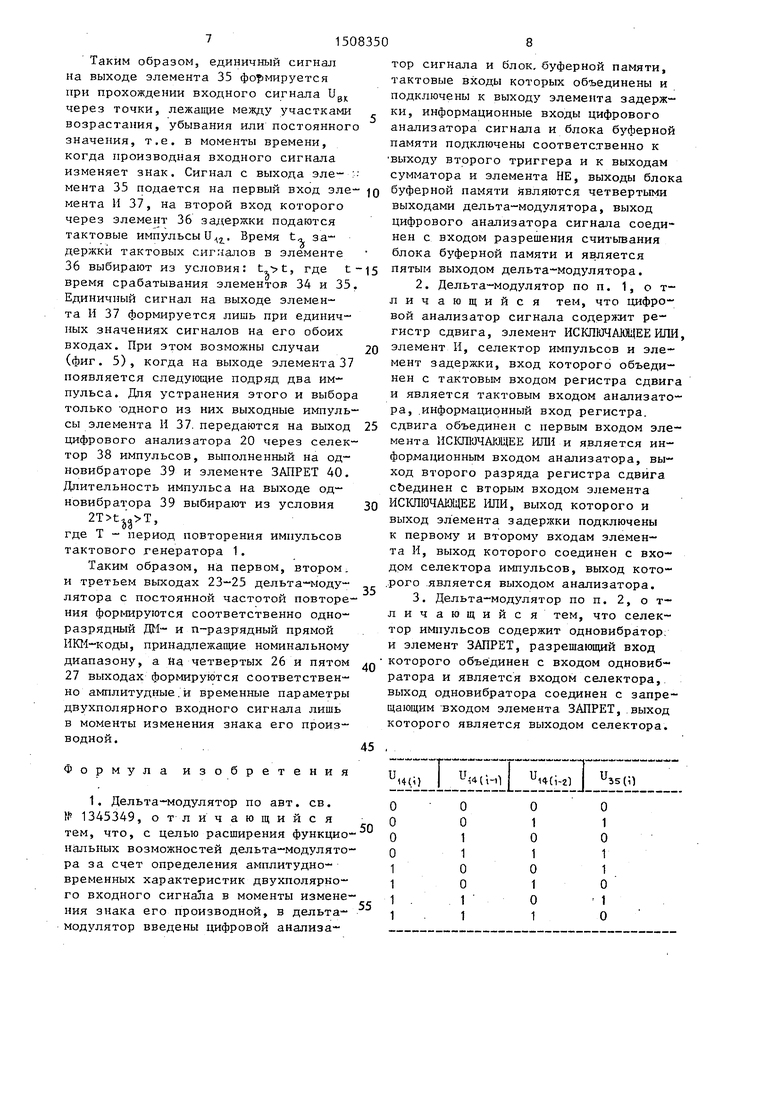

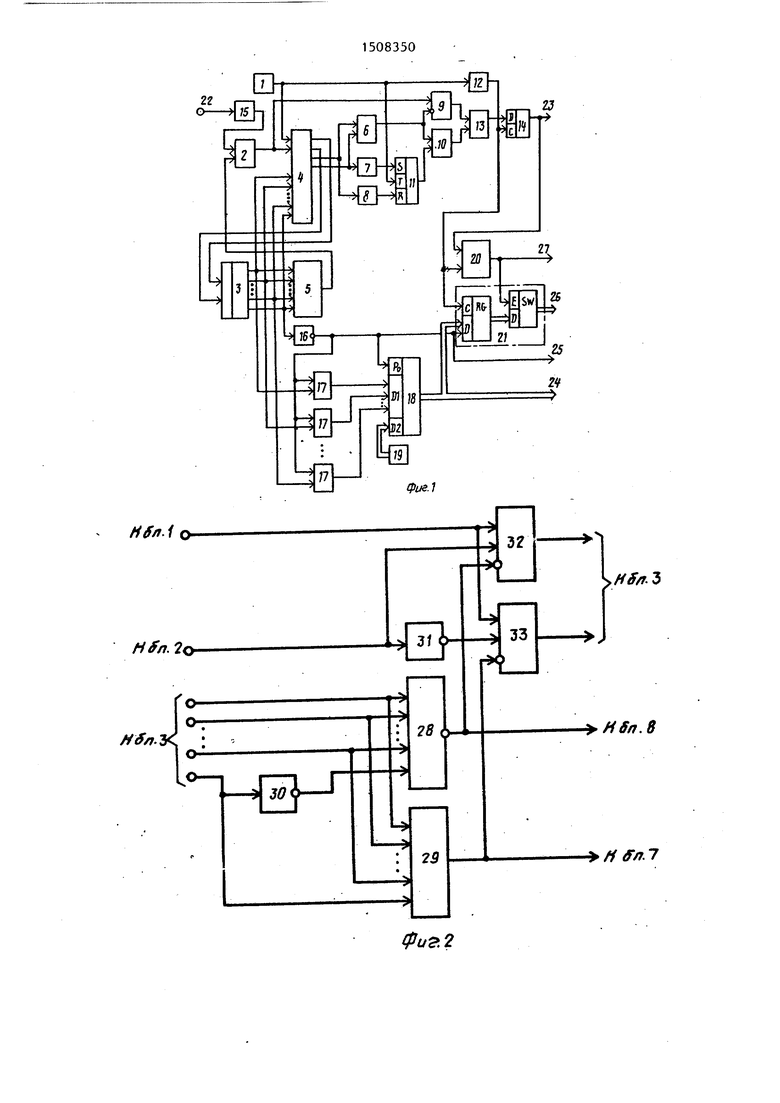

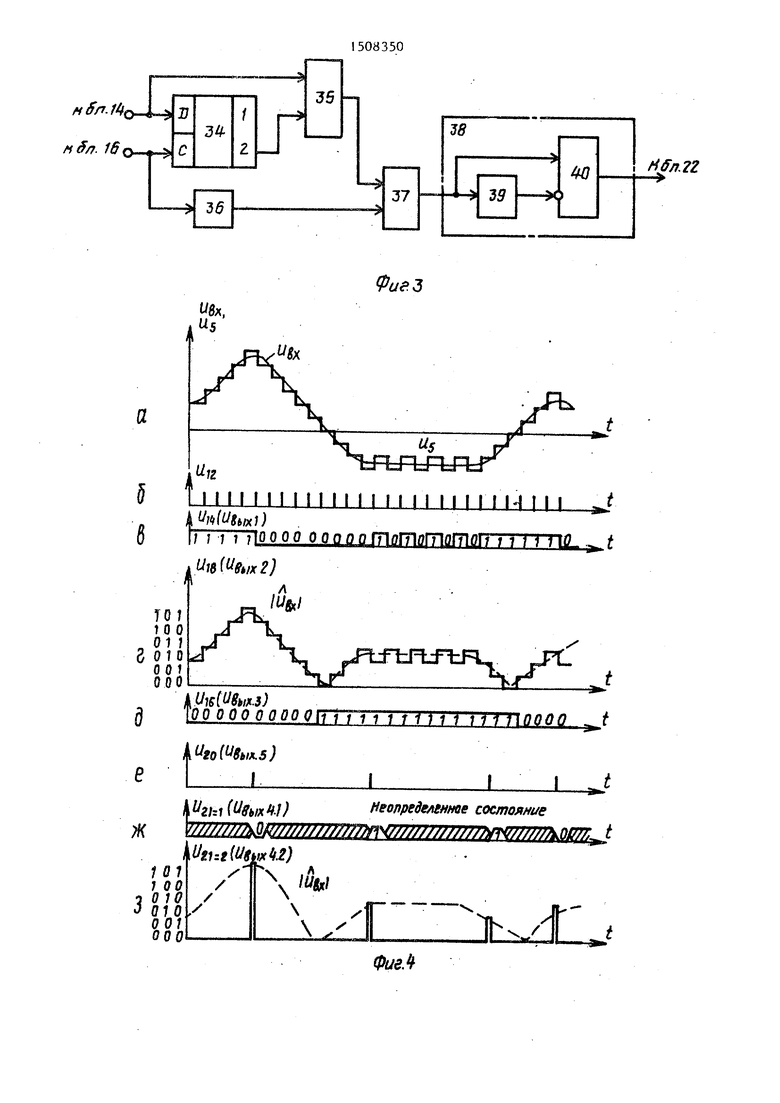

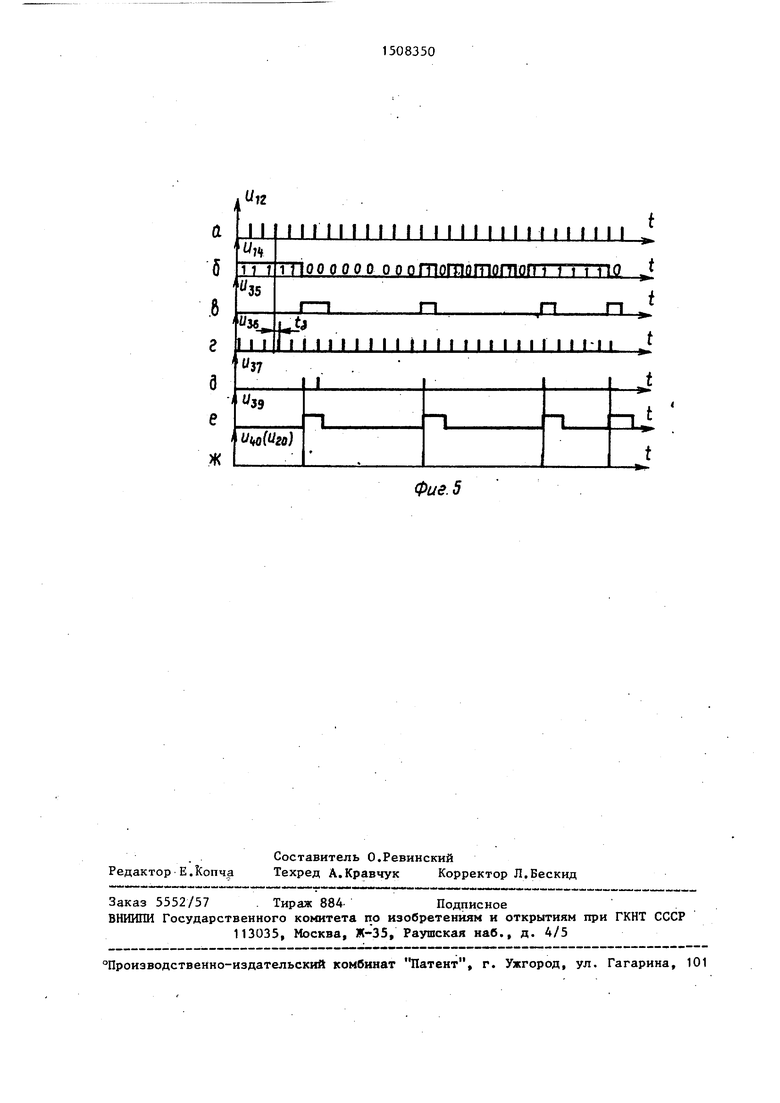

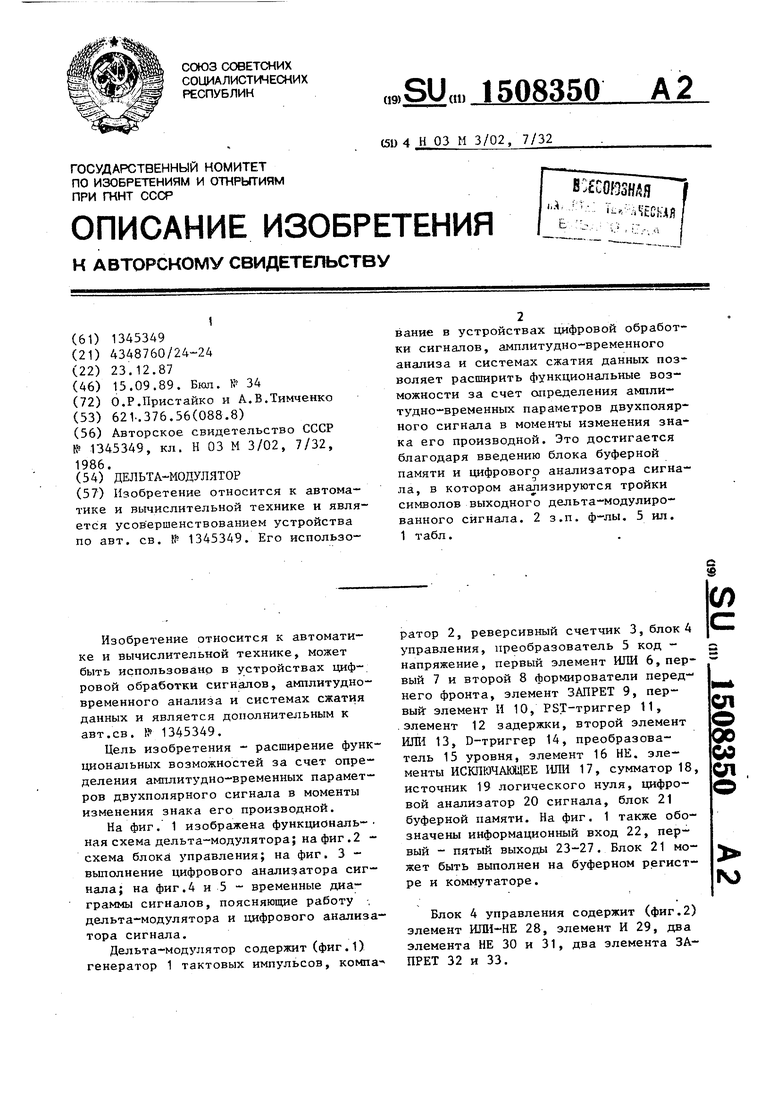

На фиг. 1 изображена функциональ- ная схема дельта-модулятора; на фиг .2 - схема блока управления; на фиг. 3 - выполнение цифрового анализатора сигнала; на фиг.4 и 5 - временные днаг граммы сигналов, поясняющие работу . дельта-модулятора и цифрового анализатора сигнала.

Дельта-модулятор содержит (фиг.1) генератор 1 тактовых импульсов, компа

ратор 2, реверсивный счетчик 3, блок 4 управления, преобразователь 5 код - напряжение, первый элемент ИЛИ 6, первый 7 и второй 8 формирователи перед-- него фронта, элемент ЗАПРЕТ 9, первый- элемент И 10, PST-триггер 11, .элемент 12 задержки, второй элемент ИЛИ 13, D-триггер 14, преобразователь 15 уровня, элемент 16 НЕ. элементы ИСКЛЮЧАЩЕЕ ИЛИ 17, сумматор 18, источник 19 логического нуля, цифровой анализатор 20 сигнала, блок 21 буферной памяти. На фиг. 1 также обозначены информационный вход 22, первый - пятый выходы 23-27. Блок 21 может быть выполнен на буферном регистре и коммутаторе.

Блок 4 управления содержит (фиг.2) элемент ИЛИ-НЕ 28, элемент И 29, два элемента НЕ 30 и 31, два элемента ЗАПРЕТ 32 и 33.

О1

о

00 Од

сд

14)

31508

Цифровой анализатор 20 сигнала содержит (фиг, 3) регистр 34 сдвига, элемент ИСКЛЮЧАКЩЕЕ ИЛИ 35, элемент 36 задержки, элемент И 37 и селектор 38 импулвсов, который может быть выполнен на одновибраторе 39 и элементе ЗАПРЕТ 40.

Дельта-модулятор работает следующим образом.

Работа устройства основана на принципах дельта-модуляции и осуществляется в два этапа. На первом этапе происходит преобразование двухполярного входного аналогового сигнала в двоич- ные дельта-модулированные (ДМ) и п- разрядные импульсно-кодово-модулиро- ванные (ИКМ) сигналы. Последние представляют в цифровом виде амплитудные параметры входного сигнала, а ДМ-сиг- налы - знак разности между входным сигналом и аппроксимирующим сигналом в обратной связи. Указанные сигналы формируются на выходах 23 и 24 устройства с частотой повторения, опре- деляемой частотой дискретизации при дельта-модуляции и фиксируются в памяти. На втором этапе осуществляется оперативный анализ изменения знака производной входного сигнала. Если изменение имело место, на выходе 27 устройства дополнительно формируется импульсный сигнал, подтверждающий изменение знака производной входного сигнала, а запомненное значение ИКМ- сигнала передается на выходы 25 и 26 устройства. Таким образом , ИКМ-сигналы формируются только в моменты времени, когда производная входного сигнала изменяет знак. Одновременно фор- мируются и импульсные сигналы, подтверждающие это изменение. ИКМ-сигналы характеризуют амплитудные параметры входного сигнала, а интервалы времени между появлением двух соседних импульсных сигналов характеризуют временные параметры входного сигнала

Рассмотрим подробно, как работает дельта-модулятор. Входной двухполяр- ный сигнал Ug,; (фиг. 4а) с входа 22 поступает на вход преобразователя 15 .уровня сигнала.

Блок 15 необходим для преобразования двухполярного аналогового сигнала в однополярный и может быть выполнен на операционном усилителе с опорным напряжением смещения. Опорное напряжение и коэффигщент усиления преобразователя 15 выбирают та

0 5 0 5 0

5

КИМ образом, чтобы его выходной сигнал находился в интервале (q., q), где q - шаг квантования дельта-модулятора.

Блоки 2 - 18 под воздействием импульсов, поступающих с генератора 1, реобразуют входной сигнал в одноразрядные дельта-кодовые и. п-раз.рядные ИКМ-сигналы.

Дельта-код на выходе D-триггера 14 формируется следующим образом.

Если входное напряжение U, не выходит за интервал (-U,,, U), аппроксимирующее напряжение U дельта-модулятора отслеживает входной сигнал. Реверсивный счетчик 3 в этом случае заполнен до соответствующего значения, ввиду чего на первом и втором выходах блока 4 .управления сигналы, фиксирующие крайние состояния счетчика 3 (минимальное - 00...01 и максимальное - 11...1), отсутствуют. Поэтому на выходах элементов ИЛИ 6 и И 10 сигналы также отсутствуют, а выходной сигнал компаратора 2 через элементы ЗАПРЕТ 9 и ИЛИ 13 поступает на информационный вход D-триггера 14.

Триггер 14 выполняет функцию фиксирующей цепи нулевого порядка. Элемент 12 необходим для согласования быстродействия блоков 2,4-5 (фиг.46). Сигнал (фиг.4в) соответствует значениям прироста аппроксимирующего напряжения Ug. и представляет собой одноразрядный дельта-код. При выполнении условия Ug Иц выходные импульсы генератора 1 через блок 4 уп- .равления заполняют реверсивный счетчик 3 до минимального, при Ug -UH или максимального, при Ug U состояния. В результате этого импульсы на третьем и четвертом выходах блока 4 управления отсутствз ют, происходит блокировка реверсивного счетчика 3, а появление сигнала на первом (при Ug S/-Un() или втором (при . Цц) выходах блока 4 разрешает прохождение выходного сигнала RST-триггера 11 через элементы И 10 и 1-ШИ 13 на D-вход триггера 14, на выходе которого формируется код - чередующаяся последовательность единиц и нулей, соответствующая значению U. Наличие установочных R и S-входов в счетном триггер е 11 и блоков 7 и 8 не допускает случайных сбоев в выходном дельта-коде при вы- полнении условия Ug lUnlПрямой n-разрядный параллельный код который соответствует значению (величине и,знаку) входного двухполярного сигнала Ug, , подаваемого на вход 22 устройства, формируется следующим образом.

Значения п-1 младиих разрядов с выходов реверсивного счетчика 3 подаются на первые входы элементов ИСКЛЮ- ЧАКЯДЕЕ ИЛИ 17, на вторые входы которых поступают инвертированные значения старшего (п-го) разряда счетчика 3. Сигнал с вьшода п-го разряда счетчика 3 используется для управления работой элементов 17, которые работают как повторители, когда значение на выходе старшего разряда реверсивного счетчика 3 соответствует логической единице ( 0), или же как инверторы, когда значение старшего разряда соответствует логическому нулю (Up,0). Выходные сигналы с выходов элементов 17 поступают на первые информационные входы (п-1)- разрядного двоичного сумматора 18 (фиг, Аг), где происходит их суммирование с инвертированными значениями старшего разряда п-разрядного кода на выходах реверсивного счетчика 3, подаваемого на вход переноса сумматора 18 через элемент НЕ 16 (фиг. 4д), и с уровнями логического нуля, подаваемьи-т на вторые информационные входы сумматора 18. В связи с Этим при Uej( О на выходах сумматора 8 значения разрядов равны соответствующим значениям (п-1)-х младших разрядов на выходе реверсивного счетчика 3, а сигнал на выходе элемента НЕ 16 равен логическому нулю. Если же и.0, то значения (п-1)-х мпадших разрядов счетчика 3 инвертируются и к ним добавляется единица младшего разряда, а сигнал на выходе элемента НЕ 16 равен логической единице ,

Формирование амплитудно-временных параметров входного сигнала только в моменты времени, когда его производная. изменяет знак, осуществляется образом.

Сигналы в виде параллельного двоичного кода поступают на информационные входы буферного блока 21 памяти, который производит их запоминание на время одного периода дискретизации. Одновременно с запоминанием одноразрядный дельта-код, формируняций8350

,

10

15

20

25

30

35

40

45

50

55

ся на первом выходе 23, подается на информационный вход цифрового анализатора 20 сигнала. В анализаторе 20 на основе логической обработки дельта-кода осуществляется оперативный анализ изменения знака производной входного сигнала. Если изменение имело место, на выходе анализатора 20. формируются импульсные сигналы (фиг. 4е), а запомненные ранее значения входного сигнала в блоке 21 поступают на четвертые выходы 27 (фиг. 4ж,з). При этом интервалы вре- ментмежду импульсными сигналами, фор- 1.1ИРУЮЩИМИСЯ на выходе анализатора 20, характеризуют временные параметры входного сигнала.

Цифровой анализатор 20 сигнала осуществляет оперативный анализ изменения знака производной входного сигнала следующим образом (фиг. 5).

Известно, что появление подряд не менее двух единичных или нулевых символов ДМ-последовательности указывает соответственно на рост или спад входного сигнала. Ввиду того, что при нулевом или постоянном входном сигнале, а также при выполнении условия Ug, 1 формируется дельта-код в виде чередующихся нулей и единиц (...0101 ... или ...1010...), анализ изменения знака производной входного сигнала в анализаторе 20 осуществляется по составу трехэлементной па чки дельта-кода. Одноразрядный дельта-код с первого выхода 23 подается на информационный вход двухразрядного регистра 34 сдвига. В i-й момент времени на его входе и выходах первого и второго разрядов формируется значение дельта-кода в i-й, (1-1)-и и (1-2)-й моменты времени соответственно. Ана- ЛИЗ производится только по первому и третьему символам трехэлементной пачки дельта-кода, поэтом сигналы с входа и выхода второго разряда регистра 34 подаются на входы элемента ИС- КЛЮЧАРЛДЕЕ ИЛИ 35.

В таблице приведены значения выход ного сигнала элемента 35 при всех возможных комбинациях символов трехэлементной пачки дельта-кода.

Сигнал на выходе элемента 35 формируется в i-й момент времени при условии

l.

35

О,и,,; и

4 1-i

71508

Таким образом, единичный сигнал на выходе элемента 35 фо)мируется при прохождении входного сигнала Ug через точки, лежащие между участками возрастания, убывания или постоянного значения, т.е. в моменты времени, когда производная входного сигнала изменяет знак. Сигнал с выхода эле- ; мента 35 подается на первый вход эле- мента И 37, на второй вход которого через элемент 36 задержки подаются тактовые импульсы ,. Время t задержки тактовых сигналов в элементе 36 выбирают из условия: t,t, где tвремя срабатывания элементов 34 и 35. Единичный сигнал на выходе элемента И 37 формируется лишь при единичных значениях сигналов на его обоих входах. При этом возможны случаи (фиг. 5), когда на выходе элемента 37 появляется следующие подряд два импульса. Для устранения этого и выбора только ОДНОГО из них выходные импульсы элемента И 37. передаются на выход цифрового анализатора 20 через селектор 38 импульсов, выполненный на од- новибраторе 39 и элементе ЗАПРЕТ 40. Длительность импульса на выходе од- новибратора 39 выбирают из условия

,

где Т - период повторения импульсов тактового генератора 1.

Таким образом, на первом, втором, и третьем выходах 23-25 дельта-модулятора с постоянной частотой повторения формируются соответственно одноразрядный и п-разрядный прямой Нга -коды, принадлежащие номинальному диапазону, а На четвертых 26 и пятом 27 выходах формируются соответственно a mлитyдныe . и временные параметры двухполярного входного сигнала лишь в моменты изменения знака его производной.

s 0 5 0

Q

5

8

тор сигнала и блок, буферной памяти, тактовые входы которых объединены и подключены к выходу элемента задержки, информационные входы цифрового анализатора сигнала и блока буферной памяти подключены соответственно к выходу второго триггера и к выходам сумматора и элемента НЕ, выходы блока буферной памяти являются четвертыми выходами дельта-модулятора, выход цифрового анализатора сигнала соединен с входом разрешения считьгоания блока буферной памяти и является пятым выходом дельта-модулятора.

2.Дельта-модулятор по п. 1, отличающийся тем, что цифровой анализатор сигнала содеряит регистр сдвига, элемент ИСКЛЮЧАЩЕЕ ИЛИ, элемент И, селектор импульсов и элемент задержки, вход которого объединен с тактовым входом регистра сдвига и является тактовым входом анализатора, .информационный вход регистра. сдвига объединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и является информационным входом анализатора, выход второго разряда регистра сдвига сЬединен с вторым входом элемента ИСКПЮЧАВДЕЕ ИЛИ, выход которого и выход элемента задержки подключены

к первому и второму входам элемента И, выход которого соединен с входом селектора импульсов, выход кото- .рого является выходом анализатора.

3.Дельта-модулятор по п. 2, о т- личающийся тем, что селектор импульсов содержит одновибратор; и элемент ЗАПРЕТ, разрешающий вход которого объединен с входом одновиб- ратора и является входом селектора, выход одновибратора соединен с запрещающим входом элемента ЗАПРЕТ, выход которого является выходом селектора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Дельта-модулятор | 1987 |

|

SU1448411A1 |

| Дельта-модулятор | 1987 |

|

SU1425838A1 |

| Дельта-модулятор | 1988 |

|

SU1543547A1 |

| Дельта-модулятор | 1990 |

|

SU1718383A1 |

| Преобразователь дельта-модулированного сигнала в импульсно-кодово-модулированный сигнал | 1986 |

|

SU1347190A1 |

| Адаптивный импульсно-кодовый модулятор | 1985 |

|

SU1300638A1 |

| Преобразователь сигналов с импульсно-кодовой модуляцией в сигналы с адаптивной дельта-модуляцией со слоговым компандированием | 1990 |

|

SU1709537A1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| Дельта-модулятор | 1985 |

|

SU1257849A1 |

Изобретение относится к автоматике и вычислительной технике и является усовершенствованием устройства по авт.св. N 1345349. Его использование в устройствах цифровой обработки сигналов, амплитудно-временного анализа и системах сжатия данных позволяет расширить функциональные возможности за счет определения амплитудно-временных параметров двухполярного сигнала в моменты изменения знака его производной. Это достигается благодаря введению блока буферной памяти и цифрового анализатора сигнала, в котором анализируются тройки символов выходного дельта-модулированного сигнала. 2 з.п. ф-лы, 5 ил.

Формула изобретения

(

L iiiJ

и

Ъ5()

Фи.2

Фиг. 5

| Дельта-модулятор | 1986 |

|

SU1345349A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-09-15—Публикация

1987-12-23—Подача