(5) УСТРОЙСТВО для КОНТРОЛЯ РЕГИСТРОВ

I

Изобретение относится к запомййающим устройствам.

Известно устройство, содержащее , декодирующий преобразователь, подключенный к эмиттерному повторителю,. сумматор по модулю два, логические схемы И и ИЛИ, дифференцирующую цепь, :две схемы запрета D .

Недостатком этого устройства является ограниченность области его применения.:

Наиболее близким к предлагаемому является устройство для контроля регистров сдвига, содержащее первый сумматор, входы которого соединены со входами устройства контроля, а выход - с первым входом элемента сравнения, второй вход которого соединен с выходом второго сумматора, выход элемента сравнения соединен с первым входом элемента И, второй вход которогочерез первый элемент задержки соединен с выходом СДВИГА

второго элемента задержки, вход которого подключен к тактовой шине и входу формирователя импульсов, выход которого соединен с тактовым . входом триггера, выход которого соединен с первым входом второго сумматора, второй вход которого соединен с информационным входом устройства, третий сумматор, выход которого соединен с информационным

to входом триггера, первый вход - с выходом первого сумматора, второй ... вход - с одним из входов первого) матора 2 .

16

Недостатком этого устройства является ограниченность области его примененияJ поскольку оно не позволяет контролировать правильность записи информации в регистр сдвига

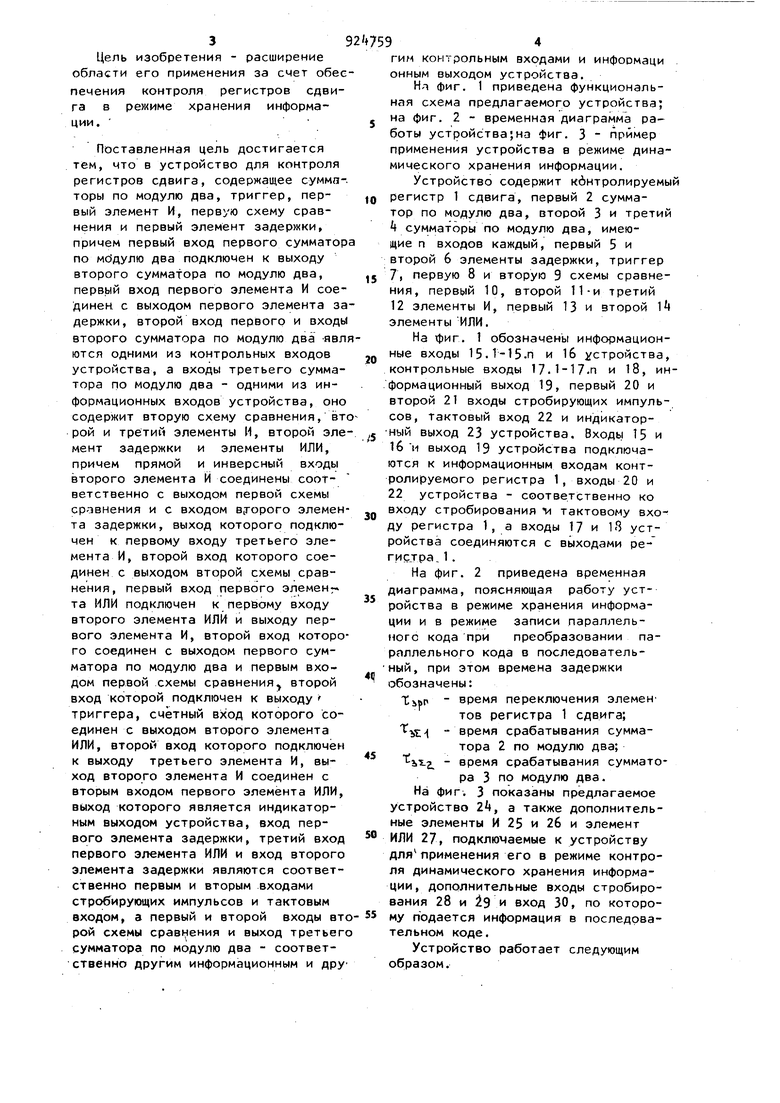

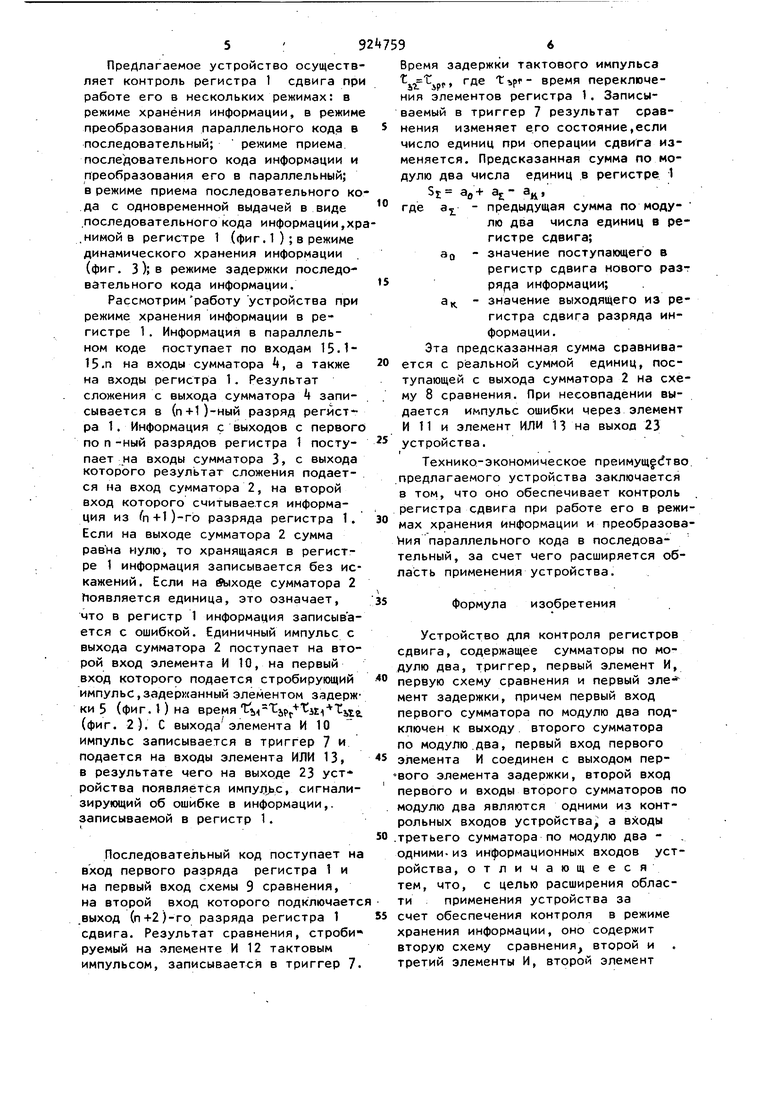

30 при работе его в режиму преобразования параллельного кода в последовательный и в режиме хранения информации. Цель изобретения - расширение области его применения за счет обес печения контроля регистров сдвига в режиме хранения информации. Поставленная цель достигается тем, что в устройство для контроля регистров сдвига, содержащее суммпторы по модулю два, триггер, первый элемент И, первую схему сравнения и первый элемент задержки, причем первый вход первого сумматор по мбдулю два подключен к выходу второго сумматора по модулю два, перв.ый вход первого элемента И соеЙинек с выходом первого элемента за держки, второй вход первого и входы второго сумматора по модулю два -явл ются одними из контрольных входов устройства, а входы третьего сумматора по модулю два - одними из информационных входов устройства, оно содержит вторую схему сравнения, вт рой и третий элементы И, второй эле мент задержки и элементы ИЛИ, причем прямой и инверсный входы второго элемента И соединены соответственно с выходом первой схемы сравнения и с входом второго элемен та задержки, выход которого подключен к первому входу третьего элемента И, второй вход которого соединен с выходом второй схемы сравнения, первый вход первого элемен;-. та ИЛИ подключен к первому входу второго элемента ИЛИ и выходу первого элемента И, второй вход которо го соединен с выходом первого сумматора по модулю два и первым входом первой схемы сравнения. второй вход которой подключен к выходу триггера, счётный вход которого соединен с выходом второго элемента ИЛИ, второй вход которого подключен к выходу третьего элемента И, выход второго элемента И соединен с вторым входом первого элемента ИЛИ, выход которого является индикаторным выходом устройства, вход первого элемента задержки, третий вход первого элемента ИЛИ и вход второго элемента задержки являются соответственно первым и вторым входами стробирующих импульсов и тактовым входом, а первый и второй входы вт рой схемы сравнения и выход третьег сумматора по модулю два - соответственно другим информационным и дру гим контрольным входами и информаци онным выходом устройства. Нл фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - временная диаграмма работы устройства;на фиг. 3 пример применения устройства в режиме динамического хранения информации. Устройство содержит контролируемый регистр 1 сдвига, первый 2 сумматор по модулю два, второй 3 и третий сумматоры по модулю два, имеющие п входов каждый, первый 5 и второй 6 элементы задержки, триггер 7| первую 8 и вторую 9 схемы сравнения, первый 10, второй 11-и третий 12 элементы И, первый 13 и второй И элементы ИЛИ. На фиг. 1 обозначены информационные входы 15.1-15.п и 16 i/стройства, контрольные входы 17.1-17.п и 18, информационный выход 19, первый 20 и второй 21 входы стробирующих импульсов. Тактовый вход 22 и индикаторный выход 23 устройства. Входь 15 и 16 и выход 19 устройства подключаются к информационным входам контролируемого регистра 1, входы 20 и 22 устройства - соответственно ко входу стробирования и тактовому входу регистра 1, а входы 17 и 18 устройства соединяются с выходами регистра, 1 . На фиг. 2 приведена временная диаграмма, поясняющая работу устройства в режиме хранения информации и в режиме записи параллельного кода при преобразовании параллельного кода в последовательный, при этом времена задержки обозначены: tj,,,p - время переключения элемен тов регистра 1 сдвига; ът;- - время срабатывания сумматора 2 по модулю два; 2,2. время срабатывания сумматора 3 по модулю два. На фиг. 3 показаны предлагаемое устройство 2k, а также дополнительные элементы И 25 и 2б и элемент ИЛИ 27, подключаемые к устройству для применения его в режиме контроля динамического хранения информации, дополнительные входы стробирования 28 и и вход 30, по которому подается информация в последовательном коде. Устройство работает следующим образом. Предлагаемое устройство осуществ ляет контроль регистра 1 сдвига пр работе его в нескольких режимах: в режиме хранения информации, в режим преобразования параллельного кода в последовательный; режиме приема, последовательного кода информации и преобразования его в параллельный; в режиме приема последовательного ко да с одновременной выдачей в виде .последовательного кода информации,хр .нимой в регистре 1 (фиг.1 ) ; в режиме динамического хранения информации (фиг. 3); в режиме задержки последовательного кода информации. Рассмотрим работу устройства при режиме хранения информации в регистре 1. Информация в параллельном коде поступает по входам 15.115 .п на входы сумматора , а также на входы регистра 1. Результат сложения с выхода сумматора 4 записывается в (п+1)-ный разряд регистра 1. Информация с выходов с первог по п-ный разрядов регистра 1 поступает на входы сумматора 3, с выхода которого результат сложения подается на вход сумматора 2, на второй вход которого считывается информация из п+1)-гЬ разряда регистра 1. Если на выходе сумматора 2 сумма равна нулю, то хранящаяся в регистре 1 информация записывается без искажений . Если на А 1ходе сумматора 2 1оявляется единица, это означает, что в регистр 1 информация записывается с ошибкой. Единичный импульс с выхода сумматора 2 поступает на второй вход элемента И 10, на первый вход которого подается стробирущий импульс,задержанный элементом задерж ки 5 (фиг. 1) на время l4(,te (фиг. 2). С выходаэлемента И 10 импульс записывается в триггер 7 и подается на входы элемента ИЛИ 13, в результате чего на выходе 23 уст ройства появляется импул с, сигнализирующий об ошибке в информации,, записываемой в регистр 1. Последовательный код поступает на вход первого разряда регистра 1 и на первый вход схемы 9 сравнения, на второй вход которого подключаетс выход (п+2)-го разряда регистра 1 сдвига. Результат сравнения, строби руемый на элементе И 12 тактовым импульсом, записывается в триггер 7. Время задержки тактового импульса а.гЧр время переключения элементов регистра 1. Записываемый в триггер 7 результат сравнения изменяет его состояние,если число единиц при операции сдвига изменяется. Предсказанная сумма по модулю два числа единиц в регистре 1 Sj ао + предыдущая сумма по модулю два числа единиц в регистре сдвига; значение поступающего в регистр сдвига нового разт информации; а - значение выходящего из регистра сдвига разряда информации . Эта предсказанная сумма сравнивается с реальной суммой единиц, поступающей с выхода сумматора 2 на схему 8 сравнения. При несовпадении выдается импульс ошибки через элемент И 11 и элемент ИЛИ 13 на выход 23 устройства. Технико-экономическое пpeимyщfdтвo, предлагаемого устройства заключается в том, что оно обеспечивает контроль регистра сдвига при работе его в режимах хранения информации и преобразования параллельного кода в последовательный, за счет чего расширяется область применения устройства. Формула изобретения Устройство для контроля регистров сдвига, содержащее сумматоры по модулю два, триггер, первый элемент И, первую схему сравнения и первый эле- мент задержки, причем первый вход первого сумматора по модулю два подключен к выходу второго сумматора по модулю.два, первый вход первого элемента И соединен с выходом первого элемента задержки, второй вход первого и входы второго сумматоров по модулю два являются одними из контрольных входов устройства а входы третьего сумматора по модулю два одними-из информационных входов устройства, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения контроля в режиме хранения информации, оно содержит вторую схему сравнения, второй и третий элементы И, второй элемент задержки и элементы ИЛИ, причем прямой и инверсный входы второго эл мента И соединены соответственно с выходом первой схемы сравнения и с входом второго элемента задержки, выход которого подключен к первому входу третьего элемента И, второй вход которого соединен с выходом второй схемы сравнения, первый вход первого элемента ИЛИ подключен к первому входу второго элемента ИЛИ и выходу первого элемента И, второй вход которого соединен с выходом первого сумматора по модулю два и первым входом первой схемы сравнения, второй вход которо подключен к выходу триггера, счетный вход которого соединен с выходо второго элемента ИЛИ, второй вход которого подключен к выходу третьего элё мента И, выход второго элемента И Соединен с вторым входом первого элемента ИЛИ, выход KcjTopor 38 является индикаторным выходом уст-, ройства, вход первого элемента задержки, третий вход первого элемента ИЛИ и вход второго элемента задержки являются соответственно .первым и вторым входами стробирующих импульсов и тактовым входом , а первый и второй входы второй схемы сравнения и выход третьего сумматора по модулю два - соответственно другим информационным у другим контрольным входами и информационным вь xoдoм устройства. Источники информации, принятые во внимание при экспертизе 1.Обнаружение и исправление ошибок в дискретных устройствах. Под ред. Толстякова В. С. М.,- Советское радио,1972, с. . 2.Авторскоесвидетельство СССР Vf 7«3038, кл. G11 С 29/00, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля регистров сдвига | 1977 |

|

SU743038A1 |

| Устройство для контроля информации по модулю три | 1988 |

|

SU1580369A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Генератор М-последовательностей | 1988 |

|

SU1596440A2 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля цифровых узлов | 1989 |

|

SU1645958A2 |

| ОБНАРУЖИТЕЛЬ ПАУЗ РЕЧИ В СИСТЕМЕ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1992 |

|

RU2103826C1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

.2

Авторы

Даты

1982-04-30—Публикация

1980-10-08—Подача