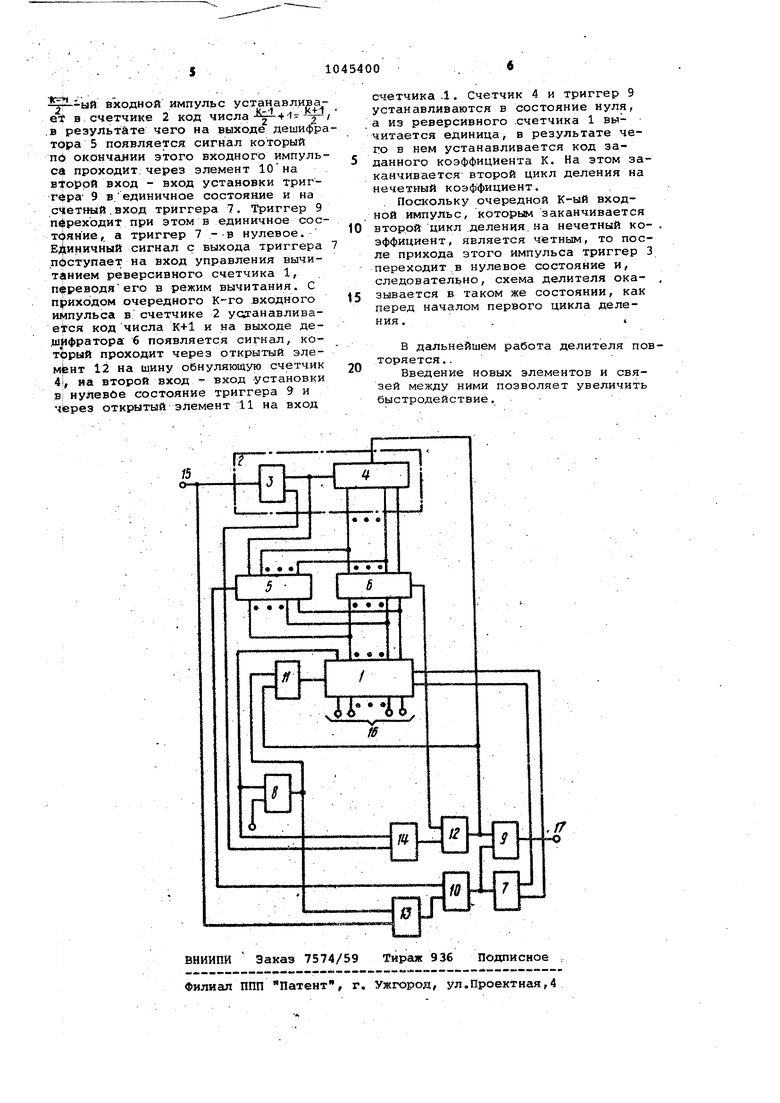

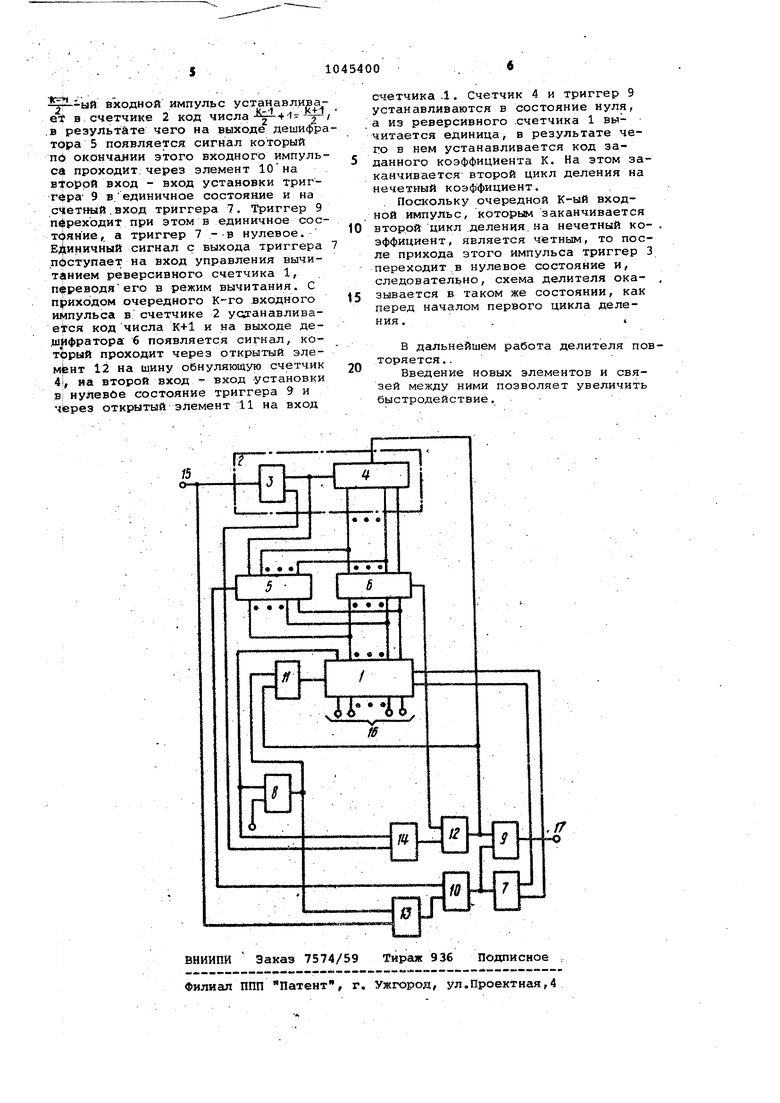

Изобретение относится к импульс ной технике и преднаэначено для использования в цифровой измерительной аппаратуре, в синтезаторах частот, в устройствах автоматики и телемеханики. Известен делитель частоты следования импульсов,, содержащий счет чик импульсов, дешифратор кода управления и дешифратор скважности, блок управления, элемент И-НЕ, три гер и инвертор L1 Недостаток известного устройства - ограниченное быстродействие. Наиболее близким по технической сущности к предлагаемому является Делитель частоты следования импуль сов, содержащий счетчик импульсов, счетный вход которого соединен с входной шиной, а разрядные выходы с первыми группами входов дешифратора кода, управления и дешифратора скважности, элемент И-НЕ, первый вход КОТОРОГО соединен с входной шиной, а выход, через элемент И со счетным входом триггера, блок управления и элемент запрета С23. j Недостаток устрбйства - ограниченное быстродействие. Цель изобретения -г повышение быстродействия. Поставленная цель достигается тем, что в делитель частоты следования импульсов, содержащий счетчик импульсов, счетный вход которо го соединен с входной шинЬй, выход всех разрядов кроме младшего - с первой группой входов дешифратора кода управления, а выходы всех раз рядов, кроме старшего - с первой группой входов дешифратора скважности, первый элемент Й-НЕ, первый вход которого соединен с входной ш .ной, а выход через первый элемент со счетным входом первого триггера введены реверсивный счетчик импуль сов, второй элемент И, второй триг гер и последовательно соединенные второй элемент И-НЕ, третий элемен И- и третий триггер, второй вход ко рого соединен со счетным входом первого триггера, первый и второй I выходы которого соединены с входами управления соответственно вычит нием и сложением реверсивного счет чика импульсов, прямой выход младшего разряда которого соединен с вход второго триггера и первым входом второго элемента. И-НЕ, выходы остальных разрядов - с вторыми группа1ми входов дешифр1атора скважности и де шифратора кода управления, разрядные входы - с шинами кода управления, а счетный вход - с выходом второго элемента И, первый вход ко торого соединен с выходом второго .триггера и вторым входом первого элемента И-НЕ, а второй вход - с обнуляющим входом счетчика импульсов и выходом третьего элемента И, второй вход которого и второй вход первого элемента И соеДИнены с выходами соответственно дешифратора кода управления и дешифратора скважности, при этом второй вход второго элемента И-НЕ соединен с инверсным выходом младшего разряда считчика импульсов. На чертеже представлена струк турная схема устройства. Схема содержит реверсивный счетчик 1 импульсов ,. счетчик 2 импульсов , состоящий из триггера 3, рабо- тающего в режиме непрерывного счета, и счет.чика 4, дешифратор 5 скважности, дешифратор б кода управления, триггеры 7-9, элементы И 10-12, элементы И-НЕ 13-14, входную шину 15, шину 16 кода управления, выходную шину 17. Максимальное значение коэффициента деления делителя определяется емкостью счет.чика 2; В реверсивном счетчике 1 импульсов, используемом в качестве узла управления, записывается и хранится код коэффициента деления К. Емкость этого счетчика должна превышать емкость счетчика 2 на один разряд. На, выходах дешифраторов 5 и 6 формируются сигналы в моменты совпадения кодов, поступающих на первые и вторые группы входов этих дешифраторов. С разрядных выходов счетчика 1 на вторые группы входов дешифраторов 5 и 6 поступает код коэффициента деления К, сдвинутый на один разряд в сторону младших разрядов, т.е. код числа у при четных-К или числа -- при нечетных К. К первой, группе входов дешифратора 5 подключены все разрядные выходы счетчика 2 за исключением вы-, хода старшего разряда. Поэтому на выходе дешифратора 5 сигнал будет появляться после установления на выходу счетчика.2 кода числа- или чиспа- , К первой группе входов дешифратора. 6 подключены все разрядные выходы счетчика 4. Поскольку на вход этого счетчика поступают, импульсы .с частотой в два раза меньшей, чем частота входных импульсов, то на выходе дешифратора б сигнал будет появляться при установлении на выходах счетчика 2 кода числа К или числа К-1. Триггер 8 предназначен для запоминания значения младшего разряда кода управления, записанного в счетчик 1. Логические элементы 11, 13 и 14 обеспечивают управление работой делителя при делении на нечетный коэффициент. Перед началом работы делителя триггеры 3, 7 - 9 и счетчики 1 и 4 устанавливаются в нулевое состояние. Затем по шинам 16 в счетчик 1 записывается код коэффициента деления, после чего делитель готов к работе., Устройство работает следующим образом. При делении на четный коэффицие в младшем разряде счетчика 1 записан нуль и поэтому триггер 8 находится в исходном состоянии. Сигнал нулевого уровня с выхода младшего разряда счетчика 1 и с выхода триг гера 8 поступают на соответствующи входа элементов 14 и 13, в результ те чего на выходах этих элементов постоянно присутствуют сигналы еди ничного уровня, которыми открыты элементы 12 и 10. Сигнал нулевого уровня с выхода триггера 8 поступае также на один вход элемента 11, удерживая его в закрытом состоянии Поэтому при делении на четный- коэф циент состояние счетчика 1 не изменится и делитель работает следую щим образом. С приходом го вход ного импульса на выходе.дешифратор 5 появляется сигнал, который проходит через открытый элемент 10 и переводит триггер 9 в единичное состояние. С приходом К-го входного импульса на выходе дешифратора б появляется сигнал,которыйчерез открытый элемент 12 поступает на вход триггера 9 и устанавливает его в нулевое состояние. Одновременно сигналом с выхода элемента 12 счетчик 4 устанавливается также в нулевое состояние. К этому моменту времени триггер 3 будет на ходиться в нулевом состоянии, так как каждый четный входной импульс перебрасывает его в состояние нуля Таким образом после подсчета К-го входного импульса при четном К дели тель оказывается в исходном состоя нии и с приходом К+1-ГО входного импульса начинается очередной цикл деления-. При нечетном коэффициенте деления в младший разряд счетчика .1 записывается единица и триггер 8 .устанавливается в единичное состояние. Сигналы единичного уровня с выхода младшего разряда счетчика 1 и с выхода триггера 8. поступают на первые входы элементов 11, 14 и 13 В результате этого элемент 11 оказывается открытым, элемент 13 от:крывает элемент 10 в паузах между входными импульсами, а элемент 14 открывает элемент 12, когда Триггер 3 находится в единичном состоянии, т. е,, в интервалах времени между моментами поступления нечетных и четных входных импульсов. Работа делителя при нечетном коэффициенте деления происходит следующим образом. С приходом го входного импульса на выходе дешифратора 5 появляется сигнал, который по окончании этого входного импульса проходит через элемент 10 на второй вход триггера 9 и на счетный вход триггера 7. Оба триггера при этом переходят в единичное состояние. Единичный сигнал с выхода триггера 7 -поступает на вход управления сложением счетчика 1, переводя его в режим сложения. С приходом К-1-го входного импульса на выходе дешифратора 6 появляется сигнал единичного уровня, который поступает на вход элемента 12. Так как К-1-ый входной импульс является четным, то с его приходом триггер 3 устанавливается в нулевое состояние и элемент 12 оказываетс-Я в это время закрытым. С приходом К-го входного импульса триггер 3 переходит в единичное состояние, в результате-чего с инверсного выхода этого триггера на вход элемента. 14 поступает сигнал нулевого уровня. Сигнал единичного уровня, появляющийся при этом на выхо.де элемента 14 открывает элемент 12 р -в результате чего сигнал с выхода дешифратора б проходит на обнуляющий вход счетчика 4, на первый вход триггера 9, устанавливая его в нулевое состояние и через открытый элемент 11 - на вход счетчика 1. Счетчик .4 и триггер У устанавливаются в состояние нули, а в счетчик 1 записывается дополнительный импульс, устанавливая в нем код числа К+1. На этом заканчивается первый -цикл деления на нечетный коэффициент. Таким образом, перед началом второго цикла деления триггер 3 на- ходится-в единичномсостоянии, . что эквивалентно записи в счетчик 2 одного входного импульса, а в счетчике 1 записан код числа, превышающего заданный коэффициент деления на единицу. Число К+1 является чатHIJM., позт- му во втором цикле деления в Jvшaдшeм разряде счетчика 1 записан нуль и на входы дешифраторов 5 и 6 поступает код числа нал нулевого уровня с выхода младшего разряда счетчика 1 поступает на вход элемента 14, в результате чего элемент 12, оказывается открытым. Во втором цикле деления на нечетный коэффициент делитель работает следующим образом. Очередной

--ЫЙ входной импульс устанавливае 4 в. счетчике 2 код числа j- .в результате чего на выходе дешифратора 5 появляется сигнал который п6 окончалии этого входного импульса проходит через элемент 10на вto)pй вход - вход установки триггера 9 в.единичное состояние и на счетный.вход триггера 7. Триггер 9 переходит при этом в единичное состояние, а триггер 7 - в нулевое. Единичный сигнал с выхода триггера поступает на вход управления вычитйнием реверсивного счетчика 1, пфреводяего в режим вычитания. С приходом очередного К-го входного иМпульса в счетчике 2 усаганавливае1гся код числа К+1 и на выходе дедийфратора б появляется сигнал, который проходит через открытый элем нт 12 на шину обнуляющую счетчик 4|, на второй вход - вход установки Bi нулевое состояние триггера 9 и через открытый элемент 11 на вход

счетчика .1. Счетчик 4 и триггер 9 устанавливаются в состояние нуля, а из реверсивного .счетчика 1 вычитается единица, в результате чего в нем устанавливается код заданного коэффициента К. На этом заканчивается второй цикл деления на нечетный коэффициент.

Поскольку очередной К-ый входной импульс, которьм заканчивается второй цикл .деления, на нечетный коэффициент, является чётным, то после прихода этого импульса триггер 3 переходит.в нулевое состояние и, следовательно, схема делителя оказывается в таком же состоянии, как перед началом первого цикла деления ..4

В дальнейшем работа делителя повторяется. .

Введение новых элементов и связей между ними позволяет увеличить быстродействие.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов | 1985 |

|

SU1265996A1 |

| Делитель частоты следования импульсов | 1988 |

|

SU1596453A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU884152A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1547057A2 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

| Делитель частоты импульсов | 1985 |

|

SU1298907A1 |

| Симметричный делитель частоты импульсов | 1982 |

|

SU1089763A2 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1119176A1 |

| Перестраиваемый делитель частоты | 1989 |

|

SU1629991A1 |

| Делитель частоты следования импульсов | 1987 |

|

SU1431069A1 |

ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содержащий счетчик импульсов , счетный вход которого соединен с входной шиной, выходы всех разрядов кроме младшего - с первой группой входов дешифратора кода управления, а выходы всех разрядов, кроме старшего - с первой группой входов дешифратора скважности, -первый элемент И-НЕ, первый вход которого соединен с входной шиной, а выход через первый элемент И со счетным входом первого триггера, о т л и ч аю щ и и с я тем, что, с целью повьиаения быстродействия, в него введены реверсивный счетчик импульсов, второй элемент И, второй триггер и последовательно соединенные второй элемент и-НЕ, третий элемент И и третий триггер, второй вход которого соединен со счетным входом первого триггера, первый и второй выходы которого соединены с входами управления соответственн-о вычитанием и сложением реверсивного счетчика импульсов, прямой выход : младшего разряда которого соединен с входом второго триггера, и первым входом второго элемента И-НЕ, выходил остальных разрядов - с вторыми группами входов дешифратора скважности и дешифратора кода управления, разрядные входы - с шинами кода управления, а счетный вход - с выходом второго элемента И, первый вход которого соединен с выходом второго триггера и вторым входом сл первого элемента И-НЕ, а второй вход - с обнуляющим входом счетчис ка импульсов и выходом третьего элемента И, второй вход которого и второй вход первого элемента .И соединены с выходами соответственно дешифратора кода управления и дешифратора скважности, при этом второй вход второго элемента; И-НЕ соедиИен 4 СП с инверсным выходом младшего разряда счетчика импульсов. Oii

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Делитель частоты | 1974 |

|

SU499674A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU884152A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-09-30—Публикация

1982-03-02—Подача