Изобретение относится к автоматике и вычислительной технике и предназначено для усреднения частоты следования импульсов с представлением результата усреднения в цифровом коде внутри длительного интервала времени и может быть использовано в цифровых системах управления различными объектами и техническими процессами.

Известны устройства для усреднения частоты за фиксированный интервал времени, содержащие реверсивный счетчик, инвертор, генератор тактовых импульсов, вентильные схемы переноса и логические схемы совпадения.

Однако известные устройства имеют невысокое быстродействие и пригодны для усреднения частоты в узком интервале времени.

Для повышения быстродействия, расширения диапазона времени усреднения частоты и упрощения устройства оно дополнительно содержит два триггера, мультивибратор, вычитающий счетчик и реверсивный управляемый делитель, первый вход которого соединен с выходами первой и второй схем совпадения, второй вход соединен с первым входом первой схемы совпадения, с суммирующим входом реверсивного счетчика и с единичным выходом первого триггера, третий вход соединен с вычитающим входом реверсивного счетчика, с первыми входами второй, третьей и четвертой схем совпадения и с нулевым выходом первого триггера, четвертый вход соединен с первым входом вентильной схемы переноса, с выходом пятой схемы совпадения и с нулевыми входами триггеров, а выход соедииен со счетным входом реверсивного счетчика, выход которого соединен со вторым входом вентильной схемы переноса. Выход последней соединен с первым входом вычитающего счетчика, второй вход которого соединен с выходами третьей и четвертой схем совпадения, а выход через щестую схему совпадения соединен с единичным входом первого триггера и с входом инвертора. Выход инвертора соединен с первым входом пятой схемы

совпадения, второй вход которой соединен с выходом генератора тактовых импульсов и единичным входом второго триггера, единичный выход которого соединен со вторыми входами второй и третьей схем совиадения, третий вход второй схемы совпадения соединен с выходом мультивибратора и со вторым входом четвертой схемы совпадения, а третий вход третьей схемы совпадения соединен со вторым входом первой схемы совиадения и

со входом устройства усреднения, причем реверсивный управляемый делитель содержит счетчик коэффициента деления, логическую схему совпадения, схему сравнения кодов, вентильную схему переноса и реверсивный

щий входы которого соединены соответственно с первым, вторым и третьим входами реверсивного управляемого делителя; при этом выход соединен с первыми входами схемы совпадения и вентильной схемы переноса, выход которой соединен со входом переноса реверсивного счетчика, а второй вход соединен с первым выходом счетчика коэффициента деления, вход которого соединен с четвертым входом реверсивного управляемого делителя, а второй выход соединен через схему сравнения кодов со вторым выходом реверсивного счетчика, а выход соединен со входом сброса реверсивного счетчика и со вторым входом схемы сравнения, выход которой соединен с выходом реверсивного управляемого делителя.

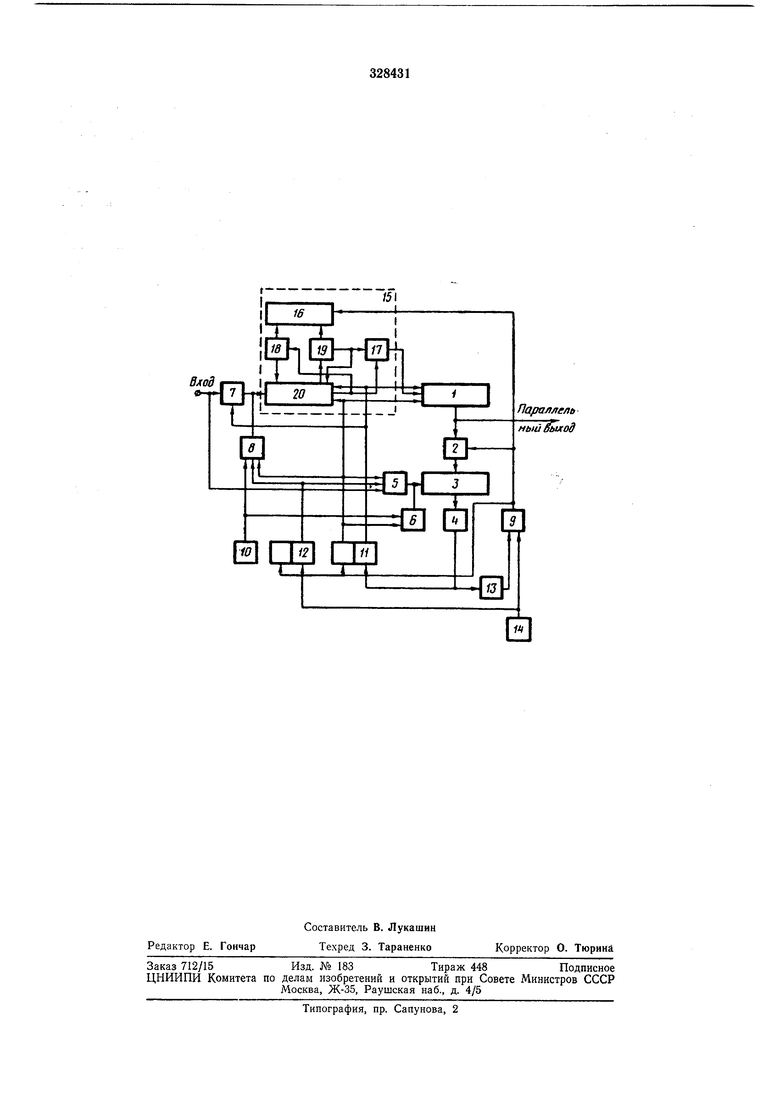

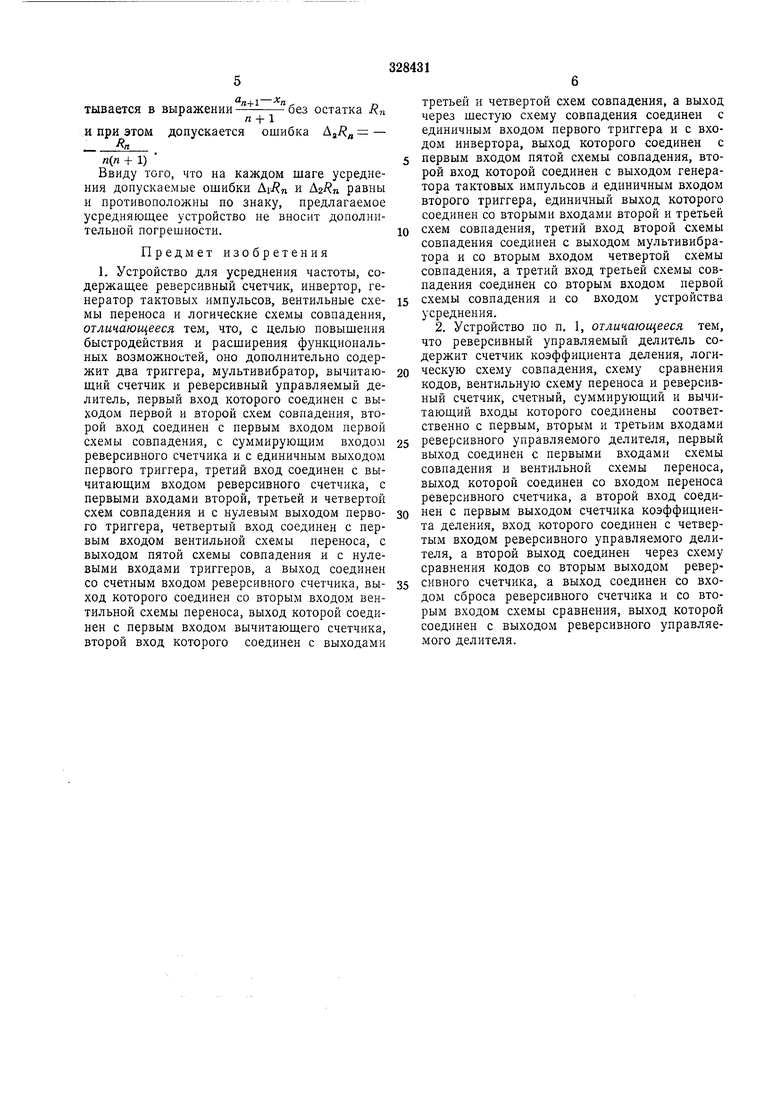

На чертеже представлена блок-схема устройства.

Она содержит реверсивный счетчик (PC) 1, вентильную схему переноса 2, вычитающий счетчик 5, логические схемы совпадения 4, 5, 6, 7, 8, 9, мультивибратор 10, триггеры 11, 12, инвертор 1, генератор тактовых импульсов 14 и реверсивный управляемый делитель 15, содержащий счетчик коэффициента деления (СКД) 16, логическую схему совпадения 17, вентильную схему переноса 18, схему сравнения кодов 19 и реверсивный счетчик (PC) 20.

Устройство работает следующим образом.

На вход устройства поступают импульсы с частотой, пропорциональной усредняемому параметру. Весь интервал времени усреднения разбивают на целое число подинтервалов, которому должна соответствовать емкость СКД. Например, если надо усреднять какойто параметр в течение часа и достаточно иметь информацию о среднем через каждую секунду, емкость СКД должна соответствовать числу 3600, для чего необходимо иметь 12-разрядный двоичный счетчик.

Генератор тактовых импульсов должен генерировать в этом случае последовательность импульсов с частотой следования 1 ги.

Обозначим через Кп - среднее значение усердняемого параметра после /г-ного тактового импульса, записанное в PC 1, Xn+i - среднее значение после я+1 тактового импульса, un+i - среднее значение входной частоты за время и+1 подинтервала, равного длительности периода между тактовыми импульсамк.

Пусть на л+1 также an+i Xn. Передним фронтом тактового импульса состояние PC 1 посредством вентильной схемы 2 переносится в вычитающий счетчик 3, содержимое СКД увеличивается на «единицу, а триггеры устанавливаются в «нулевое состояние, разрешая прохождение входным импульсам на Счетный вход вычитающего счетчика 3 через логическую схему 5. Как только вычитающий счетчик в установится в «нулевое состояние на выходе логической схемы 4 появится импульс, устанавливающий триггер 11 в «единичное состояние. При этом входные импульсы начнут поступать через логическую

схему 7 на счетный вход PC 20, осуществляющий деление на в режиме сложения.

Пусть, например, начальное состояние PC 20 - «нулевое. PC 20 подсчитывает импульсы, поступающие на его вход, и, когда состояние PC представит число «-j-l, соответствующее состоянию СКД, схема сравнения кодов 19 сформирует импульс сброса PC 20 в «нулевое состояние. В режиме сложения импульсы выхода PC 20, переходя через схему 17, поступают па счетпый вход PC /.

Таким образом, после окончания вычисления к началу следующего тактового импульса в PC будет состояние, соответствующее

й„.

-

п +1

Когда ani-i-.Xn входные импульсы, считывая предыдущее среднее зпачение в вычитающем счетчике 3, не успевают полностью за это же время нейтрализовать этот счетчик. Следующий тактовый импульс не пройдет па выход логической схемы 9, вследствие того, что она будет закрыта по входу от инвертора 13, а триггер 12 будет переведен в «единичное состоние. При этом импульсы с выхода мультивибратора, частота следования которых выбирается значительно выще максимальной измеряемой частоты, поступают на

счетные входы вычитающего счетчика 3 через логическую схему 6 и PC 20 через логическую схему и до тех пор, пока вычитающий счетчик не установится в «нулевое состояние. Вычисление в данном случае происходит в режиме

вычитания. Импульс с выхода PC 20 поступает на вентильную схему 18, переносит состояние СКД 16 в PC 20, а так же, через логическую схему 17, поступает на счетный вход PC 1, работающего в этом случае в режиме

вычитания.

Таким образом после окончания вычисления в PC 1 возникнет состояние, соответствующее

х„ - а

л+1

- Хп+

« + 1

Как только вычитающий счетчик 3 станет в «нулевое состояние, срабатывает логическая схема 4, инвертор 13 и на выходе схемы 9 появится импульс, начинающий п+2 такт вычисления.

После п-го шага усреднения состояние PC 20 представляет остаток Rn, который должен

/J

восприниматься как величина - При следующем шаге усреднения остаток воспринимается как величина . Ввиду этого дои +1 пускается ошибка, равная

а„ , 1-л;„

тывается в выражении остатка Rn

л +1

и при этом допускается ошибка - п

п(п + 1)

Ввиду того, что на каждом шаге усреднения допускаемые ошибки и равны и противоположны по знаку, предлагаемое усредняюш,ее устройство не вносит дополнительной погрешности.

Предмет изобретения

1. Устройство для усреднения частоты, содержаш,ее реверсивный счетчик, инвертор, генератор тактовых импульсов, вентильные схемы переноса и логические схемы совпадения, отличающееся тем, что, с целью повышения быстродействия и расширения функциональных возможностей, оно дополнительно содержит два триггера, мультивибратор, вычитающий счетчик и реверсивный управляемый делитель, первый вход которого соединен с выходом первой и второй схем совпадения, второй вход соединен с первым входом первой схемы совпадения, с суммируюш,им входом реверсивного счетчика и с единичным выходом первого триггера, третий вход соединен с вычитающим входом реверсивного счетчика, с первыми входами второй, третьей и четвертой схем совпадения и с нулевым выходом первого триггера, четвертый вход соединен с первым входом вентильной схемы переноса, с выходом пятой схемы совпадения и с нулевыми входами триггеров, а выход соединен со счетным входом реверсивного счетчика, выход которого соединен со вторым входом вентильной схемы переноса, выход которой соединен с первым входом вычитаюшего счетчика, второй вход которого соединен с выходами

третьей и четвертой схем совпадения, а выход через шестую схему совпадения соединен с единичным входом первого триггера и с входом инвертора, выход которого соединен с первым входом пятой схемы совпадения, второй вход которой соединен с выходом генератора тактовых импульсов и единичным входом второго триггера, единичный выход которого соединен со вторыми входами второй и третьей схем совпадения, третий вход второй схемы совпадения соединен с выходом мультивибратора и со вторым входом четвертой схемы совпадения, а третий вход третьей схемы совпадения соединен со вторым входом первой схемы совпадения и со входом устройства усреднения.

2. Устройство по п, 1, отличающееся тем, что реверсивный управляемый делитель содержит счетчик коэффициента деления, логическую схему совпадения, схему сравнения кодов, вентильную схему переноса и реверсивный счетчик, счетный, суммирующий и вычитающий входы которого соединены соответственно с первым, вторым и третьим входами реверсивного управляемого делителя, первый выход соединен с первыми входами схемы совпадения и вентильной схемы переноса, выход которой соединен со входом переноса реверсивного счетчика, а второй вход соединен с первым выходом счетчика коэффициента деления, вход которого соединен с четвертым входом реверсивного управляемого делителя, а второй выход соединен через схему сравнения кодов со вторым выходом реверсивного счетчика, а выход соединен со входом сброса реверсивного счетчика и со вторым входом схемы сравнения, выход которой соединен с выходом реверсивного управляемого делителя.

Влод I-I I

Параллели ныйВыход

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации | 1990 |

|

SU1781835A1 |

| ЦИФРОВОЙ СЛЕДЯЩИЙ КОМПЕНСАТОР | 1967 |

|

SU205138A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU999135A2 |

| Следящий аналого-цифровой преобразователь | 1985 |

|

SU1283971A1 |

| Цифровой генератор качающейся частоты | 1988 |

|

SU1601736A1 |

| Анализатор занятости канала связи | 1984 |

|

SU1225021A1 |

| Способ управления подачей инструмента на электроэрозионном станке с емкостным генератором импульсов и устройство для его осуществления | 1980 |

|

SU1351523A3 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Преобразователь фазового сдвига в цифровой код | 1982 |

|

SU1056073A1 |

| Устройство для управления разгоном и торможением двигателя | 1983 |

|

SU1124252A1 |

Даты

1972-01-01—Публикация