Изобретение относится к области вычислительной техники и предназначается для упрощения конструкции и повышения быстродействия цифровых арифметических устройств.

Известен параллельный накапливающий сумматор, содержащий регистр суммы, регистр второго слагаемого, две линии переноса .на быстродействующих вентилях, а также двухвходовые, трехвходовые и четырехвходовые логичесюие элементы «И. Двухвходовые логические элементы «И, входы которых соединены с выходами одинаковых разрядов регистра суммы и регистра второго слагаемого, соединены с линиями переноса через быстродействующие вентили, а выходы регистра второго слагаемого соединены со входами регистра суммы через двухвходовые элементы .

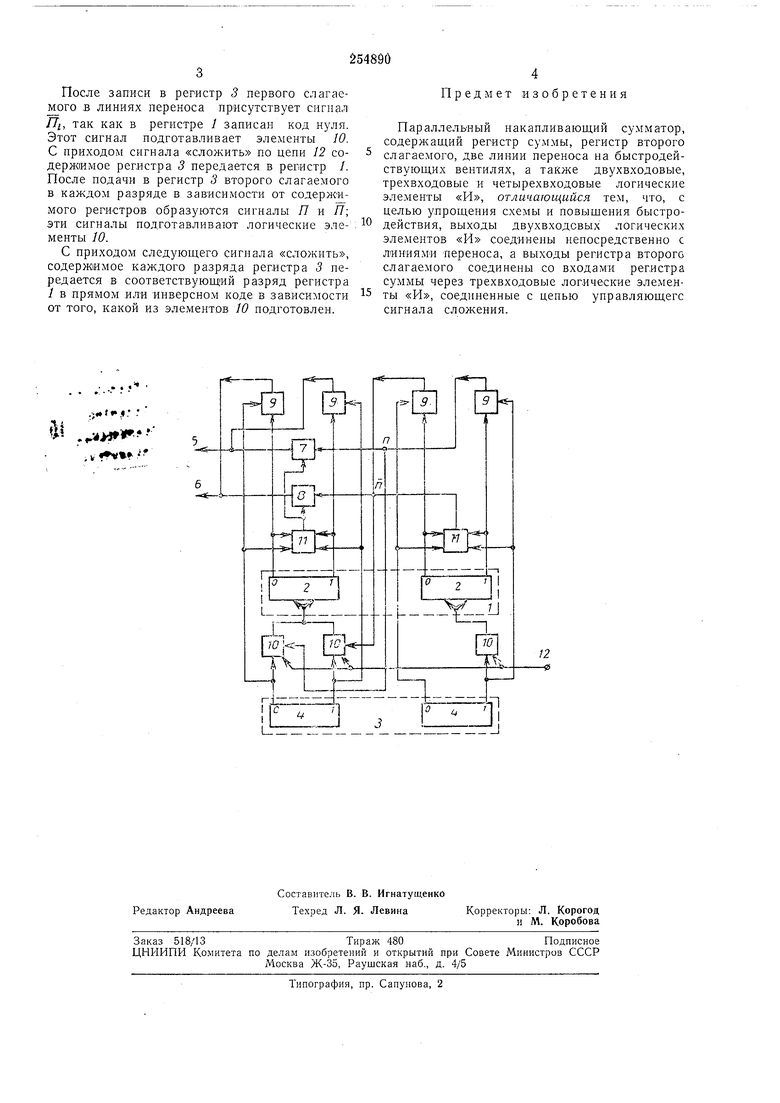

В предложенном сумматоре выходы двухвходовых логических элементов «И соединены непосредственно с линиями переноса, а выходы регистра второго слагаемого - со входами регистра суммы через трехвходовые логические элементы «И, соединенные с цепью управляющего сигнала «сложения.

Это упрощает схему сумматора и повышает его быстродействие (исключается задержка при распространении переноса после прихода сигнала «сложить).

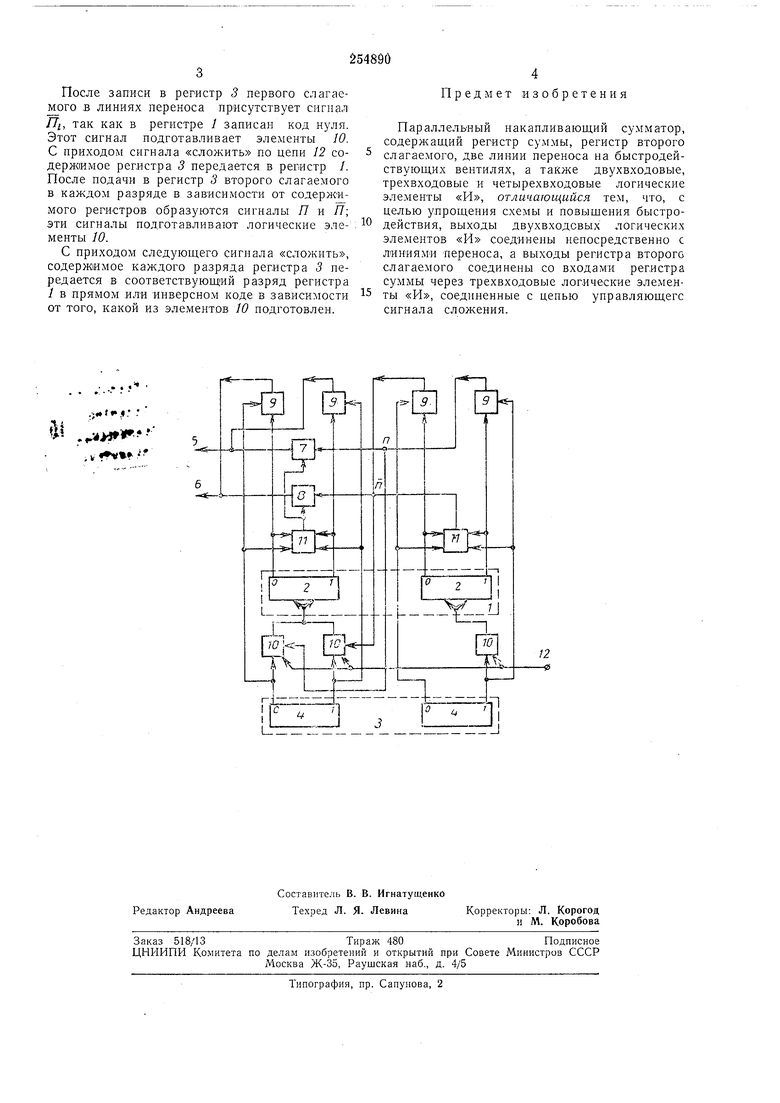

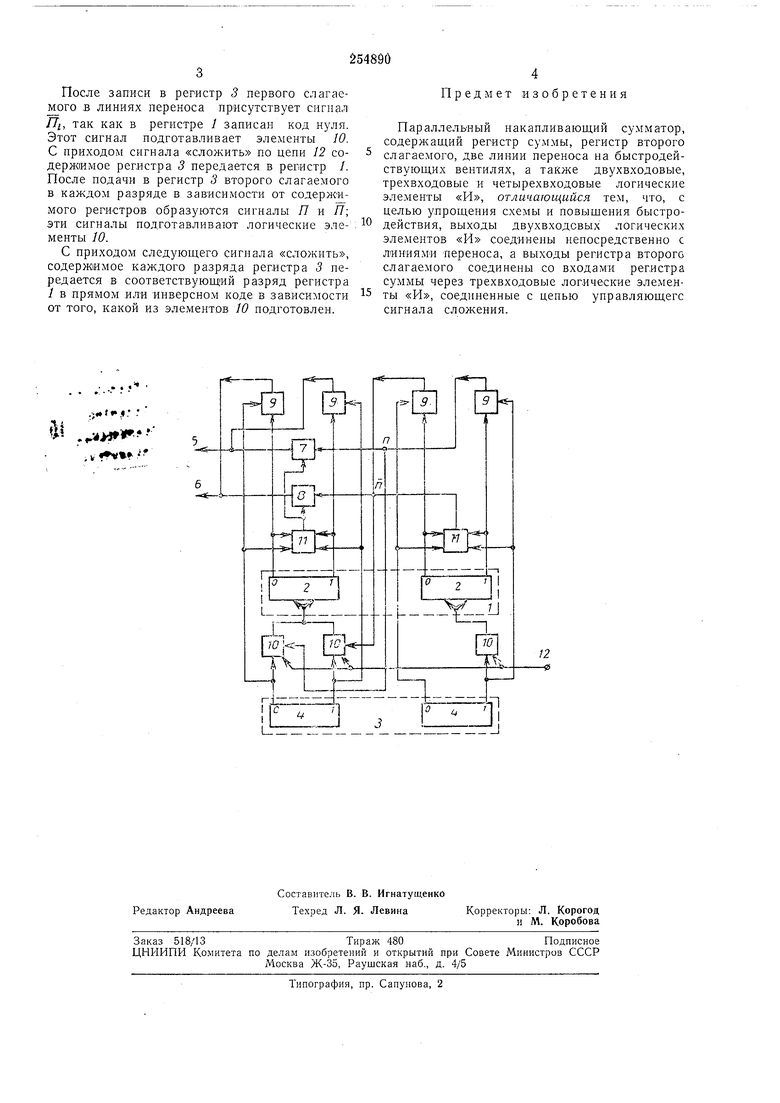

разрядов 2, регистр 3 второго слагаемого с триггерами разрядов 4, линии переноса 5 j-i 6 с быстродействующими вентилями 7 и 8, двухвходовые логические элементы «И 9, трехвходовые логические элементы «И 10, четырехвходовые логические элементы «И 11 и цепь 12 управляющего сигнала «сложить.

Сумматор работает следующим образом.

На выходах логических элементов 9 образуется сигнал:

ni Ai- BI или ni Ai-Bi,

где AI, AI, BI, BI - состояние i-x разрядов регистра суммь1 / и регистра второго слагаемого 5; HI, Д-сигнал переноса и его инверсия из j-ro разряда.

На выходах быстродействующих вентилей 7 ij 8 образуется сигнал /7 C;/7; i или Д; 3 , где Q - сигнал, образованный на выходе логического элемента 11, реализующего следующее логическое выражение:

Q (.

Таким образом, сигналы переноса и его инверсии образуются по следующим логически вырал ениям:

После записи в регистр 3 первого слагаемого в линиях переноса присутствует HI, так как в регистре 1 записан код нуля. Этот сигнал подготавливает элементы 10. С приходом сигнала «сложить по цепи 12 содержимое регистра 3 передается в регистр 1. После подачи в регистр 3 второго слагаемого в каждом разряде в зависимости от содержимого регистров образуются сигналы Я и Я; эти сигналы подготавливают логические элементы 10.

С приходом следующего сиги ал а «сложить, содержимое каждого разряда регистра 3 передается в соответствующий разряд регистра / в прямом или инверсном коде в зависимости от того, какой из элементов 10 подготовлен.

Предмет изобретения

Параллельный накапливающий сумматор, содержащий регистр суммы, регистр второго слагаемого, две линии переноса на быстродействующих вентилях, а также двухвходовые, трехвходовые и четырехвходовые логические элементы «И, отличающийся тем, что, с целью упрощения схемы и повышения быстродействия, выходы двухвходовых логических элементов «И соединены непосредственно с линиями переноса, а выходы регистра второго слагаемого соединены со входами регистра суммы через трехвходовые логические элементы «И, соединенные с цепью управляющегс сигнала сложения.

| название | год | авторы | номер документа |

|---|---|---|---|

| УМНОЖИТЕЛЬ ПО МОДУЛЮ | 2020 |

|

RU2751802C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 1965 |

|

SU169885A1 |

| ПОЛНЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР ПО МОДУЛЮ | 2011 |

|

RU2484519C1 |

| ПОЛНЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР ПО МОДУЛЮ | 2009 |

|

RU2427027C1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| ЛОГИЧЕСКИЙ БЛОК АРИФМЕТИЧЕСКОГО УСТРОЙСТВА | 1969 |

|

SU241108A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Арифметико-логическое устройство для сложения и вычитания чисел по модулю | 2017 |

|

RU2639645C1 |

й . ,v г7Ъ

Даты

1969-01-01—Публикация