Предлагаемый логический блок, предназначенный для выполнения логических операций над «-разрядными кодами, может найти применение в арифметических устройствах АУ цифровых вычислительных машин ЦВМ.

Известные арифметические устройства содержат входной и промежуточный регистры, два регистра сумм, два регистра переносов, двухвходовой и трехвходовой суммирующие элементы, регистр операций, усилители, управляющие диодными суммирующими элементами и вентилями передачи содержимого входного регистра на промел уточный. Эта часть АУ выполняет арифметические и логические операции. Однако время выполнения логических операций в известных устройствах велико, что уменьщает быстродействие ЦВМ.

Кроме того, сложность алгоритма усложняет ц логические связи цепей управления логическими операциями.

Цель предлагаемого изобретения - повысить быстродействие и расщирить функциональные возможности устройства, упростив логические связи и уменьщив оборудование той части АУ, которая выполняет логические операции.

одного из регистров переносов. Единичные выходы промежуточного регистра и одного из регистров сумм каждого разряда, а также единичный выход другого парафазного усилителя через вентиль подключены ко входу соответствующего разряда второго регистра сумм. Единичный выход усилителя, управляющего сдвигом влево, через вентиль подключен ко входу усилителей, выходы которых связаны с вентилями выдачи прямым и обратным кодом, а нулевой выход его и единичные выходы последних через вентиль подключены к усилителю, нулевой выход которого связан с вентилями переносов суммирующего элемента.

Связь диодного суммирующего элемента с управляющими усилителями заключается в том, что входы вентилей сумм этого элемента, не соединенные с единичным выходом второго регистра суммы РС2, дополнительно подключены к усилителю, запрещающему работу указанных вентилей при операции логического умножения.

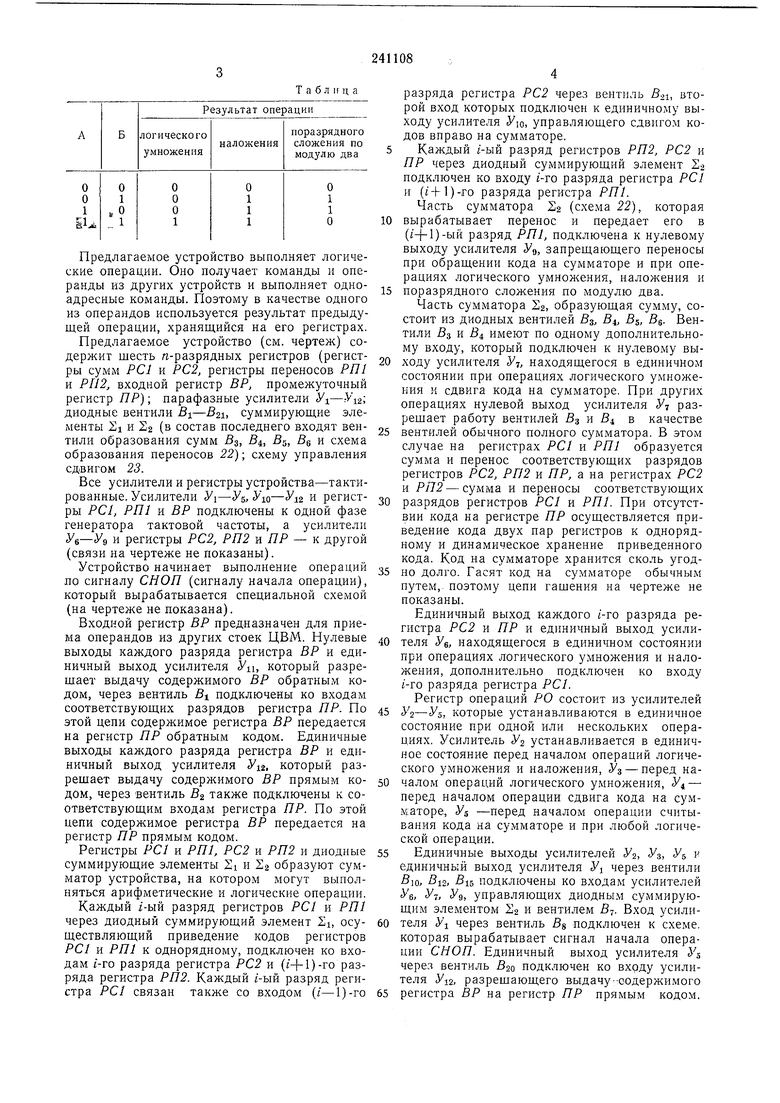

Эта связь и новый вентиль обеспечивают выполнение диодным суммирующим элементом фЗнкций полного сумматора и так называемого логического сумматора, работа которого иллюстрируется таблицей, где представлены задаваемые коды Л и Б и результаты логических операций.

Т а б л IF ц а

Предлагаемое устройство выполняет логические операции. Оно получает команды и операнды из других устройств и выполняет одноадресные команды. Поэтому в качестве одного из операндов используется результат предыдущей операции, хранящийся на его регистрах.

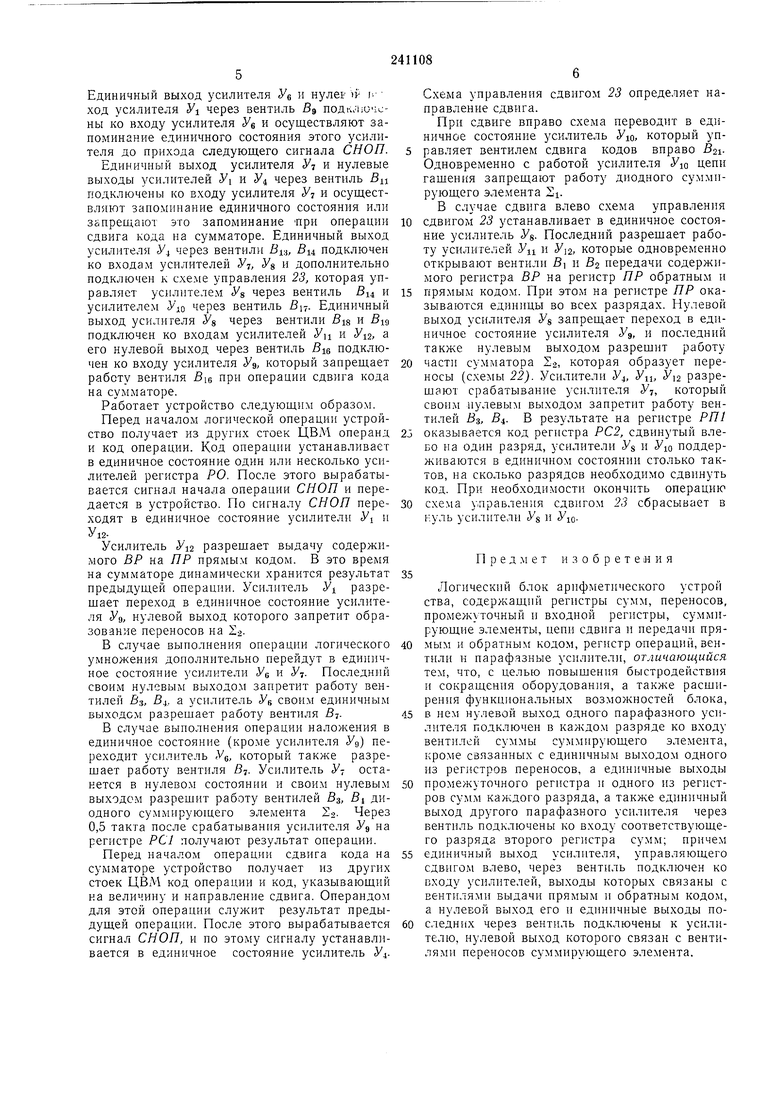

Предлагаемое устройство (см. чертеж) содержит щесть «-разрядных регистров (регистры сумм РС1 и РС2, регистры переносов РП1 и РП2, входной регистр ВР, промежуточный регистр ПР); парафазные усилители диодные вентили , суммирующие элементы 2i и 2 (в состав последнего входят вентили образования сумм БЗ, В, В, BQ и схема образования переносов 22); схему управления сдвигом 23.

Все усилители и регистры устройства-тактированные. Усилители , и регистры РС1, РП1 и ВР подключены к одной фазе генератора тактовой частоты, а усилители Уб-Ув и регистры РС2, РП2 и ЯР - к другой (связи на чертеже не показаны).

Устройство начинает выполнение операций по сигналу СНОП (сигналу начала операции), который вырабатывается специальной схемой (на чертеже не показана).

Входной регистр ВР предназначен для приема операндов из других стоек ЦВМ. Нулевые выходы каждого разряда регистра ВР и единичный выход усилителя Уц, который разрешает выдачу содержимого ВР обратным кодом, через вентиль BI подключены ко входам соответствующих разрядов регистра ПР. По этой цепи содержимое регистра ВР передается на регистр ПР обратным кодом. Единичные выходы каждого разряда регистра ВР и единичный выход усилителя У12, который разрещает выдачу содержимого ВР прямым кодом, через вентиль В также подключены к соответствующим входам регистра ПР. По этой цепи содержимое регистра ВР передается на регистр ПР прямым кодом.

Регистры РС1 и РП1, РС2 и РП2 и диодные суммирующие элементы Zj и Sg образуют сумматор устройства, на котором могут выполняться арифметические и логические операции.

Каждый i-ый разряд регистров РС1 и РП1 через диодный суммирующий элемент 1, осуществляющий приведение кодов регистров РС1 и РП1 к однорядному, подключен ко входам г-го разряда регистра РС2 и (li+l)-го разряда регистра РП2. Каждый i-ът разряд регистра РС1 связан также со входом (i-1)-го

разряда регистра РС2 через вентиль i, второй вход которых подключен к единично.му выходу усилителя УЮ, управляющего сдвигом кодов вправо на сумматоре.

Каждый г-ый разряд регистров РП2, РС2 и

ПР через диодный суммирующий элемент 22

подключен ко входу г-го разряда регистра РС1

и (f+l)-ro разряда регистра РП}.

Часть сумматора На (схема 22), которая

вырабатывает перенос и передает его в (г4-1)-ьш разряд РП}, подключена к нулевому выходу усилителя УО, запрещающего переносы при обращении кода на сумматоре и при операциях логического умножения, наложения и

поразрядного сложения по модулю два.

Часть сумматора Sa, образующая сумму, состоит из диодных вентилей BS, BI, BS, В. Вентили Вз и В имеют по одному дополнительному входу, который подключен к нулевому выходу усилителя Уу, находящегося в единичном состоянии при операциях логического умножения и сдвига кода на сумматоре. При других операциях нулевой выход усилителя Уу разрещает работу вентилей Вз и В в качестве

вентилей обычного полного сумматора. В этом случае на регистрах PCI и РП1 образуется сумма и перенос соответствующих разрядов регистров РС2, РП2 и ПР, а на регистрах РС2 и РП2 - сумма и переносы соответствующих

разрядов регистров РС1 и РП1. При отсутствии кода на регистре ПР осуществляется приведение кода двух пар регистров к однорядному и динамическое хранение приведенного кода. Код на сумматоре хранится сколь угодно долго. Гасят код на сумматоре обычным путем, поэтому цепи гащения на чертеже не показаны.

Единичный выход каждого г-го разряда регистра РС2 и ПР и единичный выход усилителя Уб, находящегося в единичном состоянии при операциях логического умножения и наложения, дополнительно подключен ко входу /-ГО разряда регистра PCL Регистр операций РО состоит из усилителей

У2-УЗ, которые устанавливаются в единичное состояние при одной или нескольких операциях. Усилитель У2 устанавливается в единичное состояние перед началом операций логического умножения и наложения, УЗ - перед началом операций логического умножения, У - перед началом операции сдвига кода на сумматоре, УЗ -перед началом операции считывания кода на сумматоре и при любой логической операции.

Единичные выходы усилителей У, УЗ, Уб v единичный выход усилителя У через вентили 10, 12, fii5 подключены ко входам усилителей Уб, УТ, Уд, управляющих диодным суммирующим элементом Sa и вентилем Вт. Вход усилителя У через вентиль Bg подключен к схеме, которая вырабатывает сигнал начала операции СНОП. Единичный выход усилителя УЗ через вентиль В подключен ко входу усилителя У12, разрешающего выдачу-содержимого

Единичный выход усилителя Ув и нулеь- IF i-- ход усилителя У через вентиль В иодк иочсны ко входу усилителя Уе и осуществляют запоминание единичиого состояния этого усилителя до прихода следующего сигнала СНОП.

Единичный выход усилителя УТ и нулевые выходы усилителей У и У через вентиль Вц подключеиы ко входу усилителя У и осуществляют запоминание единичного состояния или запрещают это запоминание при операпии сдвига кода на сумматоре. Единичный выход усилителя У4 через вентили , В-ц подключен ко входам усилителей УТ, У% и дополнительно подключен к схеме управления 23, которая управляет усилителем УЗ через вентиль Bi4 и усилителем Ую через вентиль БП. Единичный выход усилителя УЗ через вентили 3 и 5ig подключен ко входам усилителей УН и У12, а его нулевой выход через вентиль Big подключен ко входу усилителя Уд, который запрещает работу вентиля BIG при операпии сдвига кода на сумматоре.

Работает устройство следующим образом.

Перед началом логической операции устройство получает из других стоек ЦВМ операнд и код операции. Код операции устанавливает в единичное состояние один или несколько усилителей регистра РО. После этого вырабатывается сигнал начала операции СНОП и передается в устройство. По сигналу СНОП переходят в единичное состояние усилители У и

У12.

Усилитель У12 разрешает выдачу содержимого ВР на ПР прямым кодом. В это время на сумматоре динамически хранится результат предыдущей операции. Усилитель У разрешает переход в единичное состояние усилителя УЭ, нулевой выход которого запретит образование переносов на Zg.

В случае выполнения операции логического умножения дополнительно перейдут в единичное состояние усилители УС и У. Последний своим нулевым выходом запретит работу вентилей B,t, В4, а усилитель УВ своим единичным выходом разрешает работу вентиля B.

В случае выполнения операции наложения в единичное состояние (кроме усилителя Уд) переходит усилитель УО, который также разрешает работу вентиля BV. Усилитель УТ останется в нулевом состоянии и своим нулевым выходом разрешит работу вентилей Вз, В, диодного суммирующего элемента Sg. Через 0,5 такта после срабатывания усилителя Уд на регистре РС1 получают результат операции.

Перед началом операции сдвига кода на сум.маторе устройство получает из других стоек ЦВМ код операции и код, указывающий на величииу и направление сдвига. Операндом для этой операции служит результат предыдущей операции. После этого вырабатывается сигнал СНОП, и по этому сигналу устанавливается в единичное состояние усилитель У4.

Схема управления сдвигом 23 определяет направление сдвига.

При сдвиге вправо схема переводит в единичное состояние усилитель УЮ, который управляет вентилем сдвига кодов вправо .821. Одновременно с работой усилителя УЮ цепи гашения запрещают работу диодного суммирующего элемента 2i. В случае сдвига влево схема управления

сдвигом 23 устанавливает в единичное состояние усилитель УВ. Последний разрешает работу усилителей Уц и У, которые одновременно открывают вентили В, и В2 передачи содержимого регистра ВР на регистр ПР обратным и

прямым кодом. При этом на регистре ПР оказываются едии1щы во всех разрядах. Пулевой выход усилителя УЗ запрещает переход в единичное состояние усилителя Уд, и последний также нулевым выходом разрешит работу

части су.мматора Ео, которая образует иереносы (схемы 22). Усилители У4, Уц, У12 разрешают срабатывание усилителя У, который своим пулевьт выходом запретит работу вентилей Вз, В4. В результате на регистре РП1

оказывается код регистра РС2, сдвинутый влево на один разряд, усилители У и УЮ поддерживаются в единичном состоянии столько тактов, на сколько разрядов необходимо сдвинуть код. При необходимости окончить операцию

схема управления сдвигом 23 сбрасывает в нуль усилители УЗ и УЮ.

П р е д .м е Т изобретения

35

Логический блок арифметического устрой ства, содержащий регистры сумм, переносов, промежуточный и входной регистры, суммирующие элементы, цепи сдвига и передачи прямым и обратным кодом, регистр операций, вентили и парафазные усилители, отличающийся тем, что, с целью повышения быстродействия и сокращения оборудования, а также расширения функциональных возможностей блока,

в нем нулевой выход одного парафазного усилителя подключен в каждо.м разряде ко входу вентилей суммы суммирующего элемента, кроме связаиных с единичным выходом одного из регистров переносов, а единичные выходы

промежуточного регистра и одного из регистров сумм каждого разряда, а также единичный вы.ход другого парафазного усилителя через вентиль подключены ко входу соответствующего разряда второго регистра сумм; причем

единичный выход усилителя, управляющего сдвигом влево, через вентиль подключен ко входу усилителей, вы.ходы которых связаны с вентилями выдачи прямым и обратным кодом, а нулевой выход его и единичные вы.ходы последних через вентиль подключены к усилителю, нулевой вы.ход которого связан с вентилями переносов суммирующего элемента.

I РП2

PC2

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| Устройство измерения длительности импульсных сигналов | 1986 |

|

SU1476405A1 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

| Электропривод постоянного тока | 1983 |

|

SU1100697A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СТАТИСТИЧЕСКИХ ДАННЫХ | 1970 |

|

SU272674A1 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| СОЛНЕЧНАЯ ЭЛЕКТРОСТАНЦИЯ | 2002 |

|

RU2230395C1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

Даты

1969-01-01—Публикация