t ,

Изобретение относится к вычислительной технике, и может быть использовано для быстрого преобразования целых десятичных чисел в двоичные.

Цель изобретения - повьшение быст родействия.

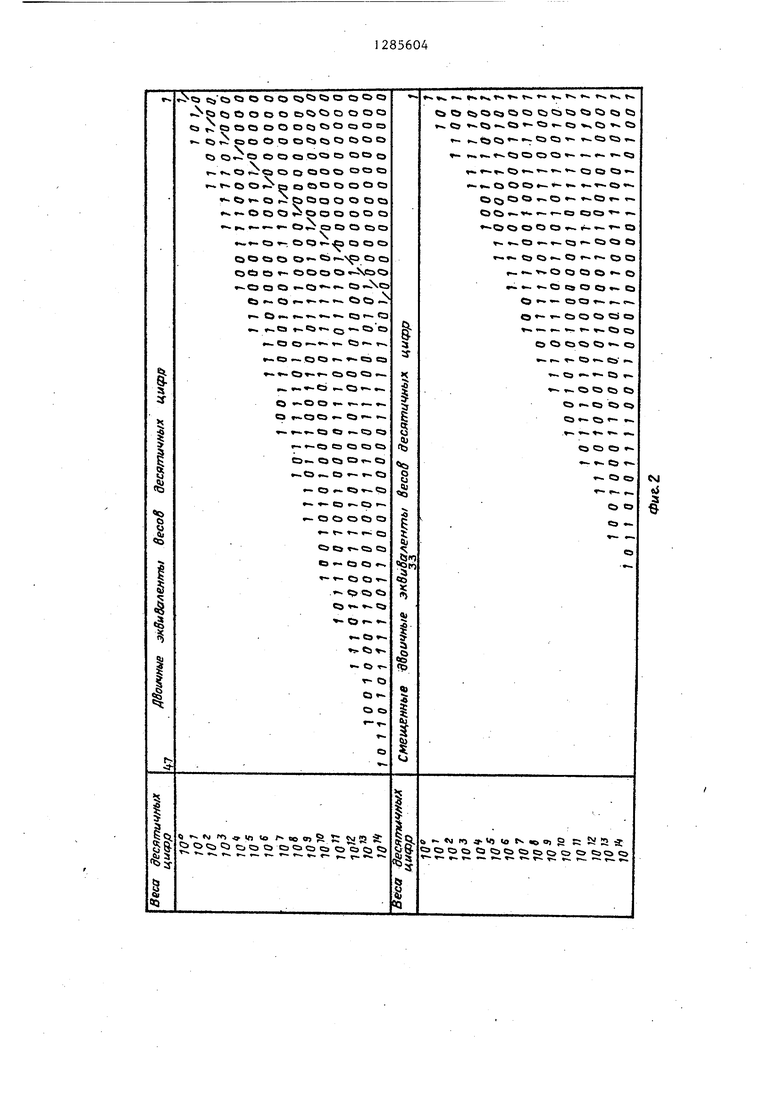

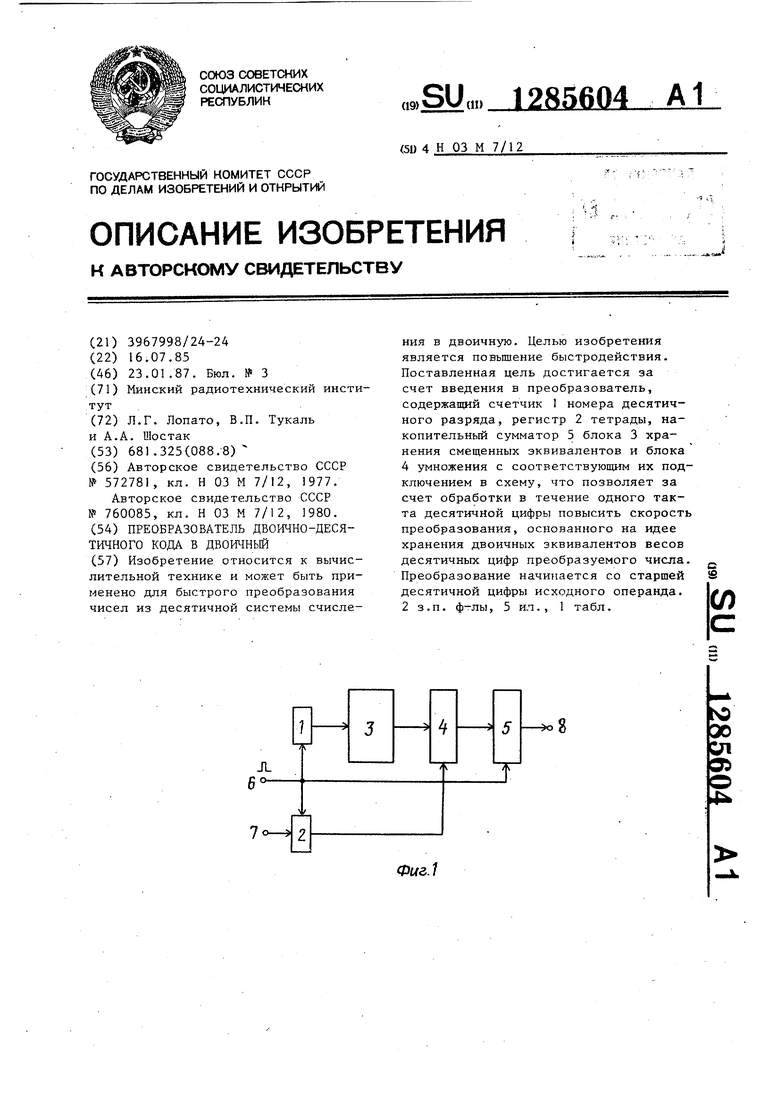

На фиг. 1 приведена структурная схема преобразователя двоично-десятичного кода в двоичный; на фиг. 2 - .таблица для m 15, где представлены значения двоичных эквивалентов весов десятичных цифр без смещения и со смещением; на фиг. 3 - диаграмма, поясняющая организацию вычислений в блоке умножения; на фиг. 4 - структурная схема блока умножения; на фиг. 5 - схема накопительного сумматора.

Преобразователь двоично-десятичного кода в двоичный содержит (фиг. счетчик 1 номера десятичного разряда, рег истр 2 тетрады, блок 3 хране- ш-iff смещенных эквивалентов, блок 4 умножения, накопительный сумматор 5, тактовый вход 6, информационный вход 7 и выход 8.

Блок умножения (фиг. 4) содержит тетрадный преобразователь 9 кода 8-4-2-1 в код 8-4-2-1-1 , блок 10 вы числения произведения, первую 11 и вторую 12 группы элементов ИЛИ.

Накопительный сумматор (фиг. 5) содержит двухвходовой сумматор 13, регистр 14 и трехвходовой сумматор 1

Блок хранения смещенных эквивалентов может быть выполнен на . ПЗУ и содержит смещенные двоичные эвиваленты чисел вида 10 (i - целое положительное число, причем Ой1бт-1 где m - разрядность исходного тичного операнда) .

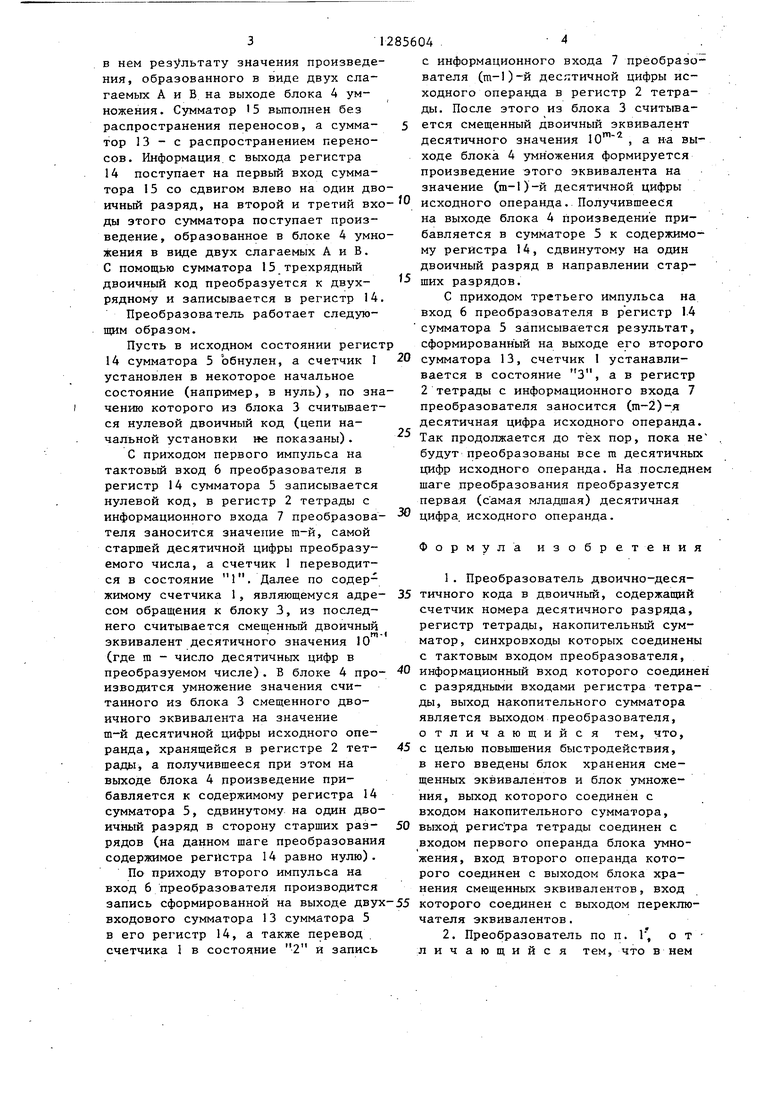

На фиг. 2 приведены значения двоичных эквивалентов десятичных значений 10 (), причем в верхней части таблицы эти зна.чения даны без смещения (как в известном преобразователе) , а в нижней части таблицы - со смещением (как в предлагаемом пробразователе) на i двоичных разрядов вправо. Принципиально такое смещение двоичных эквивалентов десятичных значений 10 возможно, так как в них i младших двоичных разрядов являются нулевыми (в верхней части таблицы (фиг. 2) область нулей отмечена штриховой линией). Сопоставляя эти два массива двоичных эквивалентов, видно, что для хранения несме

щенных эквивалентов требуется память на 47 двоичных разрядов, в то время как для хранения смещенных эквивалентов требуется память на 33 двоичных разряда.

Учитывая, что некоторые разряды двоичных эквивалентов содержат только нули или единицы, окончательно получим, что блок хранения несмещенных эквивалентов должен иметь 45 двоичных разрядов, в то время как блок хранения смещенньщ эквивалентов 29-разрядный, т.е. примерно в 1,6 раза имеет меньшую разрядность.

В блоке 4 в каждом такте работы преобразователя осуществляется умножение значения очередной десятичной цифры исходного операнда, хранимой в регистре 2 тетрады и поступающей на первый вход блока 4 умножения, на значение двоичного эквивалента ее десятичного веса, считываемого из блока 3 на второй вход блока 4 умножения. Этот блок может быть разработан любым из известных методов умножения двоичных чисел. С целью сокращения количества оборудования блока 4 и увеличения быстродействия преобразователя предлагается следующее его построение.

Десятичная цифра исходного операнда, хранимая в регистре 2 тетрады и поступающая на первый вход блока-4 умножения, предварительно преобразуется в нем из кода 8-4-2-1 в код 8-4-2-1-1. Это преобразование выполняется параллельно с работой блока 3 и поэтому не снижает быстродействие блока 4 умножения.

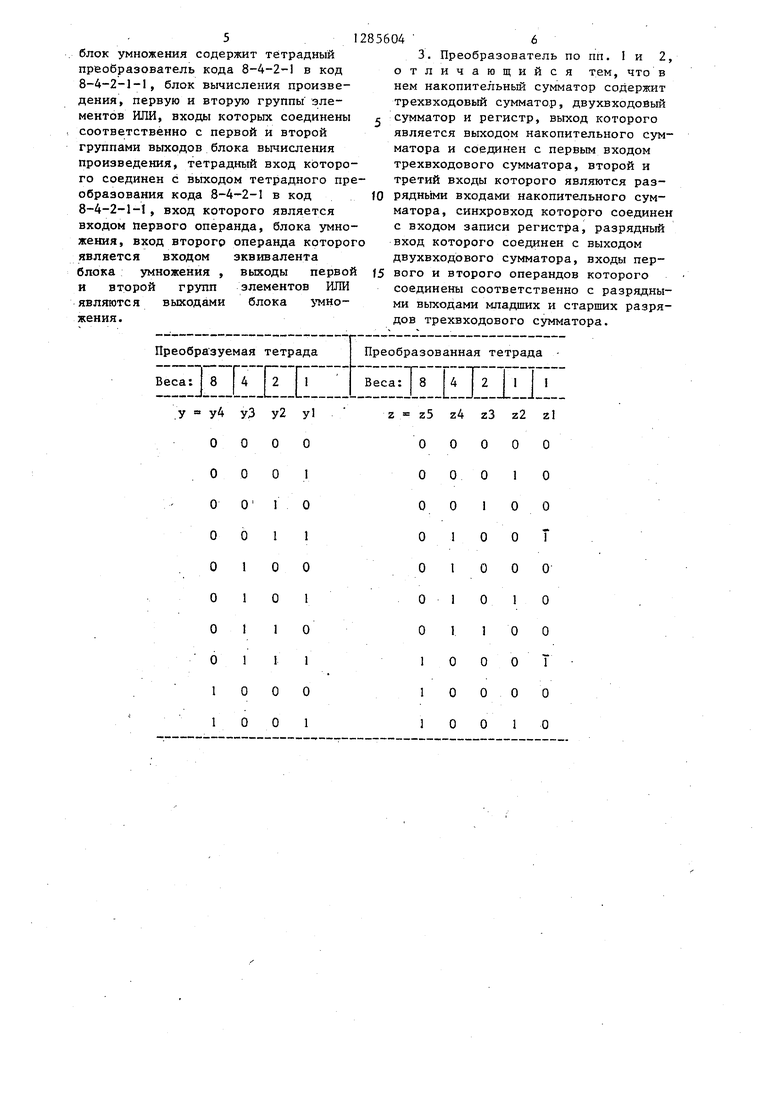

Это преобразование поясняется в таблице.

Из таблицы видно, что цифры zl, z2 и z3 преобразованной тетрады одновременно не могут быть значащими. Это же справедливо и в отнощении цифр z4, z5 преобразованной тетрады. Приведем логические вьфажения, по которым могут быть получены значения цифр преобразованной тетрады:

zl у1.у2; :

z2 у1.у2;

z3 уЬ у2;

z4 уЗ%1-у2;

z5 у4+у1.у2.уЗ..

В каждом такте работы преобразователя- в сумматоре 5 осуществляется прибавление к ранее накопленному

в нем результату значения произведения, образованного в виде двух слагаемых А и В на выходе блока 4 умножения. Сумматор 15 вьтолнен без распространения переносов, а сумма- тор 13 - с распространением переносов. Информация, с выхода регистра 14 поступает на первый вход сумматора 15 со сдвигом влево на один двоичный разряд, на второй и третий вхо ды этого сумматора поступает произведение, образованное в блоке 4 умножения в виде двух слагаемых А и В. С помощью сумматора 15 трехрядный двоичный код преобразуется к двух- рядному и записывается в регистр 14

Преобразователь работает следующим образом.

Пусть в исходном состоянии регист 14 сумматора 5 обнулен, а счетчик 1 установлен в некоторое начальное состояние (например, в нуль), по значению которого из блока 3 считывается нулевой двоичный код (цепи начальной установки не показаны).

С приходом первого импульса на тактовый вход 6 преобразователя в регистр 14 сумматора 5 записывается нулевой код, в регистр 2 тетрады с информационного входа 7 преобразова- теля заносится значение т-й, самой старшей десятичной цифры преобразуемого числа, а счетчик 1 переводится в состояние 1, Далее по содержимому счетчика 1, являющемуся адре- сом обращения к блоку 3, из последнего считывается смещенный двоичный

.тэквивалент десятичного значения 10

(где га - число десятичных цифр в преобразуемом числе). В блоке 4 про- изводится умножение значения считанного из блока 3 смещенного двоичного эквивалента на значение т-й десятичной цифры исходного операнда, хранящейся в регистре 2 тет- рады, а получившееся при этом на выходе блока 4 произведение прибавляется к содержимому регистра 14 сумматора 5, сдвинутому на один двоичный разряд в сторону старших раз- рядов (на данном щаге преобразования содержимое регистра 14 равно нулю).

По приходу второго импульса на вход 6 преобразователя производится запись сформированной на выходе двух входового сумматора 13 сумматора 5 в его регистр 14, а также перевод . счетчика 1 в состояние 2 и запись

5

5

0

5

5 0

5

с информационного входа 7 преобразователя (т-1)-й деся;тичной цифры исходного операнда в регистр 2 тетрады. После этого из блока 3 считывается смещенный двоичный эквивалент десятичного значения , а н-а выходе блока 4 умн ожения формируется произведение этого эквивалента на значение (т-1)-й десятичной цифры исходного операнда. Получившееся на выходе блока 4 произведение прибавляется в сумматоре 5 к содержимому регистра 14, сдвинутому на один двоичный разряд в направлении старших разрядов.

С приходом третьего импульса на вход 6 преобразователя в регистр 1.4 сумматора 5 записывается результат, сформированный на выходе его второго сумматора 13, счетчик 1 устанавливается в состояние 3, а в регистр 2 тетрады с информационного входа 7 преобразователя заносится (т-2)-я десятичная цифра исходного операнда. Так продолжается до тех пор, пока не будут преобразованы все га десятичных цифр исходного операнда. На последнем шаге преобразования преобразуется первая (самая младшая) десятичная цифра, исходного операнда.

Формула изобретения

1.Преобразователь двоично-десятичного кода в двоичный, содержащий счетчик номера десятичного разряда, регистр тетрады, накопительный сумматор, синхровходы которых соединены с тактовым входом преобразователя, информационный вход которого соединен с разрядными входами регистра тетрады, выход накопительного сумматора является выходом преобразователя, отличающийся тем, что,

с целью повьштения быстродействия, в него введены блок хранения смещенных эквивалентов и блок умножения, выход которого соединен с входом накопительного сумматора, выход регис тра тетрады соединен с входом первого операнда блока умножения, вход второго операнда которого соединен с выходом блока хранения смещенных эквивалентов, вход которого соединен с выходом переключателя эквивалентов.

2.Преобразователь по п. Г , отличающийся тем, что в нем

блок умножения содержит тетрадный преобразователь кода 8-4-2-1 в код 8-4-2-1-1, блок вычисления произведения, первую и вторую группы элементов ИЛИ, входы которых соединены соответственно с первой и второй группами выходов блока вычисления произведения, тетрадный вход которого соединен с выходом тетрадного преобразования кода 8-4-2-1 в код 8-4-2-1-1, вход которого является входом первого операнда, блока жения, вход второго операнда которог является входом блока умножения , и второй групп являются выходами жения.

эквивалента выходы первой элементов ИЛИ блока i MHo000

00 О I О 1 1 О

1

О 1

0101

о о

1 1 1 1

о 1

1000

1 о о

5

3. Преобразователь по пп. 1 и 2, отличающийся тем, что в нем накопительный сумматор содержит трехвходовый сумматор, двухвходойый сумматор и регистр, выход которого является выходом накопительного сумматора и соединен с первым входом трехвходового сумматора, второй и третий входы которого являются раз- ряднь1ми входами накопительного сумматора, синхровход которого соединен с входом записи регистра, разрядный вход которого соединен с выходом двухвходового сумматора, входы первого и второго операндов которого соединены соответственно с разрядными выходами младших и старших разрядов трехвходового сумматора.

О О

О

000 1 О 00100

о

I о о

01000

о о

о 1

1 о о

1000

о о

00 о

о 1

Cvj fti

V W

pj Xp 7j Vf7j JT r fl-j-Zj

. J

/ г

/oj

PI

PS X

П

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

Изобретение относится к вычислительной технике и может быть применено для быстрого преобразования чисел из десятичной системы счисления в двоичную. Целью изобретения является повышение быстродействия. Поставленная цель достигается за счет введения в преобразователь, содержащий счетчик 1 номера десятичного разряда, регистр 2 тетрады, накопительный сумматор 5 блока 3 хранения смещенных эквивалентов и блока 4 умножения с соответствующим их подключением в схему, что позволяет за счет обработки в течение одного такта десятичной цифры повысить скорость преобразования, основанного на идее хранения двоичных эквивалентов весов десятичных цифр преобразуемого числа. Преобразование начинается со старшей десятичной цифры исходного операнда, 2 з.п. ф-лы, 5 ил., 1 табл. с S (Л Фиг.

H

. Л

Редактор H. Тупица

Хя

Фиг.5

Составитель М. Аршавский

Техред Л.Олейник Корректор Т. Колб

Заказ. 7535/57 Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035,а Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Преобразователь двоично-десятичных чисел в двоичные | 1976 |

|

SU572781A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 760085, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-23—Публикация

1985-07-16—Подача